具有失调抑制能力的低功耗带隙基准电路

2022-05-25王纪鹏

王纪鹏

(福州大学 物理与信息工程学院,福建 福州 350108)

0 引 言

目前,带隙基准电压源被广泛应用于直流-直流(DC-DC)变换器、模数转换器(ADC)、数模转换器(DAC)等模拟电路中[1-2]。这些应用通常要求带隙基准电压源应当具有良好的精度和鲁棒性,不随工艺、电源电压以及温度的变化而变化。

误差放大器的输入失调电压是造成带隙基准电压源精度下降的重要因素。传统失调消除主要分为自归零[3]和斩波[4]两种方法,其中自归零技术往往存在时钟馈通和电荷注入等副作用,而斩波技术需要额外增加滤波器和振荡器等电路。基于此,本文提出了一种新型带隙基准电压电路结构,首先对误差放大器失调电压的影响进行理论分析,其次验证该结构具有较好的失调电压抑制能力,最后基于理论分析结果设计具有结构简单、低失调电压以及低功耗等优点的带隙基准电路。

1 新型带隙基准电路分析与设计

本文所提出的具有失调电压抑制功能的带隙基准电压源电路如图1所示,主要包括带隙基准电压源、误差放大器以及启动电路3部分。

图1 整体电路结构

传统的电压模型带隙基准电路如图2(a)所示,主要由误差放大器、三极管及电阻网络构成。其等效电路如图2(b)所示,图中UOS,EA为误差放大器的输入失调电压,RQ1和RQ2分别为三极管Q1和Q2的等效阻抗。

图2 传统模型

假设由于失调电压UOS,EA造成输出参考电压UBG变化的变化量为∆UBG,则通过电阻R1、R2、RQ1、RQ2在A点和B点造成的变化量分别为∆UA和∆UB。若误差放大器的增益为Av,则由失调电压UOS,EA引起的影响因子为:

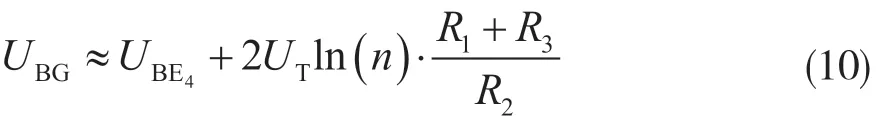

由式(1)可知,当误差放大器增益Av足够大且RQ< 新型的带隙基准源电路及其等效电路如图3(a) 和图3(b)所示,为方便分析将电阻R2和三极管Q3、Q4等效为电阻REQ。 图3 新型模型 假设三极管Q3和Q4的电流放大倍数分别为β1和β2,两者的面积之比为n∶1,则对图3(a)进行直流电流分析可得晶体管等效跨导gm3和gm4分别为: 假设失调电压UOS,EA在A点、B点和C点所引起的变化量为∆UA、∆UB和∆UC,在C点处的电流变化量为∆IC,则等效电阻值REQ和新型带隙基准电路的影响因子ξ2为: 本文设计的新型带隙基准电路中三极管Q3和Q4的面积之比为8∶1,R1和R2约为5.5 MΩ和1 MΩ,影响因子ξ1和ξ2随误差放大器增益Av的变化情况如图4所示。 图4 影响因子随增益变化 由图4可知,在误差放大器增益相同时,新型带隙基准电路的影响因子远小于传统带隙基准,可以降低对误差放大器增益与失调电压的要求,从而可以减小电路功耗和芯片面积。 三极管Q3和Q4的面积之比n和电流放大倍数β对影响因子ξ2的影响如图5(a)所示,对REQ的影响如图5(b)所示。 由图5(a)可知,当n和β增加时,ξ2将减小。由图5(b)可知,当β大于一定数值且n大于7时,REQ为负值,此时对系统的稳定性要求较高。综合考虑系统影响因子、稳定性和器件匹配等因素,由电阻RC和电容CC构成Type II型补偿电路,有效防止REQ造成系统不稳定。 图5 面积比n对ξ2和REQ的影响 基于新型带隙基准电路所构成的参考电压电路如图6所示,其基本原理是将正温度系数的电压和负温度系数的电压相叠加,从而得到与温度无关的带隙基准电压[6]。 图6 带隙基准参考电压电路 带隙基准参考电压源主体电路由三级管Q3、Q4和电阻R1、R3组成,误差放大器电路由Q1、Q2、M1、M2、M3、M4以及M5组成。带隙基准电压可表示为: 当误差放大器的增益足够大时,由“虚短”原理可知电压UA和UB近似相等。考虑三极管基极电流的影响,三极管Q1、Q2、Q3、Q4的电流放大倍数分别为β1、β2、β3、β4,集电极电流分别为IC1、IC2、IC3、IC4,基极电流IB为IC/β,由此产生的正温度系数电流IPTAT、电阻R1上的电流IR1和电阻R3上的电流IR3分别为: 当三极管电流放大倍数大于特定值βS时,则三极管基极电流对带隙基准电压UBG的影响可忽略不计。将式(7)~(9)代入式(6)可得: 误差放大器以三极管Q1和Q2作为差分输入管对,具有失调电压小、噪声低等优点。同时通过三极管Q3、Q4和电阻R3为误差放大器提供偏置,无需额外的偏置电路,可以减小芯片面积并降低整体电路功耗。M2和M4采用低阈值Native管,有利于Q1和Q2工作在线性区,从而确保整体电路具有足够的环路增益。 带隙基准电路总体芯片版图如图7所示,采用SMIC 0.18 μm CMOS工艺完成带隙基准电路的设计和仿真验证。 图7 总体芯片版图 图8显示了不同温度下的带隙基准参考电压UBG和电路总电流Itotal仿真结果。 图8 典型工艺角下参考电压仿真结果 图9为室温下失调电压1 000个样本的蒙特卡洛仿真结果。 由图9可知,失调电压标准偏差值σ约为4.47 mV,参考电压平均值μ约为1.25 V。 图9 室温下失调电压仿真结果 图10为1 000个样本下电源抑制比(Power Supply Rejection Ratio,PSRR)的蒙特卡洛仿真结果。 根据图10,PSRR在100 Hz处的仿真结果都优于-59 dB,表明本设计具有相对较好的电源噪声抑制能力。 图10 电源抑制比仿真结果 图11为在室温27 ℃和典型工艺角下输出电压和电路总电流随电源电压变化的仿真结果。 根据图11,当电源电压为2.5~5.5 V时,消耗的总电流最大约为128 μA。 图11 不同电源电压下的仿真结果 本文与其他文献中的带隙基准电压源的性能比较结果如表1所示。 根据表1,本文设计的带隙基准电路兼具电路结构简单、低功耗、低失调电压等优点。 表1 不同带隙基准电压源性能对比 本文介绍了一种具有失调电压抑制的低失调和低功耗的带隙基准电路,采用了新型带隙基准结构,抑制了误差放大器失调电压的影响,无需增加额外的失调消除电路,具有低功耗、低失调电压和结构简单等优点。采用SMIC 0.18μm CMOS工艺完成电路设计和仿真验证,可满足无线网络、便携式可穿戴设备和生物医疗等应用需求。

2 带隙基准电压源电路

3 仿真结果

4 结 论