用于量子电压基准中约瑟夫森结阵列的CMP平整化工艺研究

2022-05-12曹文会李劲劲

赵 欣, 曹文会, 李劲劲

(中国计量科学研究院 前沿计量科学中心,北京 102200)

1 引 言

现阶段使用较为广泛的Nb,NbN基超导器件制备技术[1~3],借助于半导体集成器件的成熟工艺[4~9],有能力制作出几十万个约瑟夫森结集成的超导电路[10~12]。但是随着器件规模的扩大,研究发现器件质量与集成化水平主要受到了互联密度的制约,因此增加更多的导线层是未来超导电路技术发展的关键。构建多层金属互联结构在芯片水平上提供了提高其性能的重要机遇,化学机械平整化(chemical mechanical planarization,CMP)则是实现器件层间材料平整化处理的最佳选择[13,14]。

2004年,Ishizaki实现了NbN/TiN的双结堆叠阵列可编程约瑟夫森电压标准(programmable Josephson voltage standard,PJVS)。该电路包含有超过260 000个结,并可以在10 K温度时表现出+/-6 V的恒定电压台阶,器件的第一层NbN薄膜使用CMP工艺进行平整化处理[15]。2008年,Yamamori实现了一种PJVS电路运行在18.5 GHz和10 K温度环境,拥有总共524 288个双层堆叠的NbN/TiNx结,其中首层NbN使用了CMP工艺[16]。另外,Kieler在2009年报道了结合CMP技术与电子束光刻(electron-beam lithography)的工艺也可用来加工亚纳米尺度的SNS型结[17]。中国计量科学研究院(National Institute of Metrology of China,NIM)一直致力于Nb/NbxSi1-x/Nb约瑟夫森结电压基准器件的研究[18,19],为了进一步提高器件质量与集成度,急需在堆叠约瑟夫森结阵列芯片的SiO2绝缘层平整化处理中引进CMP工艺。

文中首先介绍了使用两种不同合成方法形成SiO2层的优化CMP流程,随后展示了CMP工艺应用于包含结阵列结构的表面平整化效果。

2 样品制备

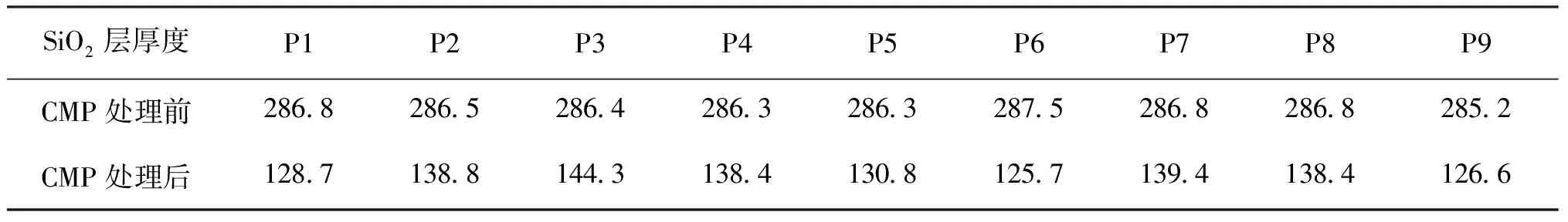

第一步,在两片5.08 cm(2英寸)硅衬底上利用不同方法制备SiO2绝缘层。一片硅衬底上覆盖有280 nm厚的热氧化(thermal oxide,TO)SiO2层,另一片硅片使用化学气象沉积(chemical vapor deposition,CVD)沉积570 nm厚的SiO2薄膜,其结果如图1所示。为了方便计算衬底上的材料去除率,在两片晶圆上各自标注了从1到9的位置点。

图1 使用TO和CVD获得含有SiO2层的衬底

第二步,制备表面图形化的2英寸样品,其中Nb/NbxSi1-x/Nb层使用了磁控溅射系统来沉积。使用光刻工序来定义结阵列图形后,利用电感耦合等离子体(inductive coupled plasma,ICP)和反应离子刻蚀(reactive ion etching,RIE)来刻蚀样品表面。接着通过去胶、清洗和烘干步骤获得了结阵列晶圆样品。之后使用常规的等离子增强化学气象沉积(plasma enhanced chemical vapor deposition,PECVD)生长方法在结阵列表面覆盖600 nm厚的SiO2层。最终获得的结阵列上方SiO2覆盖层的台阶高度在240 nm。

3 CMP处理衬底流程

3.1 CMP处理SiO2绝缘层

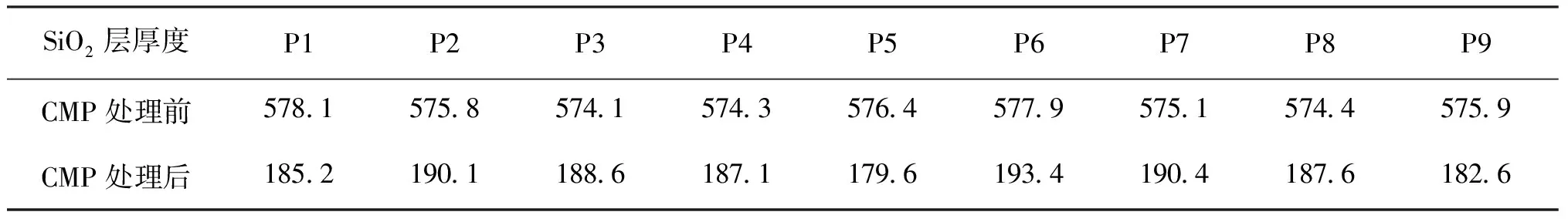

实验中采用的CMP系统是一种半导体行业内较为简易的装置(Model Universal-150),系统的重要工作参数诸如下压力、平台转速、抛光液泵送速率等均需要人工操作与设置。SiO2绝缘层厚度测量采用椭偏仪。表1给出了CMP处理TO生长的SiO2层的结果。计算得出表面材料去除高度最大值为161.8 nm,最小值为142.1 nm,平均值为151.8 nm,最大值与最小值相差19.7 nm。

表1 CMP处理TO生长的SiO2层的结果

表2给出了CMP处理PECVD生长的SiO2层的结果。计算得出表面材料去除高度最大值为396.8 nm,最小值为384.5 nm,平均值为388.6 nm,最大值与最小值相差12.3 nm。CMP系统对于两片含有SiO2绝缘层平整化的结果显示,全局材料去除高度差均在20 nm以内,实现了较好的晶圆表面全局平坦化效果。CMP系统的运行参数设置如下:晶圆和抛光垫的转动速率分别为97 r/min和103 r/min,抛光液的泵送速率控制在150 mL/min。当抛光头施加的下压力在2.47 N/cm2,计算出PECVD合成SiO2薄膜的抛光速率在3 nm/s,而TO形成的SiO2薄膜的抛光速率为2 nm/s。实验中,出现了诸如抛光终点判断[20],抛光后清洗等问题需要进一步加以研究。

表2 CMP处理PECVD生长的SiO2层的结果

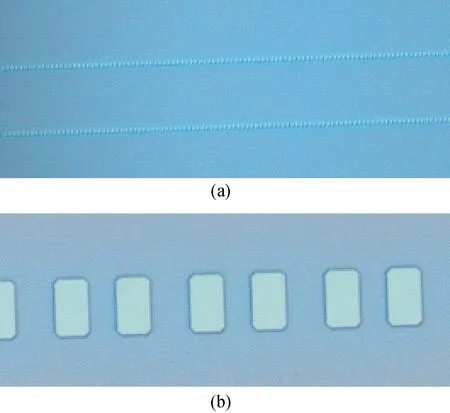

3.2 CMP处理Nb/NbxSi1-x/Nb结阵列的绝缘层

图2给出了CMP处理后的约瑟夫森结阵列光学照片。结阵列以及结单元结构的放大图像显示CMP平整化处理工艺并没有引入可见的结构损坏。该结果初步表明,经过优化的拥有相近参数设置的CMP流程可以很好得工作在图形化衬底表面。经过耗时95 s的平整化过程,结阵列台阶与结边界区域均获得了较为均匀的SiO2绝缘层去除厚度,并且处理后表面过渡平滑。

图2 CMP处理后的约瑟夫森结阵列光学图片

图3(a)和图3(b)为使用原子力显微镜(Atomic force microscope,AFM)分别对CMP处理后的CVD合成SiO2层和结阵列结构上的SiO2层进行形貌测量得到的图像,结果给出了CMP处理后表面粗糙度和台阶边沿处形貌过渡的相关信息。选定的两处2×2 μm2区域内表面粗糙度值较为接近,其粗糙度Ra值分别为0.553 nm和0.535 nm,并没有因为初始表面形貌差异而产生极大差异。

图3(c)为沿图中箭头方向的结单元结构AFM高度轮廓扫描结果。图3(c)中数据显示在水平方向大约35 μm的范围内,特征结构单元的顶部高度变化量在25 nm左右。这一结果与处理前的240 nm的台阶高度相比较,得出该结构的台阶高度去除率约为90%。

图3 AFM对覆盖有SiO2层的无图形衬底和包含结阵列图形衬底CMP处理后表面检测的结果

4 结 论

通过两种不同合成方法制备的SiO2层CMP处理实验,得出了优化的CMP流程参数设置范围。并将CMP流程移植到Nb/NbxSi1-x/Nb结阵列结构的绝缘层平整化处理中。实验数据显示结阵列之上的绝缘层台阶高度可以从240 nm削减到25 nm附近,同时拥有较低的(0.535 nm)粗糙度值。以上结果表明该CMP流程适用于下一阶段的电压基准器件构建流程。