基于P2020 处理器局部总线锁存处理分析

2022-05-10郭京胡益诚刘博

郭京 胡益诚 刘博

摘要:局部总线接口是P2020处理器应用场景较多的接口之一,为了节省芯片管脚数量,P2020芯片对局部总线进行了地址数据管脚复用,因此,硬件需要设计锁存器来区分地址和数据信号。当使用FPGA实现锁存器功能时,如果不考虑FPGA布线带来的时序误差,容易出现锁存地址出错的情况,文章通过分析P2020 处理器局部总线锁存功能,结合逻辑时序分析,设计了一种同步锁存处理的逻辑方案,对地址信号锁存时进行时钟同步设计,最终使逻辑实现锁存器达到稳定锁存地址的效果。

关键词:P2020处理器;局部总线;FPGA锁存器;时序分析

中图分类号:TP31 文献标识码:A

文章编号:1009-3044(2022)09-0017-02

P2020处理器是FreeScale 公司推出QorIQ P2 平台处理器,该型处理器结合了高性能64 位e500 内核,基于Power Architecture 技术,凭借其低功耗、高效率的特点广泛地应用于各类嵌入式场景,P2020处理器局部总线支持GPCM、FCM和UPM 三种控制模式。一般选用GPCM模式作为访问NOR FLASH等并行存储的主要方式。为了节约管脚,P2020局部总线中一部分地址线与数据复用,通过锁存信号来区分地址或数据信号,因此硬件设计需考虑锁存功能的实现[1]。本文主要对P2020 处理器局部总线锁存功能进行了分析与设计,使锁存后局部总线达到最稳定结果。

1 锁存功能时序分析

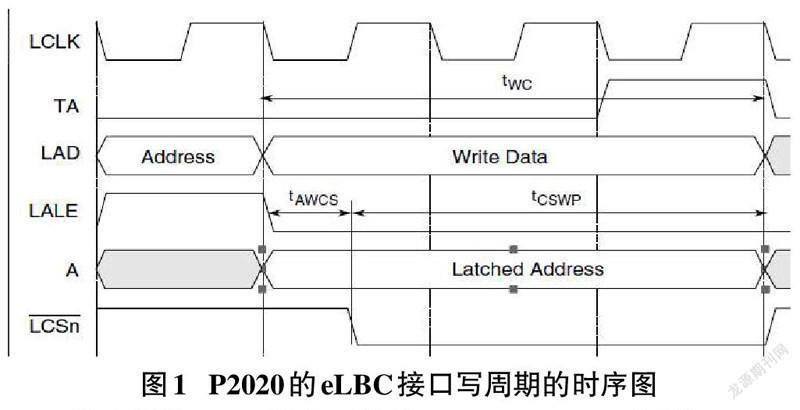

如图1所示,在一个LCLK周期内,锁存信号置高的同时地址数据LAD线上传送地址信号。而后,LALE锁存信号撤销后,LAD也变为数据信号。实际上,处理器为了保证锁存器LALE在撤销前能锁住正确的地址信号,P2020芯片规定值为LALE比LAD地址信号早撤销一个平台周期,平台周期配置为8倍LCLK频率。即LAD地址信号撤销比LALE撤销慢1/8LCLK。这样就可以保证外部锁存器在锁存信号后有足够的保持时间(hold time)[2]。

以处理器P2020平台时钟为400MHz,LCLK时钟为50MHz为例,综上所述可知:

a.一个锁存周期为20ns,即在20ns内,LAD上地址信号与LALE都发生了建立、保持、撤销三个阶段。

b.在LALE高有效期内,LAD总线上为地址信号,且LALE信号撤销会比LAD上地址信号撤销早一个平台时钟周期,即LAD上地址信号相对于LALE下降沿的保持时间为2.5ns。

2 锁存设计中的时延

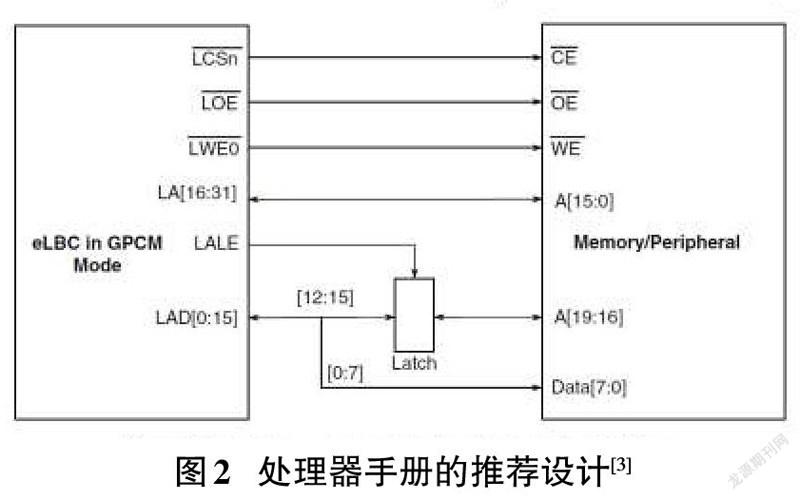

如图2所示,P2020手册中推荐的锁存功能实现方法是在处理器与外设之间,通过一个硬件锁存器,通过LALE控制锁存器,用来输出稳定的地址与数据信号。

当使用外部锁存器芯片时,只需满足锁存器锁存信号的脉冲宽度和地址保持时间后,即可锁存出正确的地址信号。但是在设计中,常常会用FPGA逻辑功能所取代外部锁存器。此时设计过程中如果按照手册做简单替换,锁存处理会发生预期之外的现象。

当逻辑中锁存器在LALE的下降沿时锁存地址,理论上锁存器是在20ns时钟周期中最后2.5ns才开始地址信号采样,即锁存地址时已经非常接近锁存周期结束,LAD地址信号即将撤销。此时需考虑走线过程产生的时延。实际设计需考虑:

a. CPU的内部信号从內部寄存器输出到CPU端口需要的时延为Tdelay1;

b. PCB布局布线的信号从CPU端口发出传送至FPGA端口存在传输时延为Tdelay2;

c. 信号从FPGA端口锁存至FPGA内部寄存器需要的时延为Tdelay3。

从CPU发出eLBC信号至FPGA内部锁存器锁存前,LAD中16位地址信号与LALE锁存信号都会存在Tdelay1+Tdelay2+Tdelay3的时延,若两组信号时延差异超过了保持时间2.5ns,即LALE到达锁存器时间太晚,导致则逻辑中锁存器在LALE的下降沿锁不住LAD正确的地址信号。实际设计中,当芯片距离较近时,Tdelay1和Tdelay2的误差可忽略不计,但由于FPGA逻辑综合后的差异,Tdelay3的差异可能会远超2.5ns。

3 逻辑实现外部锁存器的分析

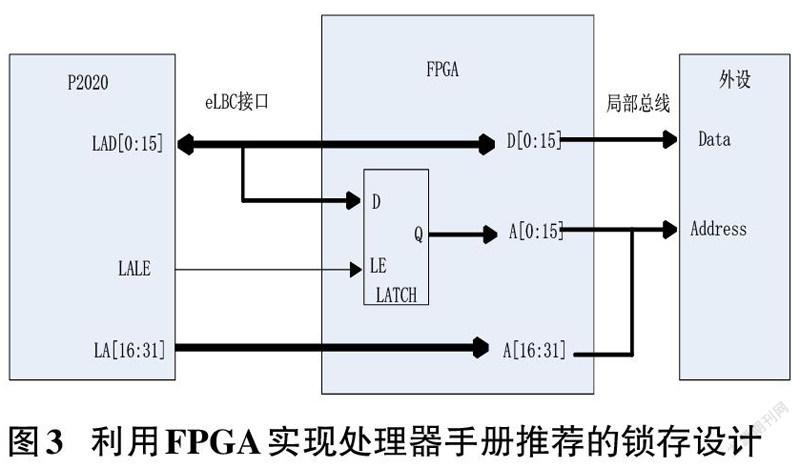

参照图2手册推荐设计,逻辑实现锁存器如图3所示,该硬件设计为P2020处理通过FPGA实现锁存器输出地址数据信号,在一个访问周期内,eLBC总线的从设备必须在LALE锁存信号有效时,将LAD[0:15]有效的地址信号锁存起来作为局部总线的A[0:15]位。而后, LALE信号变为无效,LAD[0:15]作为局部总线的数据线使用,CPU在FPGA的译码逻辑后形成可访问外设的Local Bus接口。

如果逻辑中锁存器在LALE上升沿采样时,结合图,可知,LALE与LAD上地址信号同有效,锁存器中,LAD相对LALE上升沿的理论建立时间为0,因此该种采样方式不合理,只能在LALE下降沿采样锁存信号。

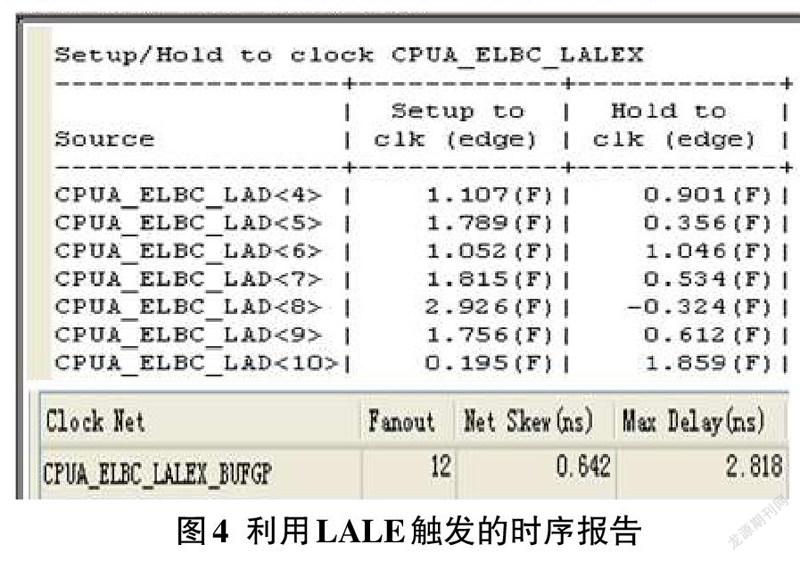

查看在LALE下降沿采样锁存信号设计方式生成的逻辑静态时序报告,如图7所示,以LAD(10)信号线为例,LAD(10)经过触发器时的静态时序,有:

a.LAD(10)建立时间(setup time)为0.195ns,该时序代表经过逻辑布线后,LAD(10)在逻辑触发器LALE下降沿采样前,需要提前0.195ns建立时间;

b.LAD(10)保持时间(hold time)为1.859ns,该时序代表经过逻辑布线后,LAD(10)在逻辑触发器LALE下降沿采样后,需要有1.859ns保持时间后信号可以结束。

c. 考虑最理想情况,处理器发出锁存信号下降沿后,地址线可以保持2.5ns,即若LAD(10)要被逻辑触发器成功锁存,在从处理器发出信号到逻辑采样前,通路上的LAD(10)相对于LALE锁存信号的下降沿至少需要保持2.5ns-1.859ns=0.641ns的时间裕量。

d. 由于该种设计基于LALE采样,所以逻辑会把LALE当作时钟信号处理以保证输出时钟的稳定性。此时会不可避免地产生LALE的延迟与抖动,从而消除甚至超过LAD(10)相对于LALE下降沿的保持时间裕量。查看时钟报告中LALE信号,LALE经过逻辑会产生0.642ns的抖动以及最大2.818ns的延迟,该抖动已经超过该种方案c条件中最小裕量。

综上所述,经过逻辑处理后LALE的下降沿采样时无法保证采样到正确LAD(10)信号,存在时序紧张的风险[4]。

4 改进后的设计及验证

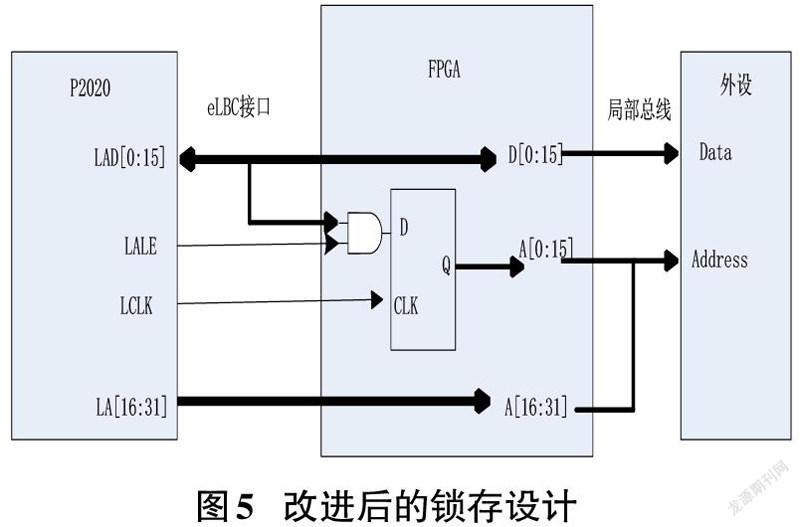

由于FPGA本身存在布局布线的误差,在逻辑中按照处理器手册设计锁存器会存在时序紧张的风险,造成LAD锁存出错。考虑不同实现方法中的差异,需设计一种新的逻辑锁存方法。如图5所示

利用逻辑设计锁存功能时,应当进行时钟同步,即eLBC接口的LCLK时钟作为触发信号,逻辑对LCLK时钟的上升沿采样,这样当LALE锁存信号为高时,进行地址锁存,逻辑采样点相比之前设计前移,处于地址锁存周期的中心时刻,可以有效保证采集到稳定的地址信号,可充分避免因走线布线带来的时序误差[5]。该种设计有:

a.处理器发出的所有LAD地址信号对于20ns时钟周期LCLK的上升沿的建立与保持时间都为10ns;

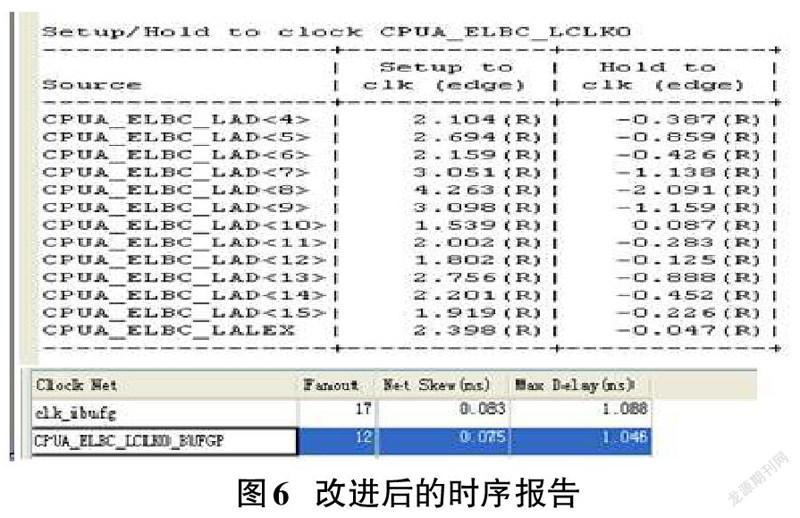

b.如圖6所示,新设计逻辑中所有LAD信号的对LCLK上升沿要求的建立时间和保持时间都在5ns之内;

c.采样时钟LCLK经过逻辑后产生延时与抖动分别为0.075ns与1.046ns。

综上所述,在最恶劣情况下,该种设计方案b、c条件中任意时序要求之和、之差都小于a条件中信号产生的时序,即处理器产生LAD信号对于LCLK上升沿的10ns建立与保持时间可充分满足逻辑采样对时序的要求。因此,该种设计可以消除了时序紧张,且拥有较大的时间裕量,可以保证系统实现锁存功能的可靠性与稳定性。

5 结论

当使用逻辑实现P2020处理器锁存功能时,需充分考虑不同设计方式中的差异,当使用硬件锁存器芯片时,整个硬件中时延较小,按照手册推荐,满足相应时序要求即可。当使用逻辑实现锁存功能时,需要考虑逻辑芯片在布局布线过程中对各类信号产生时延对锁存功能的影响,需要进行锁存功能的同步处理,使得锁存后的结果更加稳定可靠。

参考文献:

[1] 冯毅,付洁.P2020处理器LBC总线位宽转换算法研究[J].信息通信,2018,31(11):116-117,119.

[2] 冯毅,陈颖图,程小芩.P2020处理器GPCM接口时序研究[J].航空计算技术,2019,49(1):127-129.

[3] P2020 QorIQ Integrated Processor Reference Manua Rev.2[C/OL]. NXP Semiconductor Corp. http://nxp.com, 2012.

[4] 成桂梅,翟国芳,吴淞波,等.一种FPGA布局布线延时特性测试方法:CN105117513B[P].2018-08-07.

[5] 姜子威.超高速数据采集系统中多器件同步自校正方法研究与实现[D].成都:电子科技大学,2019.

【通联编辑:梁书】