EDA 设计中的等长不等时研究

2022-05-08耶菲

耶 菲

(中航工业西安航空计算技术研究所,陕西 西安 710068)

引言

在印制板设计中,等长是一个很常见也很成熟的环节,在印制板设计软件的等长约束器中可以设计各种等长规则,如一组线的长差不超过X,一组线中以A 线为基准±长度偏差,或是以A+n mil 为基准偏差。但是等长线的本质就是要保证信号的同时到达,什么又是同时到达呢?有些厂家会推荐一组信号线误差控制在若干ps 内,而另一些厂家会给出控制在若干mil 以内,既为等长。给出时间的EDA 设计人员需要换算长度信息落实在印制板设计中,而给出长度信息的,EDA 设计人员可以直接使用在印制板的规则设计中。以DDR3 为例,数据手册中推荐DDR3 的一组数据线长差在100 mil 内就不会影响其时序,可以算作等长,可是是否在印制板当中保证了长差在约束范围内就一定可以保证信号可以同时到达呢?又有哪些情况会在EDA 设计的等长线中影响到时延?一般来说是这样的,保证了长差就可以保证信号的同时到达,但是有一些特殊情况例外,这与EDA 设计者使用的软件以及印制板的结构有关,这里就简述其中的几种情况。

1 带状线和微带线

印制板当中信号的速度与印制板中传输线的结构有关,带状线和微带线为图1 所示。对于信号的传输速度不一致,所以对于同样长度的带状线和微带线对于信号的延时不同。

图1 带状线与微带线

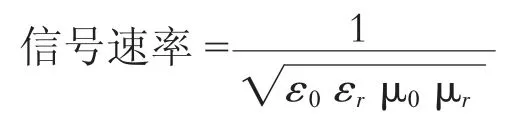

信号在带状线中的速率为[1]:

式中:ε0为自由空间介电常数,取8.89×10-12F/m;εr为材料的相对介电常数,FR4 带状线取值约为4,微带线取值1~4 之间;μ0为自由空间的磁导率,值为4π×10-7H/m;μr为材料的相对磁导率,取1。计算得出带状线中的传输速率约为6 in/ns 或是170 ps/in,微带线约为7 in/ns 或是140 ps/in。

这就导致两条长度相等的传输线A 和B 线长度都为5 in 的条件下,如果A走在表层,B走在中间层,则其时延差=(160 ps-140 ps)×5=100 ps,如果长度更长则时差更大。

而现在采用更多的是混合设计,就是传输线从器件管脚经过一段微带线到中间层走一段带状线,然后再回到表层通过一段微带线到达另一个器件,就是微带线-带状线-微带线的结构。由上面的计算可以看出如果物理等长过的两条线,其微带线和带状线的占比不一致也会导致时延不一致。

这会不会为设计带来很大的风险呢?以一般设计为例,在一般的DDR 走线中如果遇到表层无法直接扇出,而需要在表层走一段线后在扇出的,一般这个长度不会超过200 mil,则它与其他正常扇出的同组线之间的时延差=(160 ps-140 ps)×0.2 in=4 ps。

这对于组信号的影响非常小。以DDR2 为例,一个DQ 组内时差在17 ps 内都满足是需要求[2],所以只要不是极端情况将一组数据线中的一条或几条线完全走在表层就不会有太大的问题。而对于等长要求更为严格的差分线来说,由于要求同层所以不会存在此类设计问题。

2 过孔长度的影响

严格来说这类应该属于不等长的情况,因为此类情况软件中显示等长可是实际情况长度不相等。因为一些软件不会将过孔长度计入到传输线长度中。现在一些新版本的软件,修复了这些问题。如图2 所示。

图2 过孔长差

以2 mm,16 层的印制板中的2 条线为例,都从top 到bottom。A 线top-bottom-top-bottom;B 线top-bottom。其中每一个“-”代表一个换层过孔,因为板厚2 mm 由top 到bottom 则过孔长度为2 mm。

如果AB 两条走线在设计及软件中等长,则因为其没有算入过孔长度其真实长差为两个过孔的长度。

真实长差=2 mm×2=4 mm=160 mil,在印制板设计中这样的长差是一个无法被忽视的存在,可能会导致一组信号的时序问题。

在以另外两条线为例,板厚2 mm 16 层,A 线top-3-top;B 线top-14-top。

在印制板设计中,如果同一层无法走下A、B 两条线,将A、B 两条线分别走在不同的信号层是非常常见的情况。以1-3 层过孔长度0.2 mm计算,由于印制板多为对称性,1-14 层过孔长度为2 mm-0.2 mm=1.8 mm 其过孔带来的长差。

A 线过孔长度=0.2 mm×2=0.4 mm。B 线过孔长度=1.8 mm×2=3.6 mm。AB现在软件中等长,其实际长差=3.2 mm=128 mil。

这也会为信号带来不小的影响,这样的长度不应当被忽视。所以在实际设计中,应避免同类传输线过孔数量不一致的情况,对于要求比较高的同组线,尽量同层,这不光使一组线的传输环境相同,也会避免此类因过孔导致的长差问题。而在一些新的设计软件中已经将VIA 的长度考虑在等长长度中,这需要在设计时将印制板的叠层信息设置在软件中。如果不能正确地设置叠层结构也会导致软件的计算有所偏差。

3 过孔时延的影响

由于过孔结构与带状线和微带线结构的不一致,导致信号在过孔中的速度与在带状线和微带线中的速度也不一致。

信号在微带线中的速率约为170 ps/in;信号在过孔中的速率约为360 ps/in。仍以上节两条信号线A、B 为例:A 线top-3-top;B 线top-14-top。

过孔长度。A 线过孔长度=0.2 mm×2=0.4 mm;B 线过孔长度=1.8 mm×2=3.6 mm。

其过孔长差为3.2 mm,延时差为24 ps。这样量级的时延将可能对如DDR3 的数据线带来影响,不应被忽略[3]。

所以即便是使用手工计算或是使用软件将过孔的长度计算在传输线长度内,对于要求精确等长的一些信号线,同组尽量走同层避免由于过孔长度带来的时延导致信号完整性问题。

4 芯片封装内时延

严格来说芯片内延时也不属于不等长的情况,因为我们单独讨论PCB 走线时是不等长的,但是从整个链路上来说,我们要保持信号路径的整体长度相等。

信号的整个路径=印制板走线+焊盘、管脚长度+芯片内走线。同一组信号在PCB 走线长度完全一致的情况下如果焊盘、管脚长度或是芯片内部走线长度不一致也会引发信号无法同时到达芯片DIE,导致同一组信号的时序混乱。这时PCB 在设计等长时应当考虑补偿印制板焊盘、管脚长度和芯片内部走线长度的不一致。

一般来说芯片内部的pin delay 会以表格的方式由厂家提供给设计师,单位为ps。设计师将延时转换为PCB 长度信息,并补偿在PCB 的设计中[4]。如图3 为在EDA 设计软件中设计pin delay 补偿。

图3 设置pin delay 补偿

还有一种为管脚长度不一致,这种一般出现在连接器中,如下页图4,图中B 和D 管脚长度不一致,则在有等长要求的信号使用此类连接器时应根据管脚、焊盘长差在PCB 走线时作出补偿[5]。

图4 连接器管脚长差

此类PIN DELAY 由于不是在印制板当中,所以信号在管脚以及芯片内部的传播速度很可能不一致,这就是芯片厂家一般会以ps 为单位来描述pin delay 以确保时序完整。

5 玻纤效应

印制板当中信号的速度与印制板中传输线所参考的介质的介电常数有关。FR4 的具体材料为环氧玻璃布纤维,从微观角度上来说,玻璃纤维和树脂的介电常数不一致,这会导致走在玻璃纤维上的传输线延时与走在树脂上的传输线延时不一致。

以极端情况为例:A、B 两条线,A 线完全参考玻璃纤维,B 线完全参考树脂,玻璃纤维的εr值为6,树脂材料的εr值为3~4,取3.5。A 线信号速率4.8 in/ns;B 线信号速率6.4 in/ns。

以两条都长度为1in 的A 线和B 线来说:A 线时延200 ps/in;B 线时延150 ps/in。

如果这两条线刚好分别是一对差分线的正和负,这样的时差为50 ps,对于速率高于若干差分线的信号质量都会产生毁灭性打击。其实玻纤效应对差分线的影响不仅于时延,两条线的阻抗和衰减都不一致,会带来很多差模干扰,但本文仅针对时延进行讨论。

为了避免此类问题的发生,可以考虑选用玻璃纤维更加致密的板材,或选择玻璃纤维布质地更加均匀的板材,从源头上减小此类问题的发生。或使用有斜率斜走线,减少使用0°和90°走线,(inter 有推荐采用斜10°走线)使一对差分中的两条线交替参考玻璃纤维以及树脂,以减小极端情况的发生。是否可以在生产印制板中采用带角度下料的方式,使印制板中现有设计的0°和90°走线不至于单独参考玻璃纤维或是树脂材料,而是交替参考已解决此类问题的发生。

6 结论

印制板中等长的目的在于保证并行信号的时序及信号完整性。本文仅从印制板的结构、材料、器件和设计软件等方面列举了一些等长不等时的问题,其实还有其他原因带来的等长不等时。以上列举的等长不等时的问题,如果出现在印制板中即便是等长仍然会产生时序及信号完整性问题。如果可以的话尽量从设计上避免此类不一致,如果无法避免应评估其带来的影响,或是通过计算补偿其带来的时延差。