高效线性氮化镓射频功放芯片模组研究*

2022-04-20狄皓月陈文华吕关胜

狄皓月,陈文华,吕关胜

(1.优镓科技(北京)有限公司,北京 100000;2.清华大学,北京 100000)

0 引言

数据速率的快速增长催生对具有高频谱效率和大峰均比的高速复杂调制方案的需求,5G 通信基站射频通道更多、带宽更宽、频率更高、峰均比更大。而功率放大器及其相关的基带电路作为通信基站的主要耗能元件,功耗占比超过50%,这对功率放大器的功率回退效率和线性度提出了更高的要求。普通的AB 类功率放大器在回退点效率降低严重,整体功耗很大,因此需要提升功率放大器的回退效率。回退效率增强的有效解决方案包括Outphasing[1]、包络跟踪(ET,Envelope Tracking)[2]和Doherty 功率放大器(DPA,Doherty Power Amplifier)[3]等。其中,DPA 采用两路放大器并联,一个功率放大器偏置在AB 类,另一个功率放大器偏置在C类,仅在高功率区开启工作,这种结构可显著提升回退效率,同时其结构简单、性能优异,很受欢迎。

理想的DPA 具有线性响应[4],但实际的晶体管存在非线性电容和跨导以及米勒效应,因此DPA 具有很强的非线性[5-7]。为了满足信号质量和带外频谱发射要求,采用数字预失真(DPD)提高线性度。如今DPD 已经被广泛应用于大功率宏基站的DPA 中[8],然而由于DPD 的硬件成本和功率开销,其在路由器、手机、调频电台等一些小至中功率的功率放大器单元的应用场景受限。因此,如何提高DPA 的原生线性度,避开使用DPD,进一步扩大DPA 的应用领域成为新的研究热点。

1 高线性度DPA技术

1.1 提高DPA线性度的三种方法

提高DPA 的线性度主要方法有三种:三阶交调失真的消除[9-12]、幅度-幅度(AM-AM)预失真[13-15]、幅度-相位(AM-PM)矫正[16-22]等。通过对主、辅两路晶体管偏置电压[9]和输入端功分比[10]的优化,主路和辅路两个分支的三阶交调可以在合路点实现对消。由于三阶交调主要是由晶体管的三阶跨导(gm3)引起的,有学者[11]在DPA 的主路中采用了多门控晶体管(MGTRs),以此来最小化在大功率范围内的等效三阶跨导。此外,一部分三阶交调信号来源于基频信号与二次谐波信号的混合,因此将二次谐波阻抗设为短路可以进一步降低三阶交调信号的强度[11-12]。由于负载调制机制和辅功率放大器的C 类偏置状态,DPA 的AM-AM 特性非常不平坦。自适应偏置架构是常用的提升大信号区增益的方式[13],其常用于毫米波DPA 设计中,也有学者提出模拟的线性化器来改善DPA 的AM-AM 响应[14]。有学者[17-18]在主路和辅路分支前各插入了一个非线性的驱动级来抵消末级的AM-PM 失真,也有学者提出了一种具有复杂漏极阻抗的电流缩放DPA,并利用其固有的非线性相位响应来抵消由主晶体管和辅晶体管引入的AM-PM[19]。在其影响之下,Fang 等人提出来一个具有预定义AM-PM 特性的输出合成网络[20]。然而,该输出合成网络在大信号区展现出了明显的增益压缩特性,进而需要特别注意输入匹配网络的设计。Lyu 等人提出在DPA 的输出插入电桥,通过调整电桥隔离端的电抗值调整输出网络的AM-PM 特性,抵消DPA 的AM-PM 失真[21],该方法引起的增益压缩要小很多。但鉴于输出正交耦合器的尺寸相对较大,这种方法不便于集成。以上是几种提高DPA线性度的方法,由于负载调制机制和密勒效应的影响[6-7],DPA 的AM-PM 比单端的PA 要严重很多。AM-AM 可以用简单的无记忆的DPD 来高效补偿,相比之下AM-PM 要难处理很多,往往需要更复杂、更强大的DPD 来补偿[16]。因此,设计过程中的AM-PM 减少可以带来更高的收益。

基于这样的应用需求,本项目提出了一种基于相位失配的AM-PM 补偿方案,并取得了不错的效果。以下对本方案做一些简单的诠释:输出相位失配指的是输出阻抗变压器的相移偏离,输入相位失配则指的是主辅分支相位不对齐。当引入输出相位失配时,功率合成网络将会展现特定的AM-PM 特性,其代价为回退性能的小幅降低;当引入输入相位失配的时候,功率合成网络的AM-PM 特性可以得到进一步的调整,其代价为饱和性能的小幅降低。通过选择合适的输出相位失配和输入相位失配,DPA 固有的AM-PM 失真得以抵消,因此DPA 的整体AM-PM 可以被最小化。此外,相位失配的功率合成网络表现出了增益拓展的特性,因此DPA 的AM-AM 特性也可以得到一定程度的改善。

1.2 基于相位失配的AM-PM补偿理论

图1(a)展示了传统的对称DPA 的拓扑结构,其中Ropt表示主路功放的最优负载阻抗。由于晶体管的非线性和寄生效应,实际的DPA 会出现AM-AM 失真和AM-PM 失真。与AM-AM 失真相比,AM-PM 失真更难处理。在低功率区,由于只有主功放工作,DPA 的AM-PM 特性与单端的DPA保持一致。然而,一旦进入高功率区,DPA 的AM-PM 失真特性就会变得非常严重,这是由于负载调制效应通过米勒效应使得输入端电容发生巨大变化[6-7]。

为了增强DPA 的线性,本文提出了基于相位失配的AM-PM 补偿方法。图1(b)展示了本项目提出的对称DPA 架构,其中θ是输出阻抗变换器的相移,φ是主路和辅路之间的相位差。相位失配意味着θ偏离90°,φ不是零而是偏离90°则为输出相位失配,φ不为零则是输入相位失配。后续几个小结的讨论将会指出这两者都可以用于使功率合成网络产生特定的AM-PM 特性,而且代价仅仅是饱和表现和回退表现很小程度上的恶化。而实际DPA 固有的AM-PM 失真则可以用这样的功率合成网络来补偿,进而让整体的DPA 实现很好的AM-PM 特性。

图1 传统DPA架构与本文提出的DPA架构

与在引言中提及的几种减弱AM-PM 失真的方法对比[17,19,21],本项目中采用的方法有几个明显的优点。首先,提出的DPA 架构简单与传统的DPA 可以兼容,因此本方案在集成设计中有其便利性,一些针对传统DPA 的设计方法可以直接用在这里。其次,带相位失配的功率合成网络展现出了增益扩张的特性,DPA 的AM-AM 特性也可以得到改善。再次,在本架构中,输入相位失配可以通过在输入相位补偿网络中引入开关来调节,因此由工艺容差带来的AM-PM 变化可以在一定程度上得到补偿。

1.3 方法分析

将图1(b)简化为图2,其中主路和辅路的晶体管用两个电流源代替,以方便分析。

图2 用于理论分析的简化结构

本文的分析基于以下三个假设:

(1)主路和辅路晶体管都是偏置在B 类状态的具有零膝电压、常跨导、无寄生参数的理想晶体管;

(2)所有的谐波都短路处理,在晶体管的漏极只有基波和直流分量;

(3)晶体管是线性的压控流源,饱和电流是Imax,漏压是Vdc,因此最优负载阻抗为:

尽管这里假设两个功放都偏置在B 类会导致理论分析和实际情况并不完全相符,但是AB-C 的Doherty 需要额外引入很多变量,不容易直观看出本架构的优势。况且,使用B 类偏置状态进行分析在一些已发表文章中已经是很常用的手段了,其有效性已经得到证实,因此这里还是采用B 类偏置状态进行分析。

图2 中,Im/Ia、Vm/Va、Zm/Za分别是主辅路的基频漏极电流、漏极电压、负载阻抗。

输入电压记为Vin,能使晶体管饱和的输入电压为Vin_max,归一化输入电压为:

由于饱和基频电流的幅度为Imax/2,当输入电压为Vin时主路和辅路功放的电流可以表示为:

其中,e-j(θ+φ)即为辅功放比起主功放的相位滞后。

基于上述公式,可以计算得到在输出相位失配和输入相位失配条件下的DPA性能。将功率合成网络的传输系数TC定义为:

那么,功率合成网络从回退区到饱和区的AM-AM和AM-PM为:

以上两个式子表明功率合成网络对DPA 的整体的AM-PM 和AM-AM 特性起到了非常重要的作用。当θ=90°时,功率合成网络并无AM-AM 与AM-PM 变化。然而,当θ偏离90°时,功率合成网络就会展现出由θ和φ决定的相当客观的AM-AM 与AM-PM 特性,对其进行合理的利用可以有效增强DPA 的线性度。

1.4 基于相位失配下的DPA性能

设定φ=0,首先分析输出相位失配下的性能。图3 显示了计算得到的DPA 的归一化AM-AM 和AM-PM 特性。根据图3,即θ<90°时,AM-PM 滞后;θ>90°时,AM-PM超前。由于米勒效应和负载调制机制的影响,实际的DPA通常展现出超前的AM-PM 特性。因此,选择AM-PM 滞后的功率合成网络进行补偿,即θ<90°。从图3(b)可以看出,当引入输出相位失配时,功率合成网络展现出了扩张的AM-AM 特性,在θ=70°/110°时高达1.3 dB。这是本方法的另一优点,可以补偿DPA 的AM-AM 压缩。

图3 本文DPA在不同θ下的归一化

在输出相位失配存在的前提下,输入相位失配同样可以修改DPA 的AM-PM 和AM-AM 特性。图4 为在不同φ取值下提出的DPA 的归一化AM-PM 和AM-AM 特性,可以看出,与输出相位失配相比,AM-PM 对输入相位失配不太敏感。在实际实现中,初始设计可以采用输出相位失配来补偿大部分相位失真,然后可以利用输入相位失真对AM-PM 进行进一步的微调。

图4 本文DPA在不同φ下的归一化AM-PM

2 基于相位失配网络的Doherty功率放大器设计

为了验证上述方法的正确性,基于0.25 μm GaNHEMT 工艺设计一款DPA,整体方案如图5。

图5 整体方案

2.1 输出电路设计

图6 中的示意图用于仿真不同θ值下的相位失真。图7 显示了6.4 GHz 下仿真得到的AM-PM 特性。可以看出,在加入输出相位失配网络(OPM)后,相位失真从10°减低到4°。进一步加入输入相位失配网络(IPM)相位失真降低至1 相。

图6 仿真相位失真和回退漏极效率的原理图

图7 仿真得到传统DPA与本文提出的DPA的AM-PM

如图8 所示,输出阻抗变换器是通过吸收Cout的T 型传输线(TL)网络实现的。T 型网络中的分支TL 可用于给主功放和辅功放的漏极提供偏置。TL 的宽度选择为50 μm,以确保足够的直流电流容量。

图8 输出阻抗变换器的原理图

2.2 输入网络设计

主辅PA 的输入匹配网络结构如图5 所示,两者结构相同,分别调整它们的元件值以获得良好的AM-AM。在回退区域,DPA 的增益完全由主功放的增益决定。对于大功率区域,辅功放在整体增益中也起着重要作用。在设计中,主功放的输入匹配网络在回退区域进行了优化,而辅功放的输入匹配网络在高功率区域进行了优化。由于输入相位补偿理论与仿真有差异,因此这里增加相位补偿网络。一个+25°的相移网络和一个-25°的相移网络分别插入在主、辅PA 的前面。为了方便测试过程中的相位调整,采用开关SW1 和SW2。此外,还可以通过引入开关SW3和SW4 来调节主辅功分比以优化AM-AM。开关的开启、关闭电压分别为0 V 和-20 V,并在每个开关的栅极插入一个5 kΩ 电阻以减少损耗。

3 测试结果

3.1 小信号测试结果

实物DPA 如图9,芯片尺寸仅有2.8×1.5 mm2。

图9 DPA实物图

主功放和辅功放的漏极偏置均为28 V。主功放漏极静态电流为32 mA,辅功放偏置为C 类,使用-4.6 V 栅压。DPA 的小信号性能由网络分析仪测量。图10 展示了从4—8.5 GHz 测得的S 参数,其中还画出了仿真S 参数来进行比较,开关状态的选择基于下一小节中的大信号测量。实测结果和仿真结果一致性良好,但测得的小信号增益比仿真增益低约2 dB,并且实际工作频段向低频段偏移大约200 MHz。测量和仿真S 参数之间的差异很可能是由于有源区模型不准。尽管芯片布局的EM 仿真非常准确,但工艺设计套件(PDK)中提供的有源器件模型通常并不那么精确,这是由建模的复杂性引起的,在GaN-HEMT 器件中这个问题尤为突出。

图10 实测和仿真的S参数对比

3.2 大信号测试结果

大信号性能测试时,使用了矢量网络分析仪在脉冲连续波(CW)信号下进行测试。脉冲宽度和占空比分别为10 μs 和10%,采用Mini-Circuits ZVE-3W-83+驱动放大器来提供足够的输入功率。初始测试表明AM-AM 特性具有较大的扩张特性,因此功率分配器中的SW3 打开以向主功放提供更多功率,而其他开关仍处于关闭状态。在每个频率下,进行多次测量,并将结果取平均值以减少噪声的影响。图11 显示了6.1—6.6 GHz 下测量的DE、AM-AM 和AM-PM 与输出功率的关系。可以看出,在AM-AM 变化低于0.6 dB 的情况下,可实现40.8~41.4 dBm 的饱和功率、60%~62%的饱和DE 和45.5%~47%的6 dB 回退DE。此外,在6.3 GHz 处AM-AM 最小为0.3 dB。在33~41 dBm的输出功率下,AM-PM 的变化在6.3 GHz 为2°,在6.1—6.4 GHz 保持在3 以下,在6.1—6.5 GHz 保持在4°以下。

图11 6.1—6.6 GHz的大信号测量结果

与图7 相比,测量和仿真的AM-PM 响应不一致,但最大相位变化相似,这证明了所提出方法的鲁棒性。测量和仿真的大信号性能之间的差异主要归因于GaN-HEMT 器件的大信号模型不准确,这在一些已经发表的文章中是很常见的。

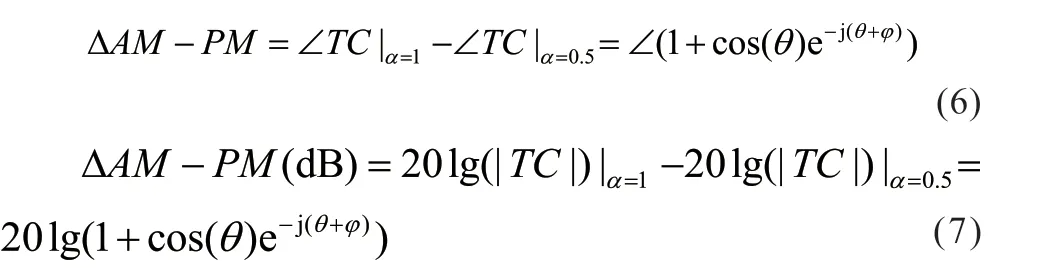

3.3 调制信号测试结果

为了验证调制信号激励下的线性度和效率,使用具有7.8 dB 峰均比(PAPR)的100 MHz LTE 64 QAM 信号来测试。测试频率范围为6.1—6.8 GHz,步长为0.1 GHz。输入调制信号由R&S SMW 200A 信号发生器生成,输出信号由R&S FSW43 频谱分析仪捕获。基于广义记忆多项式(GMP)模型的DPD 用于线性化。GMP 的记忆深度、交叉项记忆深度和非线性阶数分别表示为M、L和K。表1 总结了100 MHz 调制信号下的测量结果。可以看出,DPA 在6.1—6.5 GHz,平均功率约为33 dBm 时实现了优于-42 dBc 的原始ACPR 和36.7%~37.7%的平均DE。运行K=8 的MLDPD 后,ACPR在6.1—6.6 GHz 下提高到优于-48.5 dBc。此外,还应用了M=8、L=2 和K=8 的DPD,进一步降低了ACPR。图12 描绘了在6.2 GHz 载波和33.3 dBm 平均功率下的输出功率谱密度(PSD)。观察到输出频谱有良好的ACPR,无DPD 时为-44.1/-44.3 dBc,使用无记忆DPD 时为-49.8/-51.8 dBc,使用有记忆项DPD 时为-54.0/-55.0 dBc。

表1 100 MHz调制信号测试结果

图12 33.3 dBm平均功率下测得的功率谱密度@6.2 GHz

表2 为本文提出的DPA 与其他DPA 性能的比较。虽然输入和输出的相位失配会在一定程度上减小平均效率,但是与其他传统的DPA 相比,该DPA 线性度较高,具有竞争力。

表2 其他线性DPA对比

4 结束语

本文通过将主功放的输出网络相位偏离,辅功放的输入相位偏离,即主、辅支路相位不对齐,设计了一高线性DPA。分析得出,输入和输出网络相位失配会表现出特定的AM-PM特性,通过适当调节输出相位失配和输入相位失配,可以显著改善AM-PM 失真。同时相位失配表现出增益扩张特性,可以改善DPA 的AM-AM 失真。本文基于0.25 μm GaN HEMT 工艺,设计了一款全集成DPA 来验证上述方法。实测结果显示,6.1—6.4 GHz 中,AM-PM 优于3°,AM-AM 优于0.5 dB,100 MHz 调制信号下,邻信道功率泄漏比ACPR 优于-42 dBc。