集成电路UVM验证环境典型结构设计

2022-04-18孙晓东王治强

孙晓东,王治强

(大连东软信息学院 智能与电子工程学院,辽宁 大连 116023)

从20世纪90年代开始,半导体技术已经发展到深亚微米阶段,集成电路设计的复杂度也呈指数增长,采用传统的集成电路验证技术不仅要花费大量的工作时间,而且无法满足现代集成电路的验证要求[1].针对传统RTL代码验证平台的诸多弊端,在吸取了传统验证方法优点的基础上,3大EDA公司(Mentor,Cadence和Synopsys)共同推出了目前所有验证方法学的标准,通用验证方法学(Universal Verification Methodology,UVM)[2].

UVM是一种高级的层次化数字集成电路验证平台开发框架,它是由Accellera组织在Cadence公司与Mentor公司联合推出的开放验证方法学的基础上构建的.由SystemVerilog语言编写库文件,带有标准化的验证环境接口,有很强的复用性[3-4].

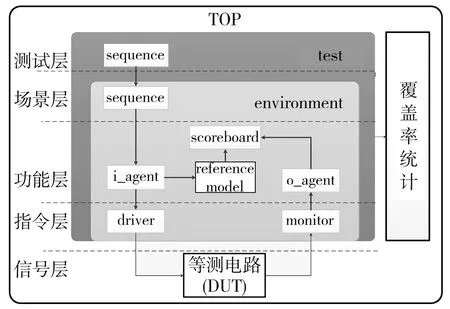

UVM验证方法学中包括interface,driver,monitor,transaction,sequencer,agent,model,scoreboard,environment,sequence,test,top等组件,这些模块按照信号层、指令层、功能层、场景层和测试层的划分组合到一起,形成了完整的验证平台[5].但是UVM的框架是一个通用整体结构,该验证平台结构适用于所有的待测模块,在详细设计的时候需要具体考虑组件的功能结构,需要花一定的时间.本文根据待测模块的功能特点将其分为总线协议、控制器和算法3种类型,针对不同类型的待测模块,通过对reference model和scoreboard进一步细化设计,提出适应该类型待测模块的典型UVM整体验证环境结构.

1 通用UVM验证环境

UVM验证环境结构如图1 所示.该结构分为信号层、指令层、功能层、场景层和测试层.

图1 UVM验证环境结构框图

信号层主要处理输入输出信号.指令层中driver负责给电路施加激励,它按照电路需要的格式,把数据包发送给待测电路,驱动电路工作.monitor负责收集待测电路的反馈信息,捕捉响应的信号[6].功能层中的i_agent会把获取数据包的端口与driver相连,同时把这个数据包发给reference model.Reference model称为参考模型或期待值模型,用于计算期待的正确答案,它需要完成实际电路相同的功能.Reference model将计算出的期待值发给scoreboard.o_agent会把monitor观察到的实际值发给scoreboard.scoreboard计分板会比对期待值和实际值,统计测试结果.本文根据待测模块类型,重点讨论reference model和scoreboard的设计.

场景层中sequencer的作用是先将数据包发送给i_agent,再传到driver中驱动待测电路,在environment中实例化功能层中的agent,model,scoreboard.

测试层中的transaction即事务,是待发送的数据包.transaction定义了数据的类型、宽度还有数据范围约束等信息.Sequence的作用是按照transaction中的数据格式和数据约束,随机产生transaction,并把它发送给sequencer.测试平台启动时先启动test,然后启动environment和其他子模块[7].

2 待测模块功能分类

数字集成电路待测模块按功能分类如表1 所示.根据芯片功能分为接口、控制器和算法3大类[8-9].总线协议又可以分为串口,高速接口和CPU周边总线[10].控制器一般有DMA传输控制器、Memory访问控制器等[11].算法模块根据芯片功能不同,分类也不同.应用在相机芯片中,主要以图像处理为主,应用在通信领域则以信号处理为主.

表1 集成电路芯片分类

3 不同类型待测模块的UVM环境设计

根据表1 模块的功能分类,针对不同功能的模块,其UVM环境在结构上可以选取适合其功能的结构.

3.1 总线协议模块

总线协议的模块主要功能是完成数据的传输,一般按照功能分为CPU周边总线、串口协议、高速接口等.总线协议类模块主要设计transaction,在driver中实现传输协议.Reference model功能简单,scoreboard主要对transaction中的member进行比对.下面以AMBA总线APB转AHB模块和SPI串口模块为例,介绍总线协议模块的UVM环境结构.

AMBA总线主要以APB,AHB,AXI等总线协议为主,其验证环境的特点是根据协议抽取transaction,环境中reference model仅仅做简单的协议转换,reference完成transaction中member的比对.本文以一款APB转AHB的总线转换模块为例,介绍其验证环境.

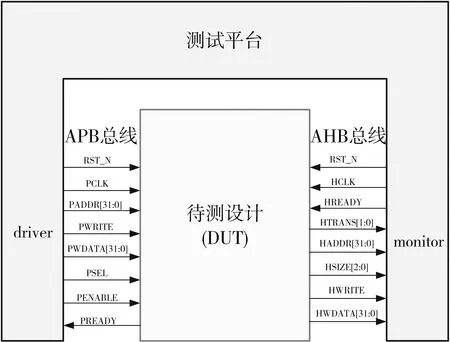

该模块的功能主要是将APB总线协议输入的数据转换为AHB总线协议的输出.待测模块与测试环境的信号级接续如图2 所示.

图2 待测模块与测试环境信号级连接

从总线协议上可以看出,比较重要的事务级信息为访问的地址、访问的数据以及访问的读写类型.因此,将上述3个内容抽取为事务级的成员.

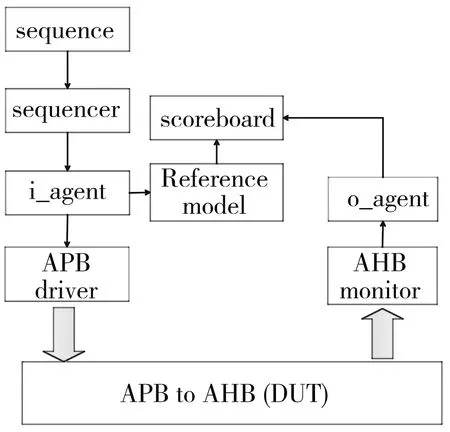

图3 为UVM验证环境结构图,环境的driver根据transaction内容,按照APB总线协议驱动各个信号,完成信号级到事务级的转换,待测模块根据输入进行动作,monitor根据AHB总线协议,监视待测模块输出,完成信号级到事务级的转换.在这个验证环境中,由于双方的事务级成员一致,因此,不需要reference model完成特定功能,只需要将i_agent中的transaction送给scoreboard即可,Scoreboard则是直接比对reference model和o_agent中的transaction内容即可.

图3 APB to AHB UVM验证环境结构

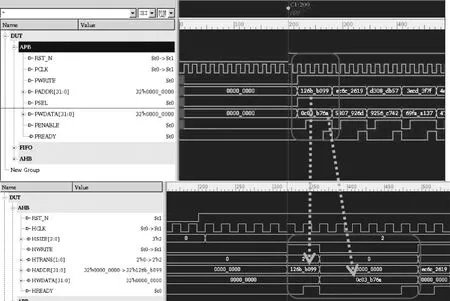

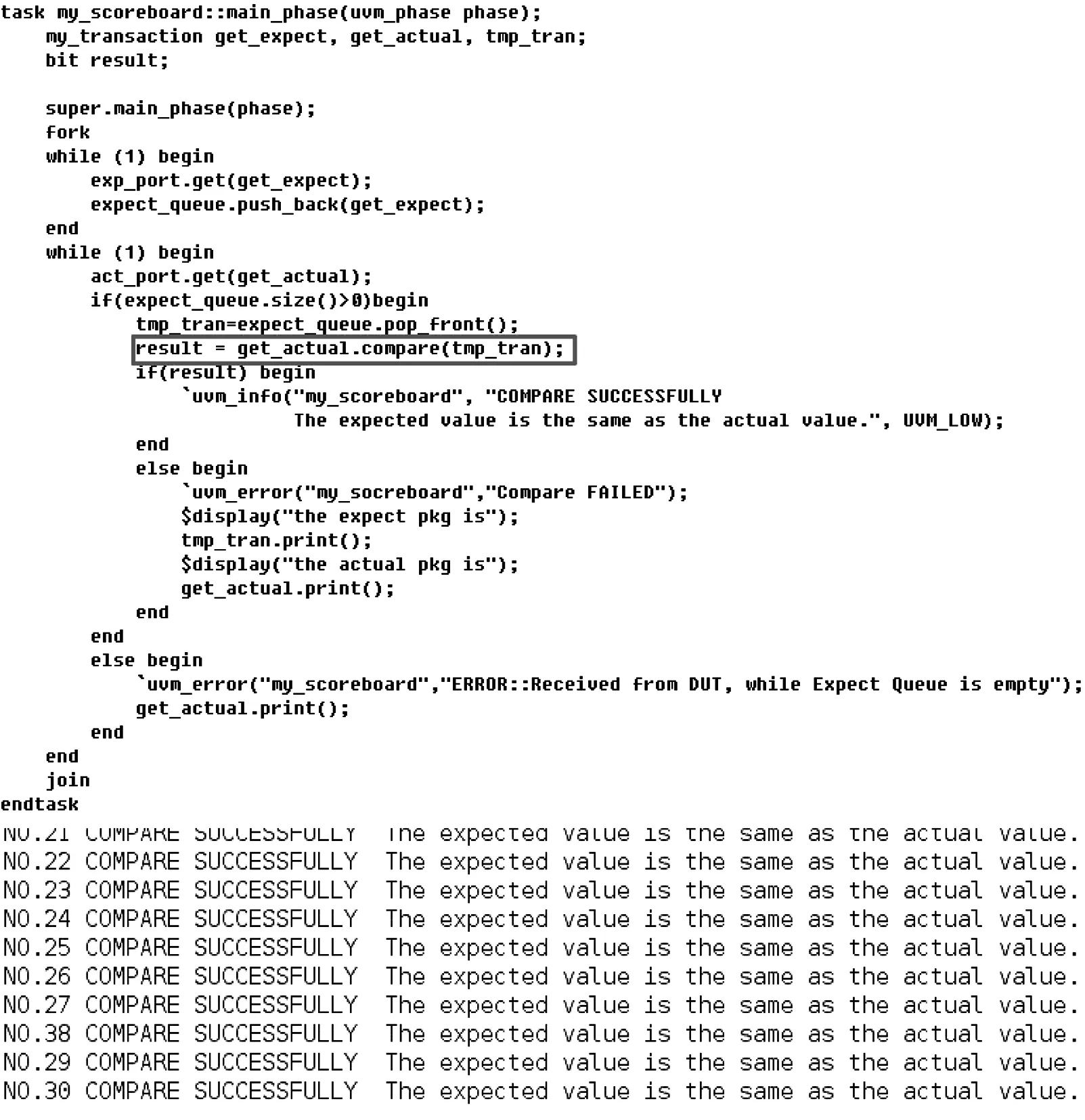

由图4 APB和AHB仿真波形可以看出,APB侧发出的向地址0x126b_b099中写入0x0c03_b76a数据的访问可以在AHB侧被正确送出.Scoreboard将完成两边transaction的比对.图5 给出了scoreboard中比对的代码和正确比对的信息.当transaction不匹配的时候则会将两边transaction中的member信息打出,以便于进一步分析.图6 为UVM_ERROR,UVM_FATAL等信息,以判断本次仿真结果的正确性.

图4 APB与AHB协议波形

图5 scoreboard 代码和比对信息

图6 UVM仿真报告

集成电路芯片中,串口协议使用很多,一般以SPI,I2C,UART等为主[12].这一类总线的特点是模块一侧是串行总线,另一侧是并行总线,可以对串口数据进行一次性的读写访问.下面以SPI为例介绍这类模块的验证环境结构.

图7 是SPI通信模块的模块图.如前所述,串行数据通过MOSI和MISO进行传输.并行数据通过Data_in和Data_out进行访问.

图7 SPI模块系统框图

该模块transaction中的member主要是data和kind,也就是读写类型和数据.其验证环境结构和APB to AHB的相似,只是将driver换成SPI协议,monitor换成相应的并口协议.验证环境工作时,driver根据transaction中的kind和data驱动串口数据,同时在sequence中控制并口数据的读取或写入.Reference model功能仅仅是将i_agent中的transaction送给scoreboard.Scoreboard中直接对比reference model和o_agent中transaction的data和kind即可.

通过大量随机测试case结合UVM仿真报告结果判断被测模块功能是否正常,通过覆盖率报告判断被测模块功能是否测试完全.图8 为SPI的总体覆盖率结果报告.

图8 总体覆盖率

3.2 算法类模块

在数字电路中根据电路实现的功能不同,存在大量的算法模块.例如图像处理中的滤波模块、灰度处理模块、信号处理模块等.这一类模块UVM环境设计重点在reference model和scoreboard上.下面按照其reference model实现方式分别进行介绍.

3.2.1 C语言实现reference model

C语言提供大量的数学运算函数,当被测模块是实现某种算法,且用C语言或systemC比较容易实现的时候,Reference model即可考虑用C来实现.其环境主要结构如图9 所示.Reference model用C来实现,环境的激励通过driver,以信号驱动的形式输入待测模块,同时以DPI调用的形式输入给reference model.待测模块和reference model根据输入进行动作,分别输出实际值文件和期待值文件,scoreboard中主要是对比两个文件,不一致的地方打出NG信息,便于验证者进行进一步分析.在实际的验证工作中,一些滤波模块会采用这种结构.

图9 C语言实现reference model环境结构

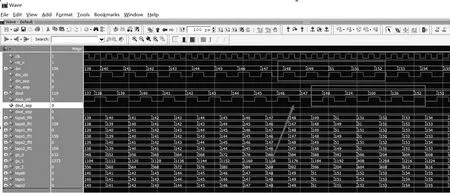

图10 为高斯滤波处理模块的仿真波形,将输入数据din的值150替换成51,输出数据从140左右变为124,100,126后再次变为152,可见进行了平滑处理.待测模块的输出会写入实际值文件.

图10 高斯滤波处理仿真波形

import“DPI”function fir(input int data_in,

outputint data_out);

验证环境中写入上述import语句.fir即为用C语言写的高斯滤波模块做reference model,完成和待测模块相同的功能.该函数根据输入数据进行处理,将数据输出到期待值文件,在driver中通过直接调用fir函数即可.scorboard中直接比对实际值文件和目标值文件.

3.2.2 Matlab实现reference model

通信芯片中有大量的信号处理模块,这些模块的设计在前期往往是通过Matlab进行性能仿真.针对这一类型模块的验证,往往reference model直接采用Matlab中的仿真数据来替代.其环境主要结构如图11 所示.由图11 可见,这类验证环境的输入即为Matlab仿真中的输入数据,driver根据驱动波形将输入数据输入到被测模块.被测模块根据输入进行动作,输出的数据会存储到一个实际值文件.reference model就是Matlab仿真的输出文件.Socreboard的功能即为比对两个文件中的数据.

图11 Matlab实现reference model环境结构

在实际的通信芯片中,峰值变换和数字失真补正等模块验证环境采用上述结构的较多.

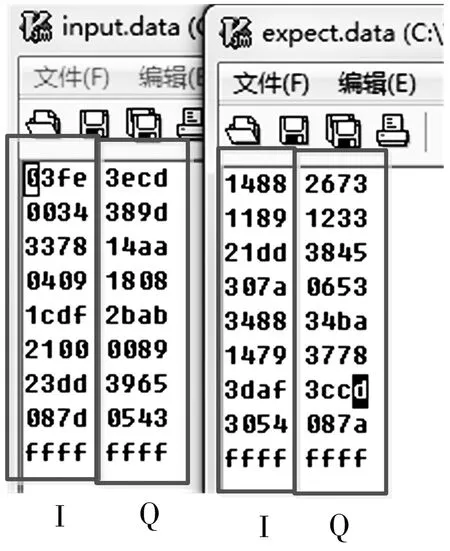

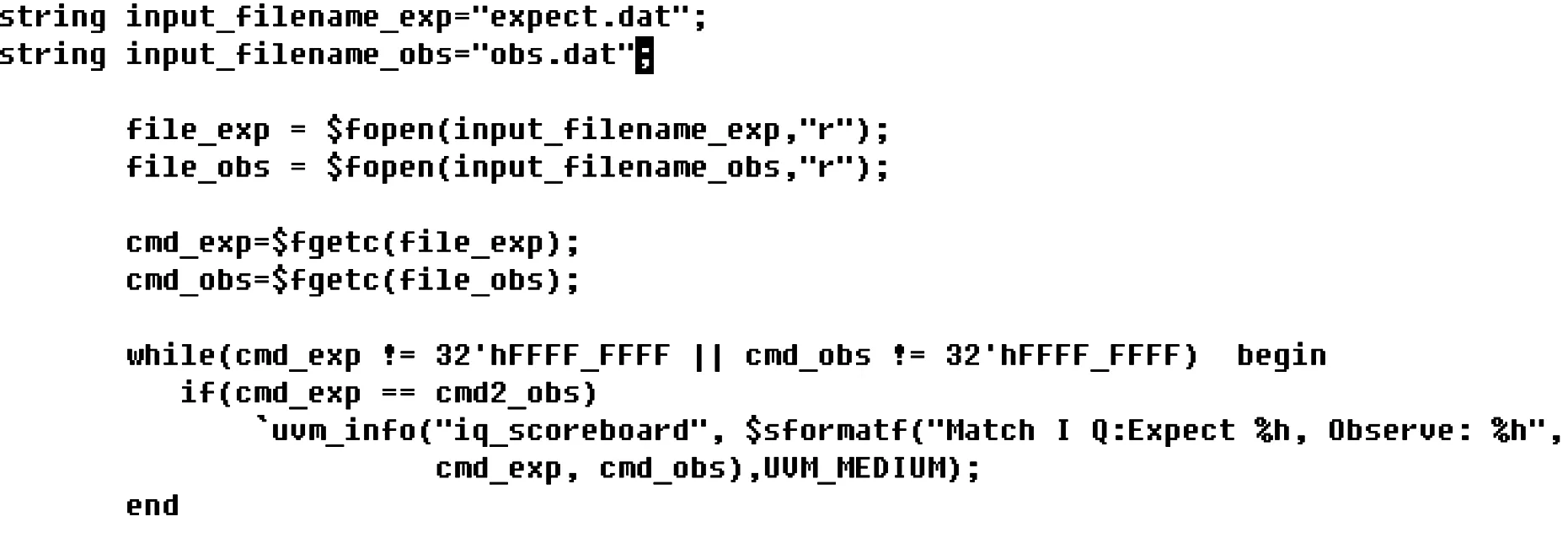

以通信处理芯片中的数字失真补正模块为例,该模块输入为14 bit的IQ数据,输出为处理后的14 bit的IQ数据.数字模块设计前,会使用Matlab进行模拟仿真,如图12 所示,input.data中为Matlab输入数据,也作为待测模块的输入数据.expect.data中为Matlab模拟仿真后的数据,作为待测模块的期待值数据.UVM环境中monitor会收集待测模块的输出,写入obs.data文件中,scoreboard比对expect.data和obs.data两个文件,代码如图13 所示.

图12 输入的IQ数据和Matlab输出的IQ数据

图13 scoreboard比对IQ数据文件代码

3.2.3 Verilog实现reference model

有些算法的期待值模块采用Verilog实现比较合适,这种情况下会采用Verilog来实现reference model.这一类被测模块的验证环境采用UVM正常的结构,即将reference model用Verilog实现即可,被测模块和reference model根据driver中输入的数据分别进行动作,将输出的信息送到scoreboard中,scoreboard直接比对两者过来的transaction即可.也可根据实际模块的功能采用对比文件的形式.实际验证工作中Power测量等模块采用该结构进行验证.

3.3 控制类模块

在数字芯片中还有一类控制模块,主要控制数据的传输,这一类模块的验证环境重点在transaction和sequence的设计,下面以DMA(Direct Memory Access)控制器为例,介绍其验证环境.

DMA控制器是一种在系统内部转移数据的独特外设,可以将其视为一种能够通过一组专用总线将内部和外部存储器与每个具有DMA能力的外设连接起来的控制器.一般每个控制器有多个DMA通道,每个通道都有一组控制寄存器,进行DMA传输的配置,如源(source)地址、目标(destination)地址、地址变化形式等.除此以外会有地址总线和数据总线,进行对特定地址的数据访问.

根据DMA的功能特点,其验证环境可以在UVM整体架构的基础上进行简化,不需要reference module,图14 是DMA控制器的验证环境结构图.验证环境首先根据sequence对待测模块进行控制寄存器的配置.待配置结束后,DMA控制器根据配置信息对source和destination 分别进行访问,source和destination由BFM(Bus Function Model)实现.

图14 DMA控制器验证环境

DMA控制器功能主要是将源地址中的数据送入到目标地址当中,其transaction中member主要是地址、读写类型和数据,其验证环境不需要特殊提供reference model.scoreboard中实例化两种checker,xact checker用来比对地址和读写类型;payload checker 用来比对数据、比对信息,如图15 所示.

图15 DMA控制器scoreboard比对信息

4 结 论

本文针对数字芯片中不同功能的验证模块:总线协议类模块、算法类模块、控制类模块分别给出其典型的UVM验证环境结构.

1)总线协议类模块的reference model主要按照协议完成transaction的统一处理,scoreboard直接比对transaction中数据即可

2)算法类模块reference model可以选择Matlab生成期待值文件、C语言生成和Verilog语言生成3种形式.前两种scoreboard主要比较文件数据.后者比对transaction数据.

3)控制类模块不需要reference model,scoreboard细化为地址和读写类型比对的xact checker和比对数据的payload checker,在其中直接比对transaction数据.

在验证前期环境架构设计阶段可以直接选择相应的环境结构,从而节省系统结构的设计时间.