一种机载雷达信号处理机实现方法

2022-03-31王亚祥

王亚祥

(南京电子技术研究所 江苏省南京市 210039)

随着无人机、飞艇等无人装备在军事领域的快速发展,无人装备凭借着高机动、低成本、长航时、零伤亡等优势被广泛应用到现代战争中。随之而来的是基于无人装备的雷达的广泛研制与使用。该种雷达集成对空/对海探测跟踪、战场实时监测、成像识别、地图测绘等功能。针对越来越复杂的战场环境,相对应的处理算法也越来越高,同时要求雷达信号处理机能够在极端时间内完成大数据量的浮点数运算,这些数据和算法都需要通用性强、性能优异的高速信号处理机来支撑实现。

随着计算机和电子元器件技术的飞速发展,数字信号处理方法和理论研究以及信号处理机的研究已经成为众多领域的热门研究基础,信号处理机被广泛应用与通信、自动化控制、航空、航天、航海等各个领域。然而,在数字信号处理机功能及性能日益齐全的今天,信号处理机的实现原理、组成结构等也愈来愈复杂,信号处理机的功耗和体积也自然而然的不断增加,这些因素和结果都会对信号处理机乃至整个电子任务系统产生十分严重的影响。因此,如何找到信号处理功能性能与体积功耗之间的平衡点,正在成为整个电子通信领域不可忽视的热点。

由以上不难看出,无人机载雷达对于雷达信号处理机在高集成、高性能、低功耗等方面提出了更高的要求。但是目前机载预警雷达信号处理领域通用架构虽然具备高性能、高可靠性等诸多优点,但该种架构在功耗和重量两方面无法满足无人机载雷达对于低功耗、轻质化的要求。本文通过对比分析5 种常见的雷达信号处理机实现方案,选用了基于DSP+PFGA 的处理架构方案,该种架构集成度高、通用性强、开发周期短,可满足无人机载雷达的轻质化、高性能、低功耗要求且具备很强的推广性和应用扩展功能。

1 常见雷达信号处理机实现形式

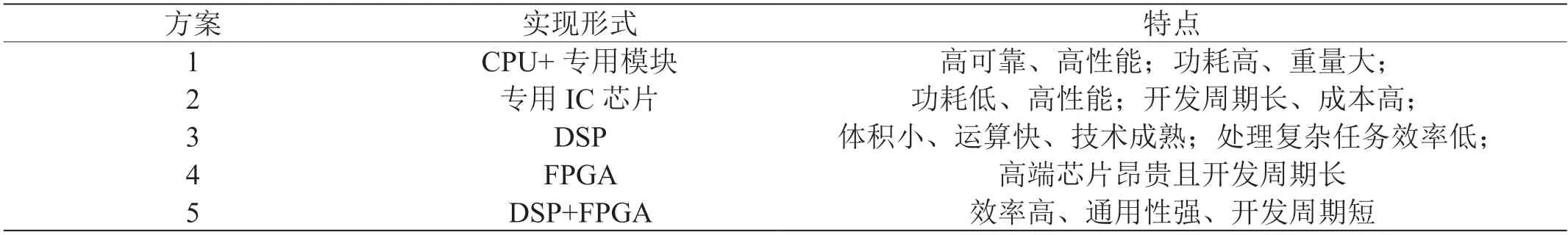

随着现场可编程口阵列(FPGA)和数字信号处理器(DSP)的制造工艺与技术的不断提高,信号与系统理论、数字信号处理理论的研究不断深入,雷达信号处理机正逐渐向全数字化、小型化发展。近年来,常见的雷达信号处理机主要有以下5 种实现方案:

1.1 基于高性能CPU+专用处理模块

该种方案可实现多路宽窄带高速数据接入及信号处理,可实现全系统SRIO 互联和以太网交换。常规的信号处理机箱采用通用处理架构,按模块功能划分,需要通用处理模块、专用处理模块、信息处理模块、数据交换模块和交换模块等至少5 种类型,再加上机箱的背板、机箱二次电源、机箱箱体及配套的各种光纤电缆等物品,形态上通常是以机箱的形式呈现。以模块数量来计算,少则5-6 块,多则15-16 块,甚至多个机箱一起完成系统的某项既定任务,重量达数十上百千克,功耗则以千瓦为记。虽然该方案稳定可靠、性能优异,但该种架构中使用的信号处理机箱的功耗和重量均超出无人平台可承受能力;

1.2 基于专业IC芯片

该种实现方案是针对雷达具体用途的算法,专门开发一款与算法相匹配的芯片。该方案可以极好的控制雷达信号处理机和芯片的功耗、性能及处理速度,但是该类芯片普遍存在开发周期长、开发成本高等特点,并且在功能应用上欠缺灵活多变性。

1.3 基于单片或多片DSP

DSP 芯片高密度集成定浮点运算单元及寄存器,其体积小、运算快、结构通用等特性使它成为完成复杂信号处理算法的极佳选择。DSP 的主要特点如下:

(1)配备独立的乘加运算单元及特殊指令,适合矩阵运算、滤波算法、FFT 以及其他信号处理运算。

(2)DSP 内部拥有独立的地址和多种总线,能够同时完成取地址和取数操作,信号处理效率很高。

(3)DSP 芯片的每条指令都由多个单元并行执行,程序运行的效率和速度得以提升。

(4)DSP 芯片自带DMA 控制器、外部存储器以及存储器扩展接口,可配合其他通信接口完成大数据快速传输。

在工程实现上,虽然DSP 可以实现复杂算法,且技术成熟,但是如果在诸如成像等领域需要处理大数据量、复杂任务的时候,数据处理时间长、数据率低,会造成很严重的资源浪费。而且,DSP 指令更适合实现算法而不是逻辑控制,对雷达系统的控制显得不够灵活。

1.4 基于FPGA架构

随着现场可编程逻辑器件FPGA 器件性能的不断提升,高端FPGA 不仅拥有百万级的逻辑门数量、大量的I/O 接口资源,还内嵌了许多处理器软核和DSP 内核,可以协助或代替DSP 实现一些需要大数据量的算法实现。但是由于高端FPGA 产品价格昂贵且国产化进程相对较慢,出于成本和软硬件调试周期等方面的考虑,单独使用FPGA 完成信号处理的情况十分少见。

1.5 基于DSP+FPGA架构

该种架构下,FPGA 可以完成大规模复杂流水运算操作,在大数据量的高速传输方面是DSP 无法比拟的。采用DSP+FPGA 的架构可以使DSP 的高速数据处理性能与FPGA 的高速数据采集、逻辑的控制能力相结合,互补两者之间的不足之处。如表1所示。

表1:雷达信号处理实现方法对比

基于以上分析,从研发成本、工程实现等角度考虑,本文选用FPGA 和DSP 相结合的系统架构,充分发挥可编程逻辑器件FPGA 和数字信号处理器DSP 的各自优势,该种系统结构灵活、实时性强、成本较低且功耗热耗较低,能满足无人机载雷达信号处理的性能需求。

2 信号处理机设计

2.1 DSP芯片选型

及上一代商用信号处理板及军事装备中大都采用的DSP是ADI 公司的TS201。随着高数据率、大数据量、复杂运算等功能需求在雷达系统中逐步发展,单核DSP 显然不能满足高速处理性能的要求。信号处理机升级改进所面临的迫切需求主要体现在两个方面:一是对单片DSP 的处理能力要求越来越高,二是对处理器(或IC 芯片)之间的拓扑结构和通信方式提出了更高的需求。

ADSP-TS201 采用超级哈佛结构,静态超标量操作适合多处理器模式运算,可直接构成分布式并行系统和共享存储式并行系统。ADSP-TS201 的主要性能指标如下:

(1)最高工作主频600 MHz(1.67 ns 指令周期);

(2)支持IEEE 浮点格式32 bit 数据和40 bit 扩展精度浮点格式。同时支持8/16/32/64 bit 的定点数据格式;

(3)允许128 bit 的数据、指令和I/O 端口访问,内部存储器带宽33.6 GB/s;

(4)32 bit 的地址总线提供4 G 的统一寻址空间;

(5)14 通道的DMA 控制器支持硬件和软件中断,支持优先级中断和嵌套中断;

(6)4 个全双工LINK 端口支持最达500 MB/s 的传输速度;

(7)JTAG 仿真接口允许多片DSP 仿真。

ADSP-TS201 处理器由处理器核和IO 接口两部分组成。其中处理器核由两个计算块、两个整型算术逻辑单元、程序控制器组成。IO 接口由内部存储器、外部设备接口、14通道的DMA 控制器、全双工的LVDS 链路口、IEEEll49.1JTAG 接口组成。内部存储器为24 Mb DRAM,外部设备接口包括SDRAM 控制器、EPROM 接口、主机接口、多处理器接口。

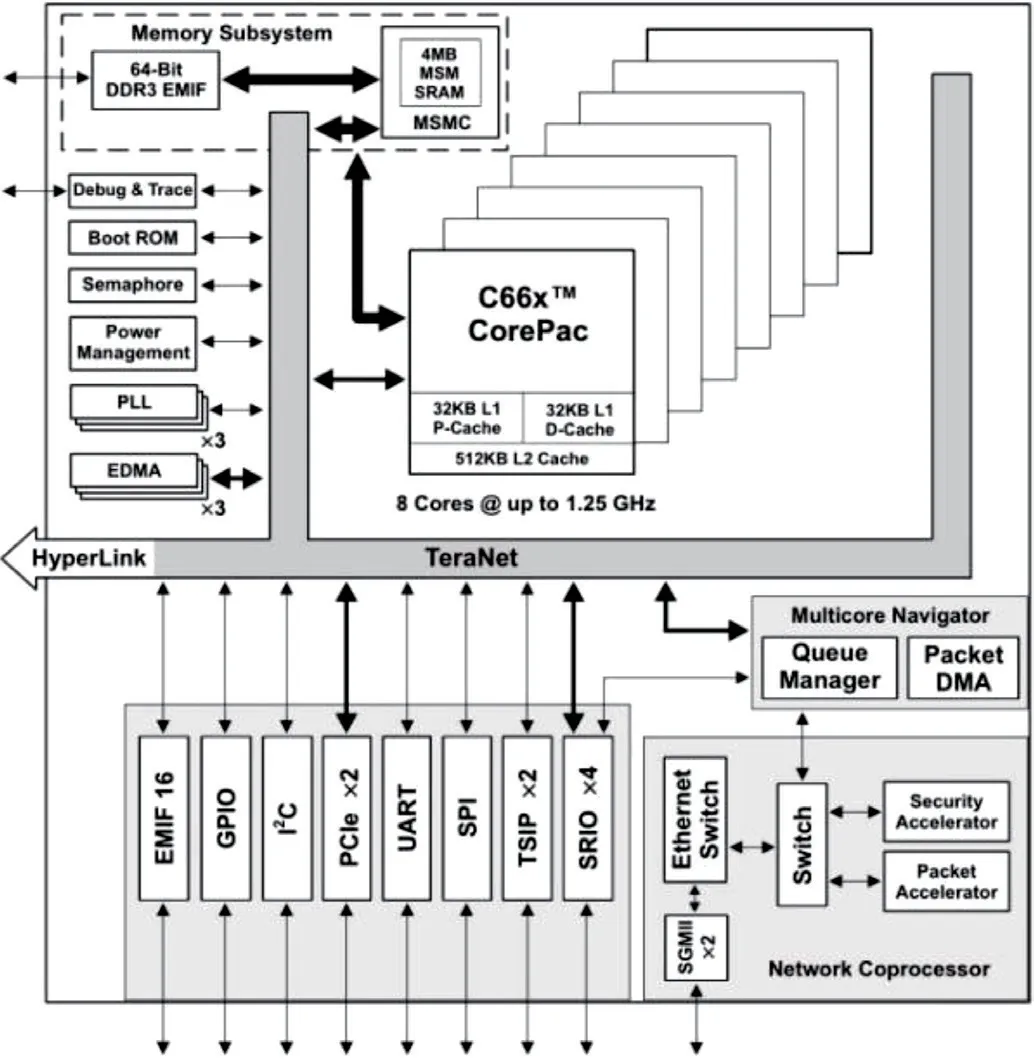

本文选用TI 的高性能定浮点数字信号处理器TMS320 C6678 作为系统处理核心。它主要特点如下:

(1)集成了8 个内核,内核频率最该可达1.25GHz;

(2)8 核并行处理速度最高可达160GFLOP;

(3)芯片每个内核有32KB L1D、32KB L1P、512KB L2 和4096KB 的多核共享存储器;

(4)芯片集成了大量的高速串行接口,包括SRIO、PCIe 等。

(5)X4 的SRIO 速率高达20Gbps,以太网接口最高支持1000Mbps 的传输速率;

TMS320C6678 是基于KeyStone 架构的DSP 处理器,拥有8 个core,每个CorePac 核的频率最高可达1.25 GHz,可以提供强大的定点和浮点运算能力,同时芯片内部集成了Multicore Navigator、RapidIO、千兆以太网和EDMA 等外设。由于芯片处理能力强,外设功能丰富,而且片内集成了大量的硬件加速器,例如Packet Accelerator、Multicore Navigator等,可以广泛地应用在通信、雷达、声纳、火控、电子对抗等领域。图1 是C6678 的内部构造图 。

图1:C6678 的内部构造图

TMS320C6678 有8 个C66x 核,典型运行速度是1GHz。每个核配置为:32KB Level 1 Data SRAM,它和DSP 核运行在相同的速度上,可以被用作普通的数据存储器或数据cache;32KB Level 1 Program SRAM,它和DSP 核运行在相同的速度上,可以被用作普通的程序存储器或程序cache;512KB LL2 SRAM,它的运行速度是DSP 核的一半,可以被用作普通存储器或cache,既可以存放数据也可以存放程序。所有DSP 核共享4MB SL2 SRAM,它的运行速度是DSP 核的一半,既可以存放数据也可以存放程序。

一个64-bit 1333MTS DDR3 SDRAM 接口可以支持8GB外部扩展存储器。C6678 集成一个64-bit 1333MTS DDR3 SDRAM 接口,可以支持8GB 外部扩展存储器,既可以存放数据也可以存放程序。它的总线宽度也可以被配置成32 bits 或16 bits。存储器访问性能对 DSP 上软件运行的效率是非常关键的。在 C6678 DSP 上,所有的主模块,包括多个DSP 核和多个DMA 都可以访问所有的存储器。

每个DSP 核每个时钟周期都可以执行最多128 bits 的load 或store 操作。在1GHz 的时钟频率下,DSP 核访问L1D SRAM 的带宽可以达到 16GB/S。当访问二级(L2)存储器或外部存储器时,访问性能主要取决于访问的方式和cache。每个 DSP 核有一个内部 DMA (IDMA),在 1GHz 的时钟频率下,它能支持高达 8GB/秒的传输。但IDMA 只能访问L1 和LL2 以及配置寄存器,它不能访问外部存储器。

DSP 的内部总线交换网络,TeraNet,提供了C66x 核 (包括其本地存储器),外部存储器,EDMA 控制器,和片上外设之间的互联。总共有 10 个 EDMA 传输控制器(用于快速数据交换)可以被配置起来同时执行任意存储器之间的数据传输。

芯片内部有两个主要的TeraNet 模块,一个用 128 bit 总线连接每个端点,速度是DSP 核频率的1/3,理论上,在1GHz 的器件上每个端口支持 5.333GB/秒的带宽;另一个TeraNet 内部总线交换网络用 256 bit 总线连接每个端点,速度是DSP 核频率的1/2,理论上,在1GHz 的器件上每个端口支持16GB/秒的带宽。

TS201 与C6678 相比,在运行速度、存储器容量、功耗等性能上都远远落后。

2.2 FPGA芯片选型

FPGA 的选型主要考虑以下因素:

(1)高速串行互连接口包括SRIO、PCIe、以太网接口等;

(2)芯片内部集成及DSP 运算核数量和性能;

(3)可外接DDR3 或DDR4,支持FPGA 进行海量数据的处理和存储;

(4)逻辑资源及IO 资源。

UtraScale Plus 系列是Xilinx 公司于2017年推出的新一代超强性能FPGA,VU9P 是该系列的一种中高端型号。该种型号FPGA 芯片采用16nm 工艺,相比前面几代产品,具备更高的接口带宽和缓存带宽,同时也内嵌了更强的DSP计算单元和存储单元。VU9P 的主要性能指标如下:

(1)逻辑单元数:2586K;

(2)内部RAM:400MB;

(3)DSP 处理单元数:6840 个;

(4)高速通道数(GTY):120 路,单通道最高支持32.75Gbps;

(5)PCIe 通道:支持6 个PCIe3.0×16 通道;

(6)支持100GE 以太网互联;

(7)DDR:支持多通道DDR4,理论速率可达3200 MT/s。

目前市面上常用的X7V690 的性能指标如下:

(1)逻辑单元数:693K;

(2)内部RAM:50MB;

(3)DSP 处理单元数:3600 个;

(4)高速通道数(GTX):96 路,单通道最高支持28.05Gbps;

(5)PCIe 通道:支持PCIe3.0*8 通道;

(6)DDR:支持多通道DDR3,理论速率可达1833 MT/s。

从以上指标可以明显看出,XCVU9P 相较于V7:

(1)逻辑单元增加了近3 倍;

(2)RAM 资源增加7 倍;

(3)DSP 处理器单元增加了近1 倍;

(4)可控制存储部件从DDR3 升级到DDR4,最大接口速率既生了1 倍。

因此,本文选用Xilinx 最新的Virtex-9 系列的FPGA。V9 作为Xilinx UtraScale Plus 系列高性能FPGA 的代表,内嵌新一代GTY serdes 接口支持25Gbps 的高速互联,其支持外挂DDR4,且DDR4 控制器最高速率可达2400MT/s。

2.3 信号处理平台设计

2.3.1 硬件设计

单单将2 款高性能处理器拼凑在一起,对整个系统的性能提升并不明显,因为系统性能的一个关键指标也是瓶颈为数据通信。如果数据通信设计出现纰漏,高性能处理器之间就不能很好的相互补充,届时不仅系统实现得不到更好的效果,反而浪费了时间、人力和物力资源。针对这个问题,同时为了最大限度的发挥两个主芯片的信号处理能力,本文再对比各种信号处理机架构后,还选用了一款Xilinx 公司的XC7Z045 作为OBC、一款ITD 公司的CPS1848 完成全系统SRIO 交换、一片BCM5396 进行全系统网络交换,用于板内所有芯片的全RapidIO 链路、全网络互联,极大的提升了数据的传输通信效率。因为RapidIO 以其传输效率高、系统成本低、系统稳定性好的特点,使其在高性能嵌入式系统中得到了广泛的应用。

经仿真分析及合理化优化修改,最终该信号处理机的硬件资源及主要技术指标如下:

• FPGA 外挂4 簇DDR4

• FPGA 每簇DDR4 位宽64bit,容量2GB,数据速率2400Mb/s。

• FPGA 预留GPIO,TTL3V3 电平。

• DSP 处理器采用两颗TI 8 核处理器TMS320C6678。

• 每片DSP 外挂一组64bit DDR3 颗粒,总容量2GB,数据速率1333Mb/s。

• DSP 采用NorFlash 加载模式,NorFlash 容量1GB。

• 4 个芯片 之间通过SRIO x4 互联@5Gbps。

• 单电源输入12v。

该信号处理机的主要技术指标总结如表2所示。

表2:信号处理机硬件资源

如图2所示,该信号处理机的硬件设计架构的特点与创新点如下:

图2:信号处理机硬件资源框图

(1)集成了基于DSP 的通用信号处理器和超大规模FPGA 的专用硬件加速处理器,各个处理器具有独立的数据缓存和高速数据通道,形成独立的计算节点,具备一定的数据存储、信息交换和处理能力,能够独立完成计算功能。模块采用SRIO 总线构成集中星型交换结构,实现处理器之间的高带宽、低延迟的全互联数据交换,可以动态形成串联、并联、主从等各种系统互联拓扑,支持串行/并行流水线等各种处理架构,支持各种信号和数据的处理运算;

(2)计算节点能够通过动态参数配置、软件在线加载、完全或局部重载等技术手段,实现计算节点的动态可重构与可扩展。支持基于计算节点的故障或健康信息上报,隔离故障和亚健康节点,进而进行计算节点资源的动态重组;

(3)由于模块集成度高、布线密度大、电源品种多、核心电源电压低、功率密度大等特点,模块的信号完整性和电源完成性问题较为突出。通过优化电源设计,优化布局布线,信号完整性仿真分析和高速电路测试验证等手段解决模块信号完整性和电源完整性;

(4)由于模块芯片密度大,单片热耗高,对散热设计要求较高,通过热仿真分析,优化散热板设计解决模块散热问题。

2.3.2 软件设计

系统软件设计由两部分组成:DSP 软件和FPGA 软件。AD 数据预处理、杂波抑制和抗干扰在两片FPGA 中完成,目标检测和点航迹处理在两片DSP 中完成。工程应用时计算任务分配如图3所示。

图3:信号处理机计算任务分配框图

上述软件架构,实在充分分析无人机载雷达信号处理各个工作模块所需硬件资源的基础之上,充分发挥DSP 和FPGA 的优点,将工程实现与算法仿真做到了一致。该种架构流水作业处理雷达后端数据,工作过程中,每个芯片都处于运行中,也进一步最大限度的将芯片的性能发挥到最佳。

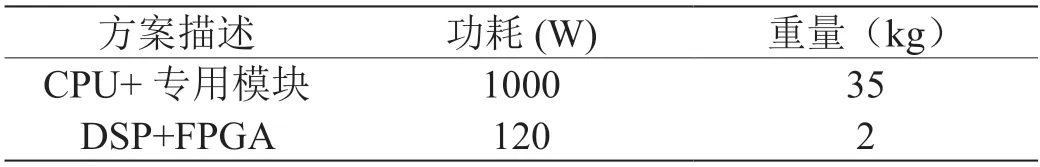

3 工程应用

如图1所示,信号处理模块上使用2 片C6678 和2 片FPGA 以保证模块的性能与功耗之间达到平衡统一。

结合无人机载雷达的实际需求,经由仿真数据上电实测,模块可实时处理单帧大小为128MB 的AD 数据,且模块的峰值功耗<120W,可满足未来无人机载预警雷达的作战需求。表3所示为本方法与目前主流的机载信号处理机在同时处理速率4Gbps 的雷达实测数据时的对比分析。

表3:方案性能对比

由表3 可以看出,本文所提出的信号处理机实现方法,在保证完成所需性能基础上,在功耗、重量等方面相比与常见的新信号处理机箱均实现了数量级的下降。

4 结束语

为了满足无人机载雷达对于信号处理的高性能与低功耗之间的平衡,且伴随着高性能FPAG 和多核DSP 有效的推动了雷达信号处理机的研发与革新,本文选用了DSP+FPGA的架构来实现。经过仿真及实测数据分析,该种架构可在百瓦功率、2 kg 量级以内实现雷达的多通道实时信号处理,比机载预警常见的机箱单元平台在功耗和重量方面均减小一个数量级,可满足当前无人机载雷达低功耗、长航时的需求。