三维集成电路集成硅通孔的应力应变研究

2022-03-29苏鹏徐鹏程秦进功王东田野

苏鹏 徐鹏程 秦进功 王东 田野

摘 要:采用有限元模拟法研究三维集成电路集成中硅通孔结构在热循环载荷条件下的失效行为,对硅通孔结构的应力应变进行分析。结果表明,硅通孔结构在热循环载荷下顶部Cu焊盘角落附近的SiO层处具有最大的应力与应变,这表明硅通孔结构中最易失效位置在顶部Cu焊盘角落附近Cu和SiO的界面处。试验结果与模拟分析一致,进一步验证了模拟结果对硅通孔结构最易失效位置分析的可靠性。

关键词:硅通孔;三维封装;热循环;可靠性;有限元分析法

中图分类号:TG454 文献标志码:A 文章编号:1003-5168(2022)4-0051-04

DOI:10.19968/j.cnki.hnkj.1003-5168.2022.04.011

Reliability Research of Integrated Through Silicon Vias in 3D Integrated Circuits-Stress and Strain Research

SU Peng XU Pengcheng QIN Jingong WANG Dong TIAN Ye

(Henan University of Technology,Zhengzhou 450000,China)

Abstract:The finite element simulation method is used to study the failure behavior of TSV structures in 3D integrated circuits under thermal cyclic loading conditions, and the stress and strain of TSV structures are analyzed. The results show that the maximum deformation amount of the TSV structure under thermal cyclic loading is located at the center of the top Cu pad, and the SiO layer near the corners of the top Cu pad has the largest stress and strain, which indicates that the TSV structure in the The most vulnerable location is at the interface of Cu and SiO near the corner of the top Cu pad. The experimental results are consistent with the simulation analysis, which further verifies the reliability of the simulation results for the analysis of the most vulnerable location of the TSV structure.

Keywords:through silicon via; 3D packaging; thermal cycling; reliability; finite element analysis method

0 引言

随着微电子产品向多功能、高密度及微型化方向迅速发展,二维电子封装已经接近摩尔定律極限,因而不能满足当前微电子产品多功能化发展的需要,基于硅通孔互连技术(Through Silicon Via,TSV)的三维集成电路封装因其高封装密度、低功耗和高运行速率从而成为最具潜力的封装方式[1-2]。TSV结构中Si芯片和Cu柱的热膨胀系数(Coefficient of Thermal Expansion,CTE)相差较大,当温度变化时,易在Si和Cu界面处产生热失配从而使得应力集中,最终导致整个三维封装结构的失效。特别是在更高密度和更微型化的电子封装中,TSV结构尺寸的不断减小使得这一可靠性问题更加严重,因此研究热循环条件下三维集成电路封装硅通孔结构的应力与应变具有极其重要的意义[3-4]。

目前,已有部分学者对热冲击条件下硅通孔材料设置及结构参数对应力应变的影响进行了研究[5-6],其中何映婷[5]研究了不同情况下不同结构TSV的热力响应,得到了不同结构尺寸以及材料组合对于TSV热力响应的影响情况。此外部分学者研究了大尺寸封装结构中TSV在热冲击条件下的应力应变[7-8],Liang等人[7]采用有限元分析(FEA)方法研究了硅各向异性对热循环载荷下TSV结构的热应力的影响,结果表明,高热应力始终位于结构中两种材料的界面处。虽然部分学者对大尺寸封装结构下TSV结构的应力应变进行了研究,但对小间距和小尺寸封装结构中TSV承受热循环条件下的应力应变研究尚不完善,对三维集成电路封装中硅通孔结构热循环条件下的应力应变、失效机理等方面仍要做进一步的研究和探索。

本研究建立了小间距互连尺寸下TSV结构的有限元模型,采用映射划分和自由划分相结合的方式划分网格,研究在热循环载荷下TSV结构的应力与应变。通过分析热循环过程中最高温和最低温时TSV结构各部位的等效应力和塑性应变,从而对可能出现的热失效问题进行预测并评估其可靠性,最终通过试验结果对模拟进行验证。

1 试验方法

TSV结构主要包括介质隔离层、扩散阻挡层和填充金属。通常情况下,介质隔离层为SiO。由于扩散阻挡层的厚度非常小,对TSV结构热应力的影响可以忽略不计,故研究中TSV结构模型不设置扩散阻挡层。

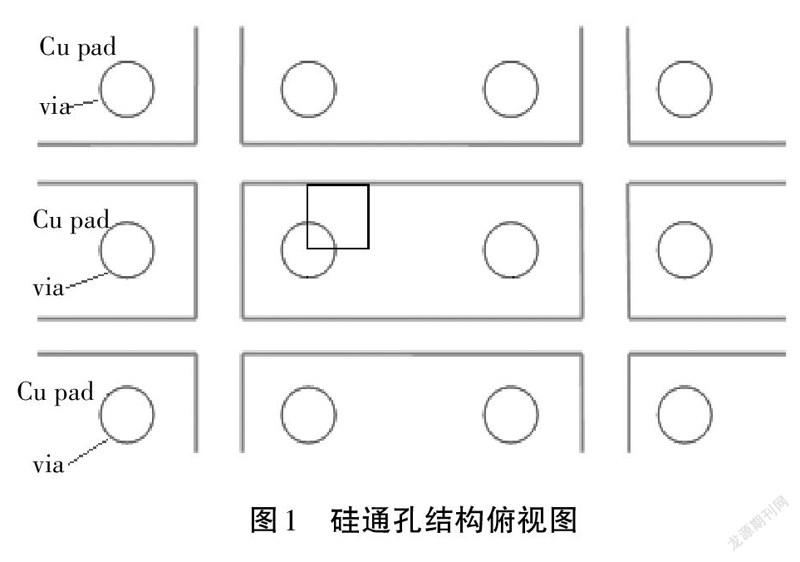

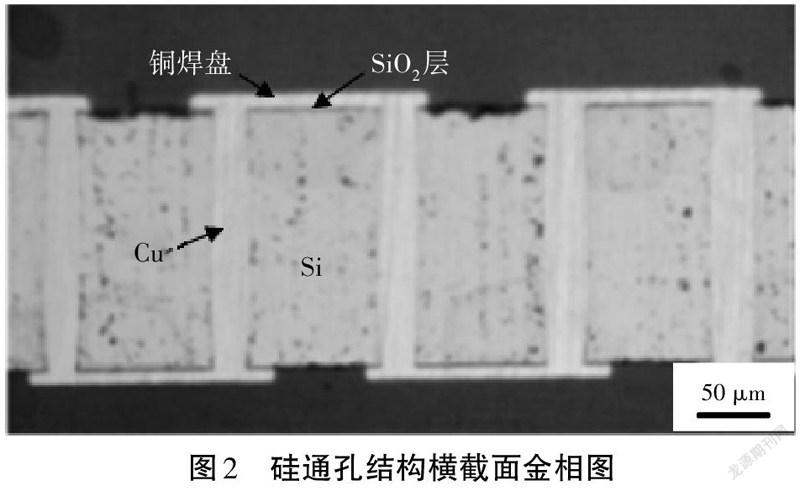

图1为TSV结构俯视图,图2为TSV结构横截面金相图。本研究TSV结构SiO层的厚度为2 μm,通孔直径为35 μm,TSV深度为100 μm,Cu焊盘厚度为14 μm,深宽比为2。热循环加载按照美国军用标准MIL-STD-883选取,温度范围为-55~125 ℃,升降温速率为12 ℃/min,高低温转换时间为3 s,高低温保持时间各15 min。硅通孔施加热循环载荷至第7个循环时应力趋于稳定,由于计算资源的限制,不可能对试验的所有循环进行模拟,为了得到更为精确的结果,设定仿真运算8个循环[9]。采用P600-P3000粒度的碳化硅水砂纸对金相样品进行磨制,再采用1 μm和0.05 μm的AlO悬浮抛光液进行最终抛光。采用扫描电子显微镜(Scanning Electronic Microscopy,SEM)对硅通孔结构横截面进行观察。

2 模型的建立及参数的选择

2.1 模型的建立和单元划分

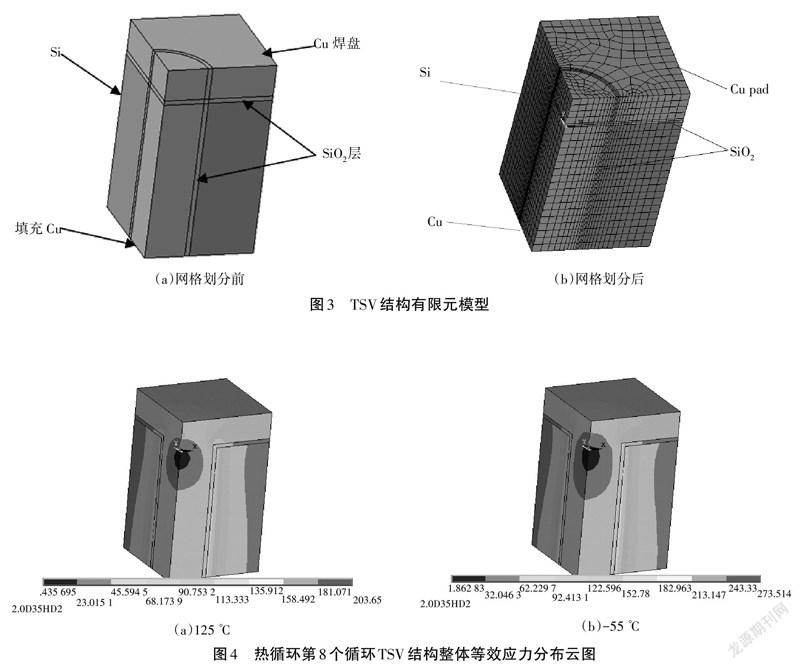

由图1可知,各个硅通孔的结构完全相同且呈周期性排列。为了便于分析,选取单个硅通孔的1/4为研究对象进行模型建立和单元划分,即图1中黑色方框中的部分。图3(a)为单个硅通孔1/4结构的几何模型示意图。

由于TSV结构各个部位所产生的应力与应变不同,要求的计算精度也不一样,因此采用映射划分方式和自由划分方式相结合的办法来进行网格划分。在Si和Cu相接触的部位,由于Si和Cu极易因热失配产生较大的热应力,是易对TSV结构可靠性产生影响的关键部位,故采用映射划分的方式,可提高计算精度并对TSV结构的应力应变进行定量分析。其他部位由于产生的热应力相对较小且要求的计算精度不高,因此采用自由划分的方式来缩减计算的时间。此外由于Si和Cu界面处的热应力较大,在Si和Cu的界面处的网格划分密度大于其他部位以获得更为精确的计算结果,图3(b)为网格划分之后TSV结构的有限元模型。

2.2 参数的选取及载荷的施加

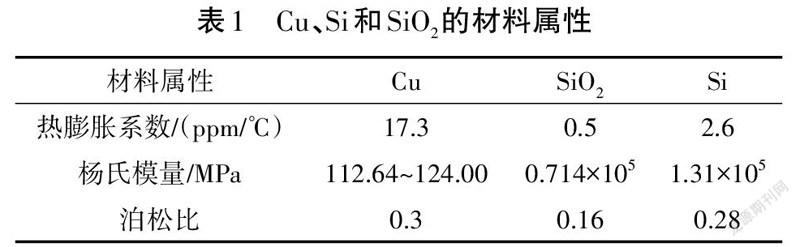

TSV结构的有限元模型主要涉及3种材料:Si、Cu和SiO,表1为Cu、SiO和Si的材料属性。由于Si材料在所有工作过程中只发生弹性变形,故采用线弹性材料本构模型描述Si材料在热循环条件下的变形行为。Cu采用服从于von Mises屈服准则的多线性随动强化材料本构模型,描述其在热循环载荷下的金属塑性行为,Cu材料的杨氏模量值随温度变化而变化,TSV结构的其他材料参数受温度影响较小,因此假定其他材料参数不变。

3 计算结果与讨论

3.1 热循环下TSV结构应力与应变分析

热失配引起Cu和Si形变量不同而导致的应力集中是TSV结构失效的主要原因,因此分析硅通孔结构在热循环载荷下的应力变化具有重要意义。图4为热循环第8个循环时封装结构的整体等效应力分布云图。由图4可知,TSV结构在热循环载荷下整体应力最大值位于顶部Cu焊盘角落附近的SiO层,整体应力最小值位于填充Cu柱与顶部Cu焊盘交界面的中心处,TSV结构整体应力的变化趋势是:从TSV结构顶部Cu焊盘角落附近的SiO层向四周逐渐减小。

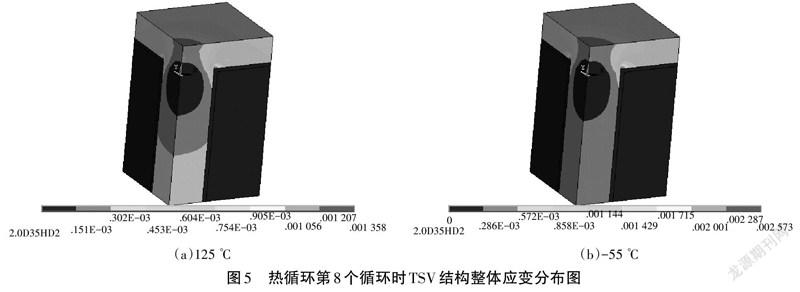

图5为热循环第8个循环时TSV结构的整体等效应变云图。由图5可知,TSV结构在热循环载荷下整体应变的变化趋势是:从TSV结构顶部Cu焊盘角落附近的SiO层向四周逐渐减小,最大值位于顶部Cu焊盘角落附近的SiO层。

3.2 最易失效位置试验验证及分析

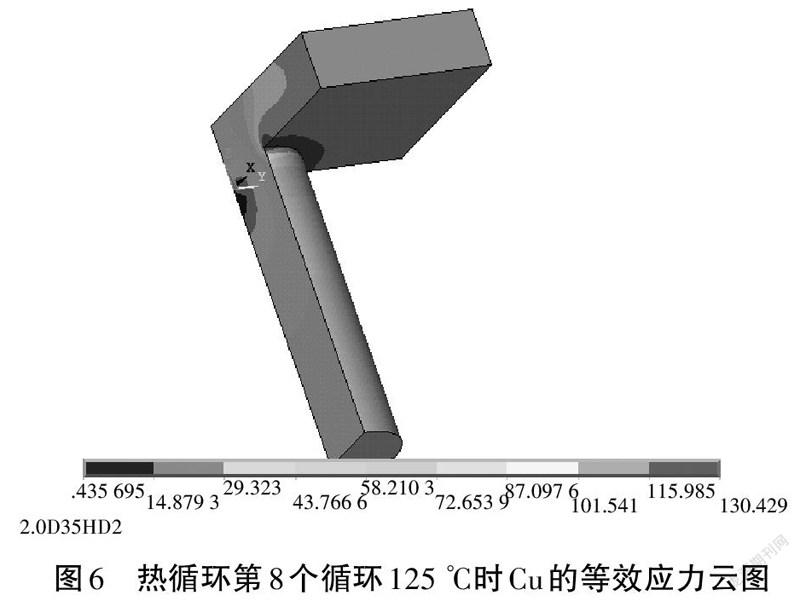

图6为热循环第8个循环125 ℃时Cu的等效应力云图。由图6可知,热循环载荷下TSV结构中Cu的等效应力最大值位于TSV结构顶部Cu焊盘角落附近Cu和SiO的界面处,这与热循环条件下TSV结构应力与应变分析的结果相同。

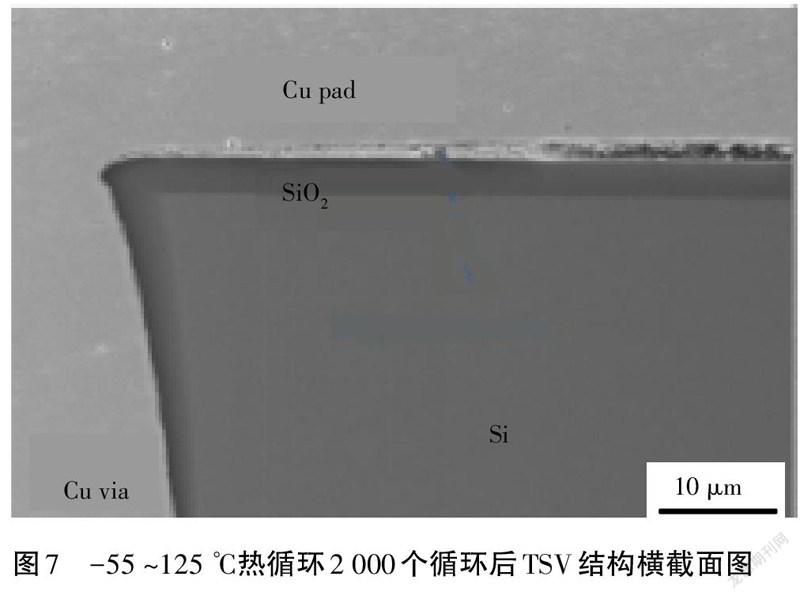

分析以上结果可以得出结论,封装结构中最易失效位置在TSV结构顶部Cu焊盘角落附近Cu和SiO的界面处。这是因为在热循环过程中,Si和Cu的热膨胀系数相差较大,Cu的膨胀使SiO层受到轴向的拉伸应力和径向的压应力。因此,如果该界面处的Cu失效,则TSV结构整体将失效。图7为-55~125 ℃热循环2 000个循环后TSV结构横截面扫描电镜图,通过对试验样品的观察,可以看出裂纹萌生的位置为Cu焊盘和SiO的界面处,从而验证了以上模拟结果的正确性。

4 結语

在热循环载荷下,TSV结构整体等效应力与应变的最大值位于TSV结构顶部Cu焊盘边角附近的SiO层处。TSV结构中最易失效位置在TSV结构顶部Cu焊盘角落附近Cu和SiO的交界处,即热循环导致的裂纹易在Cu焊盘和SiO界面处形成,该试验结果与模拟分析结果一致,因此该位置为TSV结构热应力可靠性薄弱位置。

参考文献:

[1] 庞学满,周骏,梁秋实,等.基板堆叠型三维系统级封装技术[J].固体电子学研究与进展,2021,41(3):161-165.

[2] 周健,周绍华.3D封装与硅通孔(TSV)技术[J].中国新技术新产品,2015(24):13.

[3] 王硕,马奎,杨发顺.TSV可靠性综述[J].电子技术应用,2021,47(2):1-6.

[4] 张宁.三维集成中的TSV技术[J].集成电路应用,2017,34(11):17-22.

[5] 何映婷.基于电-热-力耦合的TSV热力响应研究[D].西安:西安电子科技大学,2017.

[6] 袁琰红,高立明,吴昊,等.硅通孔尺寸与材料对热应力的影响[J].半导体光电,2013,34(2): 255-258.

[7] LIANG J, NING M, DING C, et al. The effect of silicon anisotropy on the thermal stress of TSV structure of 3D packaging chip under thermal cyclic loads[C]//2021 22nd International Conference on Electronic Packaging Technology (ICEPT),2021: 1-4.

[8] 宋培帅,何昱蓉,魏江涛,等.三维封装TSV结构热失效性分析[J].电子与封装,2021,21(9):13-18.