基于龙芯处理器的继电保护装置平台及关键技术

2022-03-17李友军周华良徐广辉戴欣欣罗华煜

李友军,周华良,徐广辉,戴欣欣,罗华煜,夏 雨

(1. 南瑞集团(国网电力科学研究院)有限公司 智能电网保护和运行控制国家重点实验室,江苏 南京 211106;2. 国电南瑞科技股份有限公司,江苏 南京 211106)

0 引言

继电保护是电网稳定运行的核心二次设备,须保证在任何条件下都能稳定供应和正常运维,设计开发自主可控的继电保护装置符合当前实际应用需求。

芯片选型,特别是处理器芯片选型及自主可控程度的定义是开发自主可控的继电保护装置首要面临的问题。其次单板件或整装置无缝替换在运装置的需求应优先满足,确保电网的战略备用安全。从技术成熟度角度考虑,自主可控继电保护装置平台应向保护专业提供一致兼容的接口,使业务代码可直接编译使用,从而提高继电保护算法的成熟度和软件兼容性。从可靠性角度考虑,针对现有继电保护装置的可靠性已有大量的研究[1-2],开发自主可控继电保护装置平台应继承这些可靠性研究成果,保持继电保护装置的高可靠性。而国产元器件的成熟度和工程应用不足,在可靠性和一致性方面尚待完善[3-4],故需要利用整体体系优化设计弥补部件级技术性能差距,从而实现装置的整体功能和性能对标在运装置。从变电站类型角度考虑,目前在运的变电站有传统变电站、数字化变电站、智能变电站3种。传统变电站以模拟采样为主要需求;数字化变电站以采样和信息数字化为主要特征;智能变电站以数字化技术为基础,增加了功能集成化、结构紧凑化、状态可视化等主要特征[5],其核心是二次设备网络化[6]。因此继电保护装置想要适用于上述3 类变电站,必须实现接口网络化。基于进口器件的继电保护接口网络化技术已经有众多研究成果[7-10],嵌入式以太网技术也有相关学者进行了研究[11]。

当前继电保护装置大多采用分布式架构和多板卡部署[12-14]的方式设计,具有配置灵活、扩展方便的特点。本文继承已有文献的成果,基于自主可控元器件设计继电保护装置平台,并针对自主可控芯片的特点进行适配开发,且遵循兼容性、平台和应用解耦、接口网络化[15]、可靠性[16-18]等原则。本文主要从自主化芯片选型原则、平台体系架构、兼容性设计、关键代码实时性优化提升、软错误防护措施等方面详细介绍自主可控继电保护装置平台及其关键技术。由于处理器自主可控涉及领域众多,包括技术路线来源、自主设计能力、自主生产能力、持续发展能力、生态系统等,且芯片类型众多,难以逐一阐述,所以本文仅阐述处理器的自主可控选型思路,希望能对业界选型起到参考作用。

1 主控芯片选型

目前还没有业界公认的自主化芯片定义标准,在研制自主可控的继电保护装置平台时,需定义自主化芯片的选型原则。本文根据文献[19]的自主可控分级研究结果,针对最新技术进展,给出了芯片自主化分级情况,如附录A 表A1所示。当前大部分基于ARM 核开发的芯片多为知识产权IP(Intellectual Property)硬核授权,仅能根据市场需求添加外围设备,其内核为国外设计的成品,不具备缺陷修复和性能提升的条件,仅能达到部分自主化的水平(L2);国内个别企业采用基于ARM 指定版本架构授权设计的芯片,其指令集变更的权限仍由国外公司掌控,后期的发展易受国际环境变化的影响,仅能达到有条件自主化水平(L3);还有部分企业获得了指令集的永久授权,可根据自身设计需求自主升级指令集,具备高度自主化的条件(L4),龙芯中科基于MIPS 的指令体系架构和申威基于Alpha 的指令体系架构属于此类自主化水平分类;开源的RISC-V 指令体系也具有高度自主化的条件,但尚无量产的芯片,软件生态不够完善,嵌入式通用处理器芯片还处于起步阶段。上述几种指令体系架构的比较如附录A表A2所示。

从自主化水平来看,Alpha 架构和MIPS 架构的国产处理器芯片满足高度自主化(L4)的要求,而Alpha 架构的处理器主要用于服务器,不适用于嵌入式应用场景。在嵌入式处理器方面,仅有基于MIPS 架构的龙芯处理器能达到高度自主化的要求,且龙芯处理器经过多年的发展,已在军工[20]、宇航[21]、工业控制[22]等领域得到了较多应用。本文选用龙芯2K1000 处理器(下文简称为2K1000)作为电力二次设备平台的核心处理器,其采用40 nm 复杂金属半导体氧化物CMOS(Complementary Metal Oxide Semiconductor)工艺,功耗小于4.5 W,具有高速串行计算机扩展总线PCIe(Peripheral Component Interconnect express)、千兆以太网介质访问控制GMAC(Gigabit Media Access Controller)等高速通信接口,以及控制器局域网CAN(Controller Area Network)总线、通用串行总线USB(Universal Serial Bus)、集成电路总线I2C(Inter-Integrated Circuit)等低速接口,可以满足电力二次设备的嵌入式应用场景;处理器片内集成2 个64 位的双发射GS264 处理器核,主频可达1 GHz,每个核具有独立的32 KByte的一级指令缓存及一级数据缓存;另外处理器片内还集成了丰富的高速和低速外设接口,如附录A 图A1所示。

2 基于2K1000的继电保护装置平台设计

针对2K1000 的外设接口特点,本文采用PCIe高速接口外加现场可编程门阵列FPGA(Field Programmable Gate Array)扩展以太网增加站控层网络接口和过程层网络接口,实现接口网络化。各个模件通过背板总线进行数据交换,实现分布式架构的搭建。

2.1 分布式架构设计

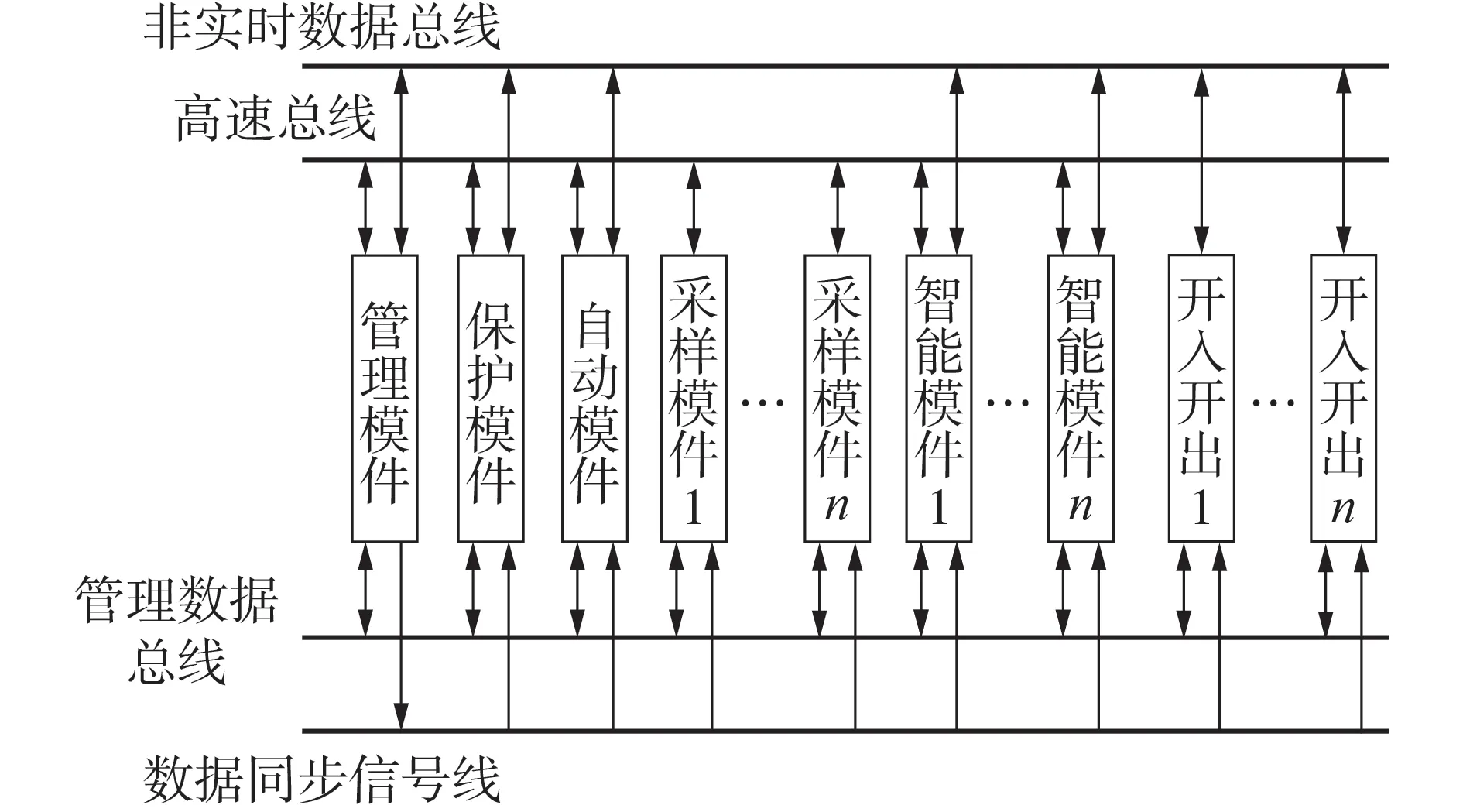

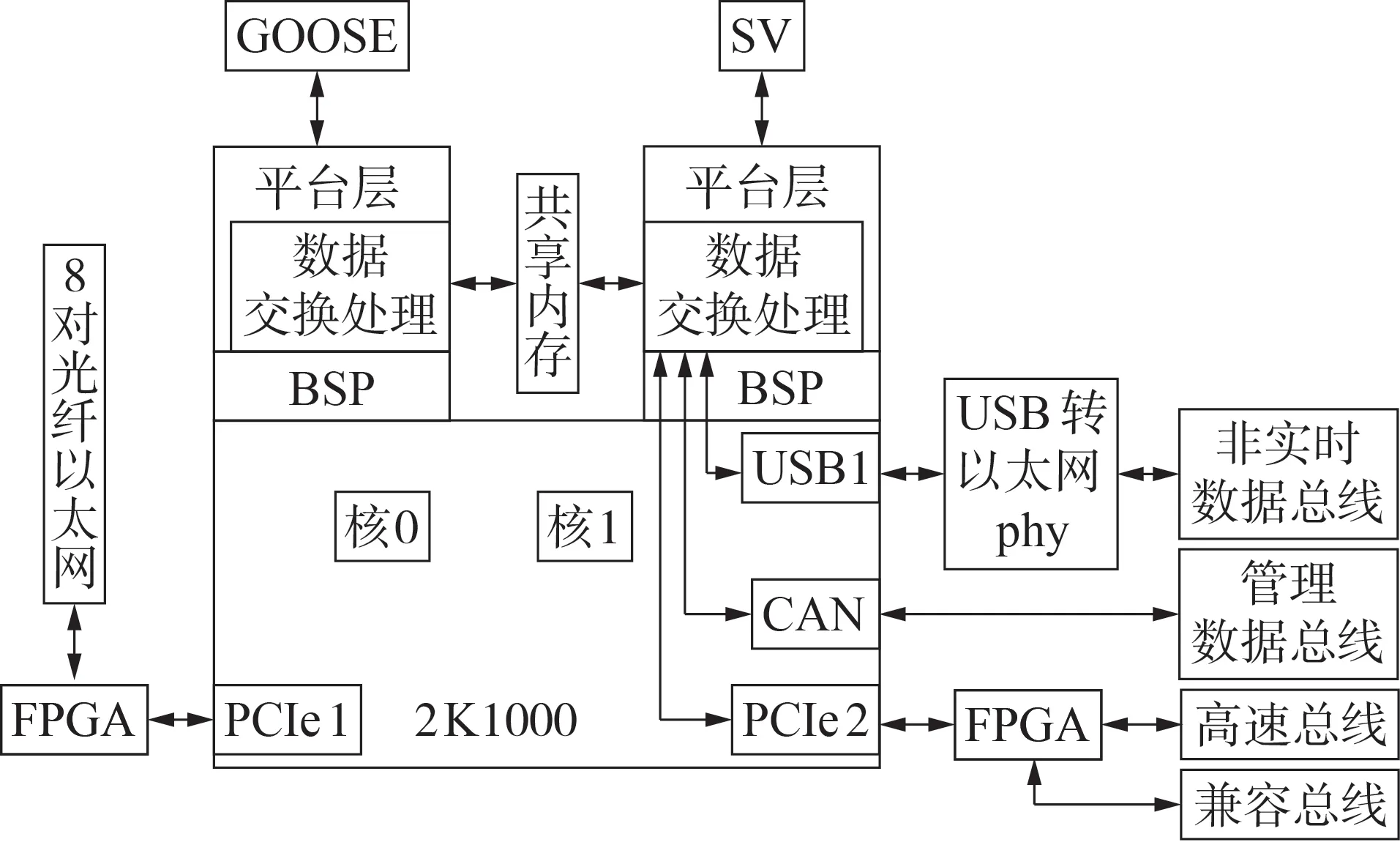

继电保护装置平台通常包括管理模件、启动模件、保护模件、智能模件、采样模件、开入开出等模件。本文采用分布式架构,所有模件均通过背板总线接入系统进行数据交换,实现数据共享和逻辑控制。基于2K1000的继电保护装置平台架构如图1所示。

图1 基于2K1000的继电保护装置平台架构示意图Fig.1 Schematic diagram of architecture of relay protection device platform based on 2K1000

平台背板上布置了高速总线、非实时数据总线、管理数据总线以及数据同步信号线。高速总线采用百兆以太网接口,主要用于传输实时数据,如采样值、实时计算量等;非实时数据总线采用USB 转以太网接口,主要传输事件顺序记录SOE(Sequence Of Event)以及模拟量的幅值、相角等;管理数据总线主要负责模件配置、参数、调试等系统管理类的数据;数据同步信号线主要用于继电保护装置平台内部各模件之间的数据同步,由管理模件发出同步脉冲,其他模件利用该信号同步自身的数据。模件根据自身功能类型选择总线类型,所有模件均接入管理数据总线和数据同步信号线,从而能够接收和响应管理模件的命令、参数等报文,并定时向管理总线发送心跳报文。另外,管理模件、保护模件、启动模件和智能模件还接入高速总线和非实时数据总线;采样模件还接入高速总线;开入开出还接入非实时数据总线。

2.2 实时数据共享方案

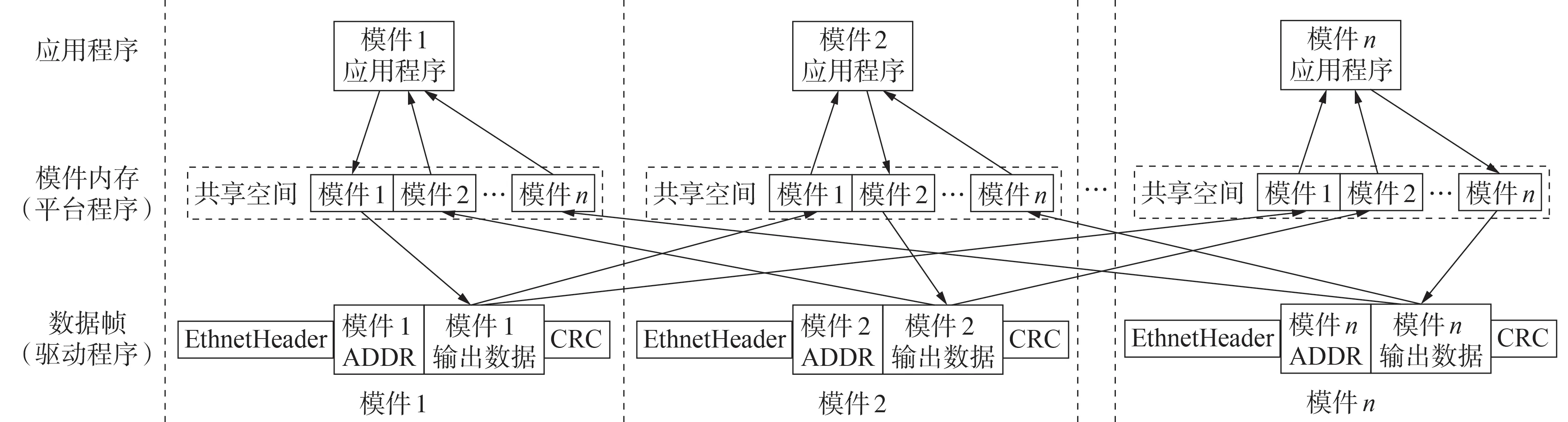

实时数据共享是继电保护装置平台各个模件进行协同计算和逻辑控制的关键。通过模件间的数据共享,保护模件、启动模件、智能模件、采样模件可以按照各自的逻辑独立运行并相互协同。模件间的实时数据交换框架示意图如图2所示。

保护模件按3 层软件架构实现,分别为应用程序、平台程序和驱动程序。模件数据共享框架也分3 层实现,分别是应用程序、内存共享空间、数据帧接收和发送。应用程序根据业务需要定义输入数据、输出数据。平台程序根据应用程序定义的输入数据源,预先申请模件的共享数据区,如图2 的共享空间中的模件1、模件2、…、模件n等空间所示,其中包含自身输出数据区。模件接收高速总线的所有数据,将数据复制到预先申请的对应共享内存空间。应用程序根据业务需要从共享内存中取数并开展逻辑计算,计算结束后将输出数据填入自身数据区。业务程序运行结束后,由平台程序将模件自身数据区通过高速总线进行广播,完成装置平台内部各个模件之间的实时数据共享。

图2 模件间的实时数据交换框架示意图Fig.2 Schematic diagram of framework of real-time data exchange between modules

保护模件获得实时的保护通道采样数据并进行计算,从而控制出口继电器。启动模件获得实时的启动通道采样数据并进行计算,从而控制启动继电器。智能模件将网口接收到的数字化采样数据通过同步和插值计算转换为模件的输出数据,并通过高速总线广播发送。采样模件获得的采样数据通过高速总线广播发送。其他模件根据自身功能通过高速总线广播实时数据。

2.3 功能模件设计

管理模件、保护模件、启动模件、智能模件等核心板卡均基于2K1000设计,其中管理模件部署开源Linux操作系统,其他几种插件基于裸核运行模式部署自主开发的简单任务调度框架。

2.3.1 管理模件

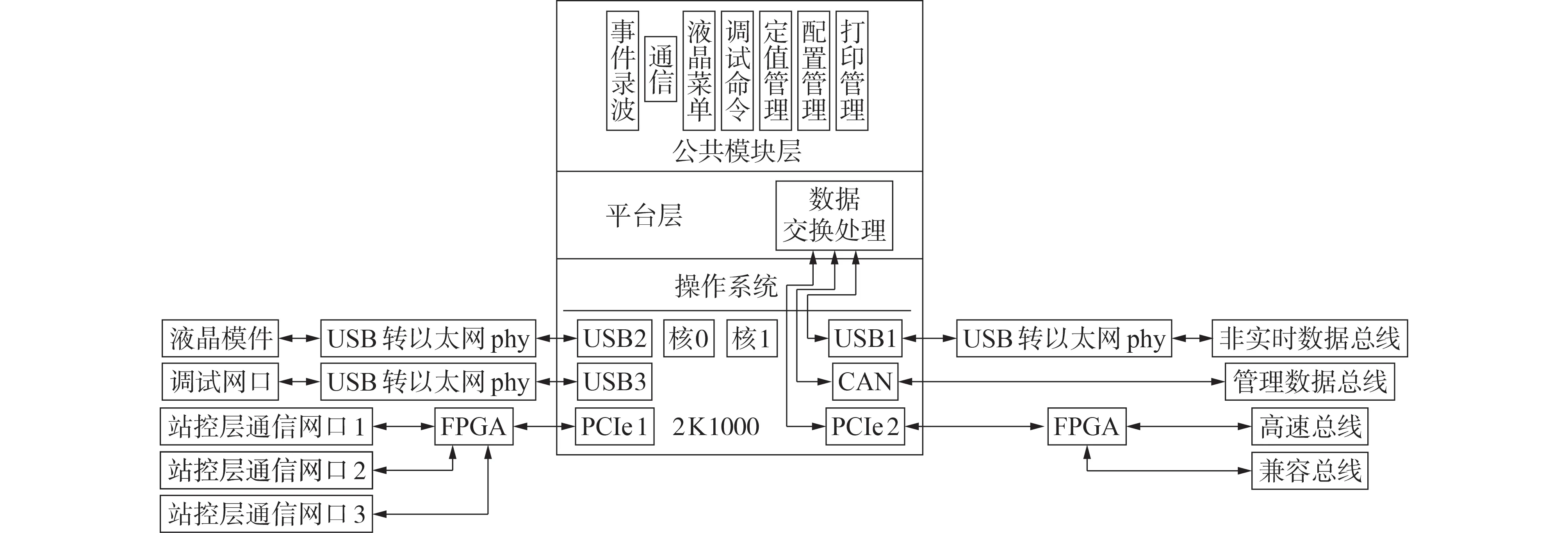

管理模件主要负责事件录波的存储、系统配置及参数定值的管理分发、人机接口管理、对外网络及串口通信、命令及调试。管理模件采用硬件层、操作系统层、平台层及公共模块层4 层架构,其功能框图如图3 所示。平台层主要负责系统管理、系统监视、时钟同步、任务监视、数据交换等业务。公共模块基于平台层的接口和数据,运行相应业务程序,主要包括事件录波、通信、液晶菜单、定值管理、配置管理、打印管理等。

图3 管理模件的层次结构及功能框图Fig.3 Hierarchical structure and functional block diagram of management module

硬件方面,管理模件通过USB1转以太网接入非实时数据总线;通过PCIe2接入FPGA,由FPGA 扩展百兆以太网接口接入高速总线,且扩展兼容总线使其可直接无缝替换在运继电保护装置的对应插件;通过CAN 接入管理数据总线;分别通过USB2、USB3转以太网接入液晶模件和调试网口;3 个站控层以太网通信接口通过PCIe1由FPGA扩展。

2.3.2 保护模件和启动模件

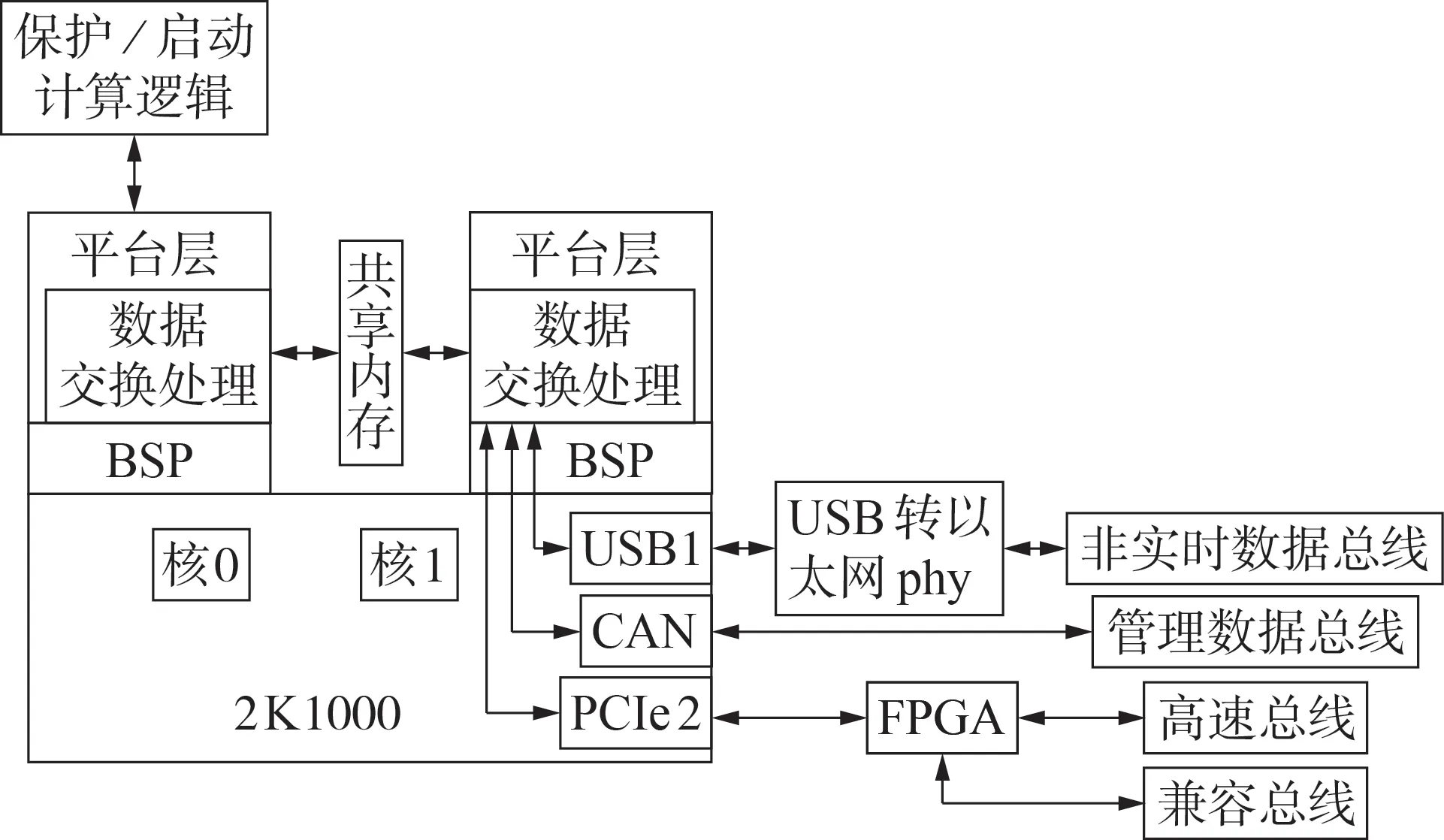

保护模件和启动模件采用相同的硬件架构和软件框架,均以2K1000为基础,采用裸核运行模式,其功能框图如图4所示。

图4 保护或启动模件的层次结构及功能框图Fig.4 Hierarchical structure and functional block diagram of protection module or trigger module

1)硬件方面,保护或启动模件继承了管理模件的基本接口形式,其总线接口和管理模件相同,但取消了外扩的以太网接口和液晶模件接口。

2)软件方面,2K1000 的2 个核分别运行独立的程序,双核之间通过共享内存交换数据。核1 仅部署平台程序,其中的数据交换处理模块负责处理总线上的所有数据,包括数据帧的判断、数据整理及容错处理。在报文校验正确并同步后,将数据放入共享内存,供核0的保护或启动模块使用。核0的数据交换处理模块仅处理共享内存的数据。保护/启动模块的输出数据通过数据交换处理模块发送给核1并由核1发送,有效分散了计算压力。保护/启动模块可选择数据发送的通道,数据交换处理模块根据保护/启动模块的指令通过指定通道发送指定的数据。保护模件只处理收到的保护模拟数字AD 转换器(Analog to Digital converter)数据,启动模件处理启动AD 数据,确保相互冗余校验,满足保护、启动分开的要求。

3)通过平台层程序封装,上层保护/启动计算逻辑程序的接口兼容在运装置,可无缝移植使用。

2.3.3 智能模件

智能模件是继电保护装置平台用于数字化变电站或智能变电站的接口插件,负责接收数字化采样及处理数字化开入开出,为可选模件。智能模件是在保护或启动模件的基础上扩展了8 对光纤以太网接口,其软件的层次结构基本一致,如图5所示。

图5 智能模件的层次结构及功能框图Fig.5 Hierarchical structure and functional block diagram of intelligent module

智能模件在软件上为双核独立运行,通过共享内存交换数据。面向通用对象的变电站事件GOOSE(Generic Object Oriented Substation Event)模块和采样值SV(Sample Value)模块分别部署在核0 和核1 上,两者相互解耦,仅通过共享内存交换数据。智能模件也可仅部署GOOSE 模块或仅部署SV模块,兼容单板件更换。

在网络风暴抑制、报文过滤、SV 报文等间隔控制、SV/GOOSE共口发送等方面,本文参考文献[10]的技术,采用FPGA实现,分担了处理器的计算压力。FPGA 将收到的报文分为GOOSE 区和SV 区,并按照GOOSE和SV的特点分别进行报文过滤和校验,校验有效的报文通过PCIe接口发送给处理器。PCIe驱动程序收到报文后,将GOOSE 报文发给核0 的GOOSE模块,将SV报文发给核1的SV模块。GOOSE模块将需要发送的报文放入缓冲区,由PCIe 驱动实时读取并发送给FPGA,FPGA通过光口进行发送。

2.3.4 采样模件和开入开出模件

采样模件是基于FPGA、AD设计的,其基本原理是由FPGA控制A/D采样时序并读回SV,再由FPGA通过高速总线发给保护模件和启动模件。采样模件采用保护和启动采样分开双AD回路设计,将保护采样数据发给保护模件,启动采样数据发给启动模件。

开入模件采用数字光耦技术,可精确控制开入量的动作电压和返回电压值,光耦隔离的输入和输出信号为数字信号,不受温度、传变比等模拟特性参数的影响,稳定可靠。

开出模件支持大容量、快速跳闸接点,动作时间能控制在3 ms 以内。出口跳闸逻辑经启动模件和保护模件协同控制,并实时对出口接点状态进行监视,有效防止保护装置的单一元件故障造成误动[12]。

2.3.5 系统监视

实时监视装置内部程序模块和模件的状态,是提高继电保护装置运行可靠性的必要措施。本文设计的继电保护装置平台的系统监视主要有以下3个方面。

1)监视装置内部物理特征,主要包括核心处理器的内部温度、采样参考电压、开出回读、报警闭锁回读、电源输出电压和输入电压、光模块的功率及温度、以太网的链接状态、收发数据包等,这些监视量能够直观判断保护装置的内部运行状态和外部线路连接情况等。

2)监视装置内部通信链路,主要包括通信数据流量、数据帧校验、数据有效性等内容,用于监控内部数据总线通信异常。

3)监视装置的模件、模块等。监视各类插件的运行状态,包括插件的心跳、中断、主循环、异常中断等;监视程序模块,包括模块的心跳、异常信号、模块运行周期等,从而跟踪模块运行异常信号,回溯异常运行堆栈信息,以便快速找出异常原因。

所有监视信息均记录在装置的文件系统中并分类处理(告警或闭锁)。

3 平台关键技术

3.1 兼容性设计

本文主要通过梳理在运继电保护装置的外形、尺寸、界面显示、按键布局、端子规格及其信号定义,确保所设计的自主继电保护装置的上述特性和在运装置完全一致,且性能指标和在运装置相当,从而实现整装置的无缝替换。

为实现板件级无缝替换,需要从硬件和软件两方面进行兼容设计。硬件方面,本文采取保持在运装置背板信号线不变,将新增加的信号线全部布置到空闲位置的方法实现硬件兼容。对所有板件均设计了兼容总线,兼容总线覆盖全部在运装置的信号线,实现了板件在电气信号连接上的兼容。软件方面,本文设计的自主可控继电保护装置平台和在运的继电保护装置采用相同的软件平台框架,且配置及数据交换定义完全相同、应用程序接口一致,从而实现了软件兼容。

3.2 关键程序优化

因国产数字信号处理器DSP(Digital Signal Processor)在性能、功耗和软件生态等方面尚无法满足继电保护装置的要求,只能采用国产通用中央处理器(CPU)替代DSP。通用CPU 采用程序和数据共用总线的冯·诺依曼结构,而DSP采用程序总线和数据总线分开的哈弗结构,故在相同的主频下,通用CPU在算力、中断响应实时性及中断执行时间的稳定性方面明显弱于DSP。本文选取高主频的2K1000 代替DSP,通过程序优化使其在算力、中断响应实时性、执行时间稳定性方面满足继电保护要求。

采用减少软件层数的方法提高中断响应的实时性。如图5 所示,处理器采用裸核运行模式,在板级支持包BSP(Board Support Package)上部署平台层程序框架,关键任务采用硬中断直接调度,避免了操作系统任务调度逻辑对中断响应实时性的影响。

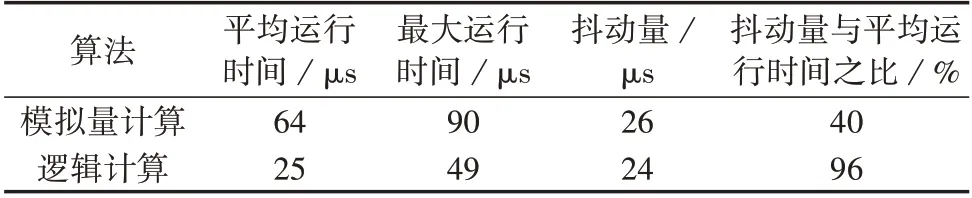

2K1000 为通用CPU,其程序调用通过高速缓冲存储器加速处理。而指令会被CPU 自动换入换出,经常导致中断任务的2 次执行时间相差很大。本文以90路模拟量采样计算和24路逻辑计算为例,测试结果如表1 所示。由表可见,优化前中断执行时间抖动非常大,如用于继电保护运算,会导致中断执行时间超过中断周期,可能造成继电保护装置拒动或误动。

表1 优化前的中断执行时间抖动情况Table 1 Jitter of interrupt service run-time before optimization

为解决中断执行时间抖动的问题,本文将CPU芯片的高速缓冲存储器分为CPU 使用区和保留区。保留区的大小按照中断服务程序的大小设定。在引导程序到内存时,将中断服务程序代码全部锁定到CPU 的高速缓冲保留区,阻止CPU 程序代码的换入换出。这样CPU 在执行中断服务程序的过程中,每次都直接从高速缓冲保留区获取指令,其执行时间抖动变小,可将抖动时间控制在10 μs内。具体原理如附录A 图A2 所示。优化后进行和表1 相同的算例测试,结果如表2 所示。由表可见,优化后的中断执行时间非常稳定,满足了保护算法执行时间稳定性的要求。

表2 优化后的中断执行时间抖动情况Table 2 Jitter of interrupt service run-time after optimization

3.3 内存异常变位纠错设计

嵌入式系统的随机存取存储器RAM(Random Access Memory)可能会因生产工艺、空间高能粒子辐射、电磁干扰等原因导致电位异常翻转,造成保护装置运行异常、误动、拒动等问题[23]。2K1000 的RAM控制器不支持硬件的错误检查和纠正技术ECC(Error Checking And Correcting),故须设计软件的RAM检查和纠错方案。

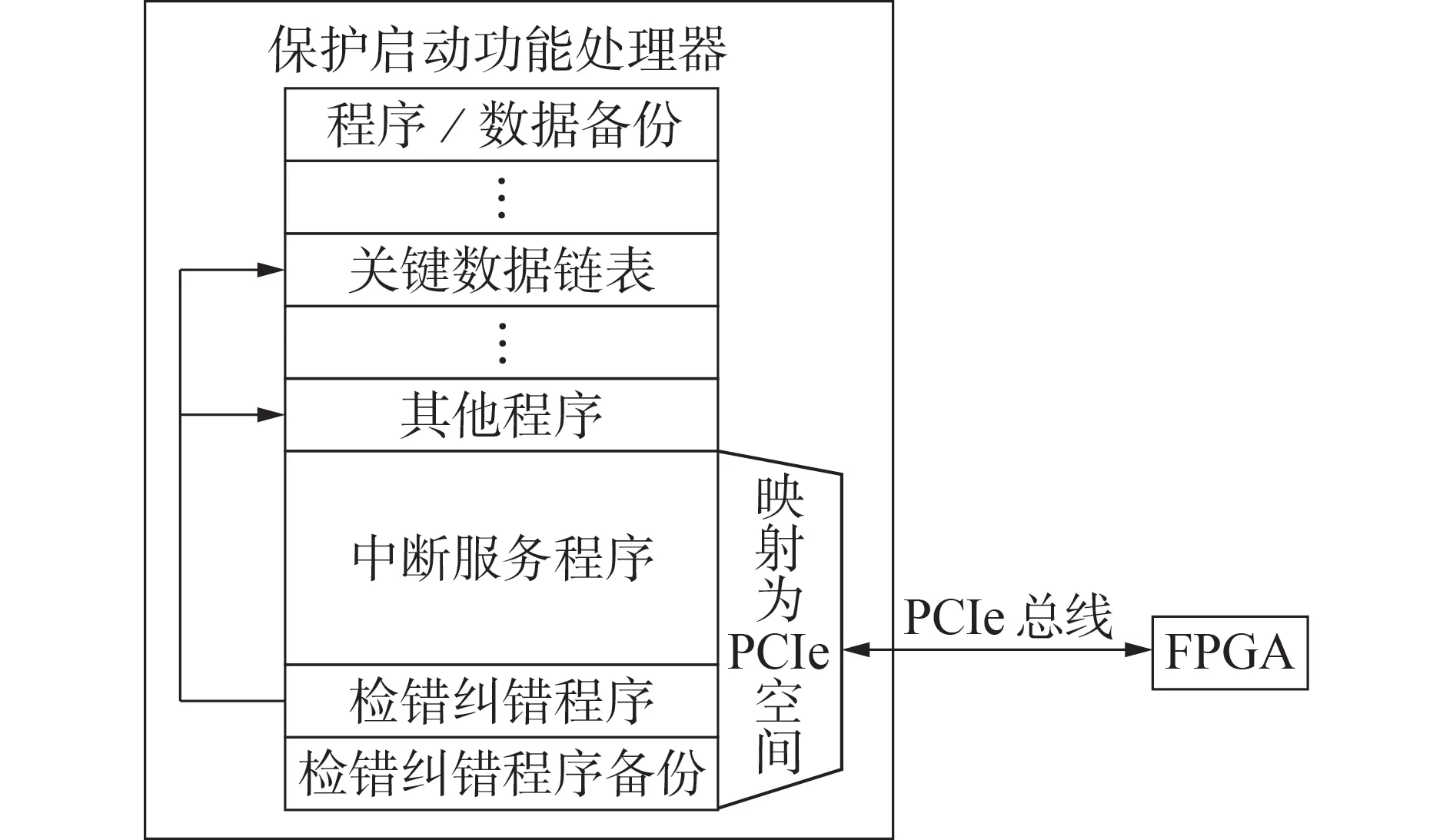

本文将程序空间按重要性进行分区,将中断服务程序和检错纠错程序锁入高速缓冲存储器,并映射为PCIe 空间,由FPGA 通过PCIe 总线直接访问并计算校验码。其他程序、关键数据及其备份内容放入RAM 指定区,由检错纠错程序负责校验和纠错,如图6所示。

图6 RAM异常变位容错设计框架Fig.6 Error-tolerant design framework of RAM unexpected bit change

经过计算,在PCIe 总线传输速率为5 Gbit/s 的条件下,FPGA 在833 μs 的周期内,可以校验超过400 KByte 的指令代码,能覆盖继电保护程序空间,实现每中断校验。对于实时运行程序和数据,由FPGA 每中断主动读取并计算校验码,通过PCIe 将校验码传递给处理器。检错纠错程序在中断头部读取该校验码并和备份区校验码进行比较,若校验码一致则不作任何处理,若校验码不一致则启动程序恢复流程,具体流程见附录A 图A3。对于非实时运行程序和数据,由检错纠错程序分块分时计算校验码,每次计算完成后,进入校验环节,若校验码不一致,则启动程序恢复流程。

本方案利用系统已有的FPGA 协助实时计算RAM 存储器的校验码,既降低了对保护逻辑计算程序的干扰,又未明显增加系统成本。

4 平台应用

在继电保护装置研制上,采用“平台+应用”的层次化研发模式,基于本文的自主可控继电保护装置平台,应用模块及算法可直接移植使用,无需进行改动,如附录A 图A4 所示。研发过程中,始终贯彻兼容设计的原则,实现整机无缝替换和单板兼容替代,如附录A图A5所示。

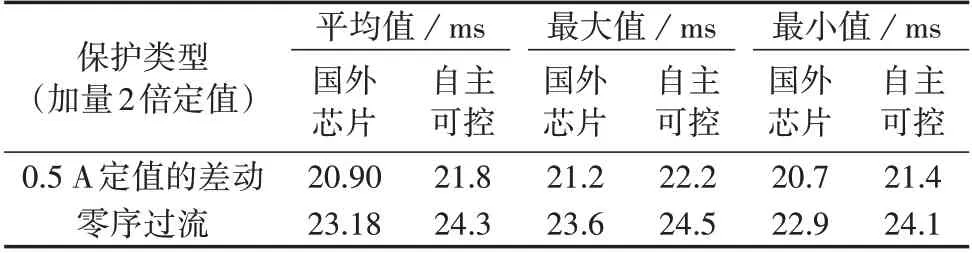

基于本装置平台研制了全电压等级的全系列保护装置,包括母线保护、变压器保护、线路保护等。装置性能指标和现有保护装置基本相当,本文以线路差动保护装置的差动保护和零序过流为例,列出自主可控保护装置和基于国外芯片的保护装置的动作时间,如表3 所示。由表可见,自主可控保护装置比基于国外芯片的保护装置慢0.7~1.2 ms,主要原因是国产继电器出口速度稍慢。从2019 年11 月开始,自主可控继电保护装置陆续在江苏1 000 kV 东吴变/泰州变、宁夏750 kV 贺兰山/杞乡变、江苏500 kV茅山变/武南变、220 kV玉峰变/周市变/亭林变以及福建35 kV 漳州变等顺利投入挂网试运行,且运行稳定可靠。

表3 自主可控和非自主可控保护装置动作时间比较Table 3 Actuation time comparison between autonomous controlled and nonautonomous controlled protection devices

5 结语

本文通过研究自主化处理器自主可控标准,选定了2K1000作为继电保护装置平台的核心处理器,设计了继电保护装置平台,解决了板件级和整装置级兼容替换、通用CPU 中断运行不稳定及内存异常翻转的问题。

随着国产处理器的进步,继电保护装置平台需在整装置功耗、计算能力、配置灵活性等方面持续提升和迭代,不断提高基于国产处理器的继电保护装置平台的适用能力和可靠性,使国产继电保护装置具备国际市场竞争力。

附录见本刊网络版(http://www.epae.cn)。