PXle多通道数字化仪模块的设计

2022-03-17刘明军徐朋朋苗继超唐建立

刘明军,徐朋朋,苗继超,唐建立

(中电科思仪科技股份有限公司,山东青岛,266555)

0 引言

PXIe多通道数字化仪模块是一款16-bit、最高250MSa/s/通道、3U、单槽、PXIe模块仪器。产品包括4个模拟采集通道,具有触发采集、通道同步、自动校准等功能,触发方式支持背板触发、外触发输入,最大输入范围为±25V,输入阻抗50Ω/1MΩ,可提供DC~100MHz的实时带宽。板载2GB DDR3大容量缓存数据,支持乒乓模式的数据交换。板卡采用PXI Express Gen2高速总线,利用DMA模式实现主控单元与采集单元的高速数据传输,开发了基于QT的软面板及驱动程序,既保证了模块跨平台应用,又能获得友好的人机界面,除了板载10MHz高精度TCXO时钟外,板卡还允许用户接入外部参考输入时钟,用户可实现从125 Sa/s到250 MSa/s灵活采样。

1 数字化仪模块总体硬件设计

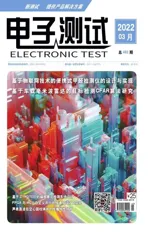

PXIe多通道数字化仪模块由模拟通道板与数据采集板两个电路板整件构成,主要包括模拟通道、时钟与采集电路、触发电路、数字信号处理电路(数据接收、数据存储)、电源电路等组成。整机硬件组成框图如图1所示。

图1 整机硬件原理框图

数字化仪模块的输入信号经过模拟通道调理,进入A/D转换器量化。量化后的数据经过抽取处理存入采集存储器,CPU根据触发系统产生的触发信号,从波形存储器中取出波形数据,送到显示处理模块,在显示处理模块中转换为一定像素的显示数据帧,并以一定的刷新速度在显示设备上实现更新显示,波形存储器中的数据还可供CPU做波形参数测量、信号分析和处理时使用。

1.1 模拟通道设计

通道部分主要由四个垂直通道以及通道控制电路组成。四个垂直通道电路是完全一样的在一个电路板上,即模拟通道板,每个通道设计有屏蔽盒,模拟通道板是可拆卸、可更换的整件,能够独立生产和调试。垂直通道电路整件由继电器开关矩阵、固定衰减器、阻抗变换器、预放大器、程控衰减器、后放大器电路等组成。

图2给出了模拟通道的原理框图。

图2 模拟通道原理框图

固定增益衰减器主要将大功率的信号进行衰减,从而满足通道垂直灵敏度的要求。阻抗变换器的主要作用是将1M欧姆的输入阻抗配成50欧姆,减小后端宽带放大器的直流偏置,减小后端宽带放大器的电压噪声。

前置的预放大器(增益为10dB或30dB)、程控衰减器(0-20dB)、后放大器(8.86dB),主要对不同幅度的信号进行衰减或放大,从而满足通道垂直灵敏度1mV/div~5V/div的要求。

1.2 采集电路设计

数据采集板主要由时钟与采集电路、数字信号处理电路、PXIe接口电路、触发电路及DC/DC变换电路等组成。

时钟与采集电路主要由高稳定的时钟发生器和快速的ADC组成。时钟发生器由频率合成器、参考时钟振荡器等组成,产生的250MHz时钟信号一分为四送给后端的4路ADC作为转换器输入时钟。对于100MHz带宽的数字化仪,要实现4个通道的数据采集,使用4片250MSa/s采样率的ADC来实现四通道250MSa/s的采样率。

触发电路包括模拟触发、数字触发、背板触发电路三个部分。通道触发和外部触发采用传统的模拟触发来实现;而边沿、脉宽、逻辑、脉冲等触发采用新型的数字触发来实现,数字触发全部在FPGA内部实现,数字触发技术可以减小触发抖动,提高触发灵敏度;背板触发是通过背板过来的8个触发信号实现四个通道数字化仪的并行数据采集,这8个触发信号是双向的,也可以将本模块产生的触发信号通过背板送往其他通道,以实现多个模块的数据采集等同步工作,背板触发也在FPGA内部实现。

数字信号处理电路包括高速数据的接收、存储、数字波形显示处理等功能单元,该部分的处理速度直接决定了整机的波形捕获率。对于100MHz带宽,数字信号的处理需要1片高性能的FPGA来实现。FPGA完成数据的采集、存储、波形的生成、图像的合成、数字波形显示、数字触发、背板触发与解码以及PXIe数据通信。

1.2.1 时钟电路设计

系统的采样时钟的设计要求具有高频率、高精度、高集成度等特点,基于成本和工程进度以及小型化的考虑,我们采用单一锁相环的频率合成器件AD9517-4来实现设计要求,以输出高频率,高频谱纯度,低杂散的时钟信号。AD9517-4是一款低功耗、高集成度、内置PLL和VCO的频率合成器,输出频率范围765MHz~2950MHz,能够同时产生4路LVPECL差分时钟、4路LVDS差分时钟或8路CMOS单端时钟共12路时钟,其中4路250MHz、LVPECL差分时钟用于4片AD、1路50MHz、LVDS差分时钟用于DDR参考时钟输入FPGA专用管脚、1路250MHz、LVDS差分时钟用于DDR系统时钟作为冗余设计输入到FPGA专用管脚、另外1路50MHz、LVDS差分时钟用于整个模块的系统时钟输入到FPGA全局时钟管脚。

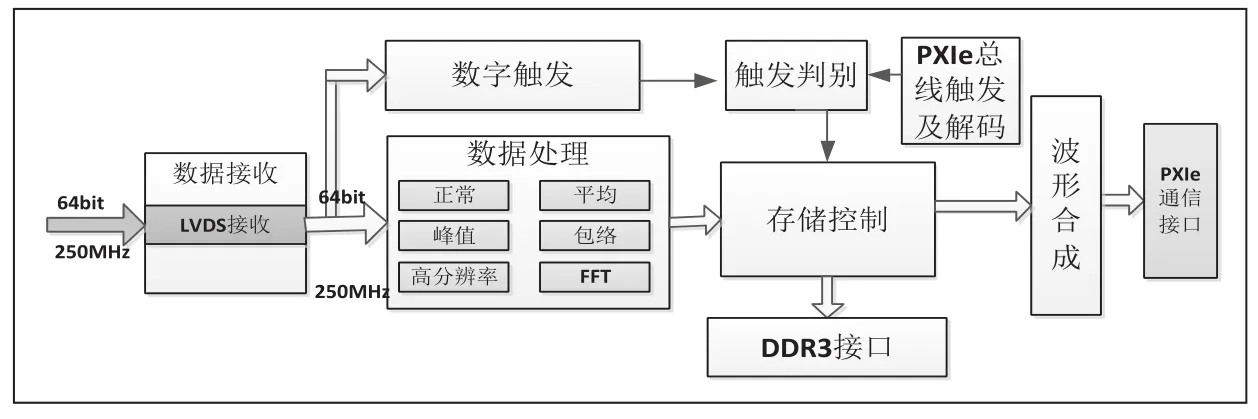

1.2.2 采集与存储电路设计

高速的数据采集单元主要由A/D转换器和数据处理单元等组成,如图3所示。采集电路的核心在于ADC的选型及设计。本方案采用ADI公司的高分辨率模数转换器,它能够实现250MSa/s的采样率,垂直分辨率为16位,采用1.8V、3.3V供电,2Vpp~2.5Vpp的模拟信号输入及250Mbps数据速率的LVDS输出,主要应用于多载波发射机、高分辨率数据采集、多模无线通信接收机、宽带无线接入、雷达、红外成像等领域。

图3 采集电路设计方案

数据处理单元在FPGA中实现,FPGA选用XC7K325T系列。大容量数据存储选用4片DDR3的MT41K256M16内存颗粒实现,内存颗粒的速率支持到1866Mb/s,4片内存数据宽度64位,等效116G的数据流,内存颗粒控制器按照50%效率计算,可实现58G的数据流。250MSa/s采样率、16位垂直分辨率的4片ADC等效速率16G,完全能够满足设计要求,为了匹配通道数据采集与存储之间的速率关系,我们将在DDR控制器设计过程中做相应的降速处理。

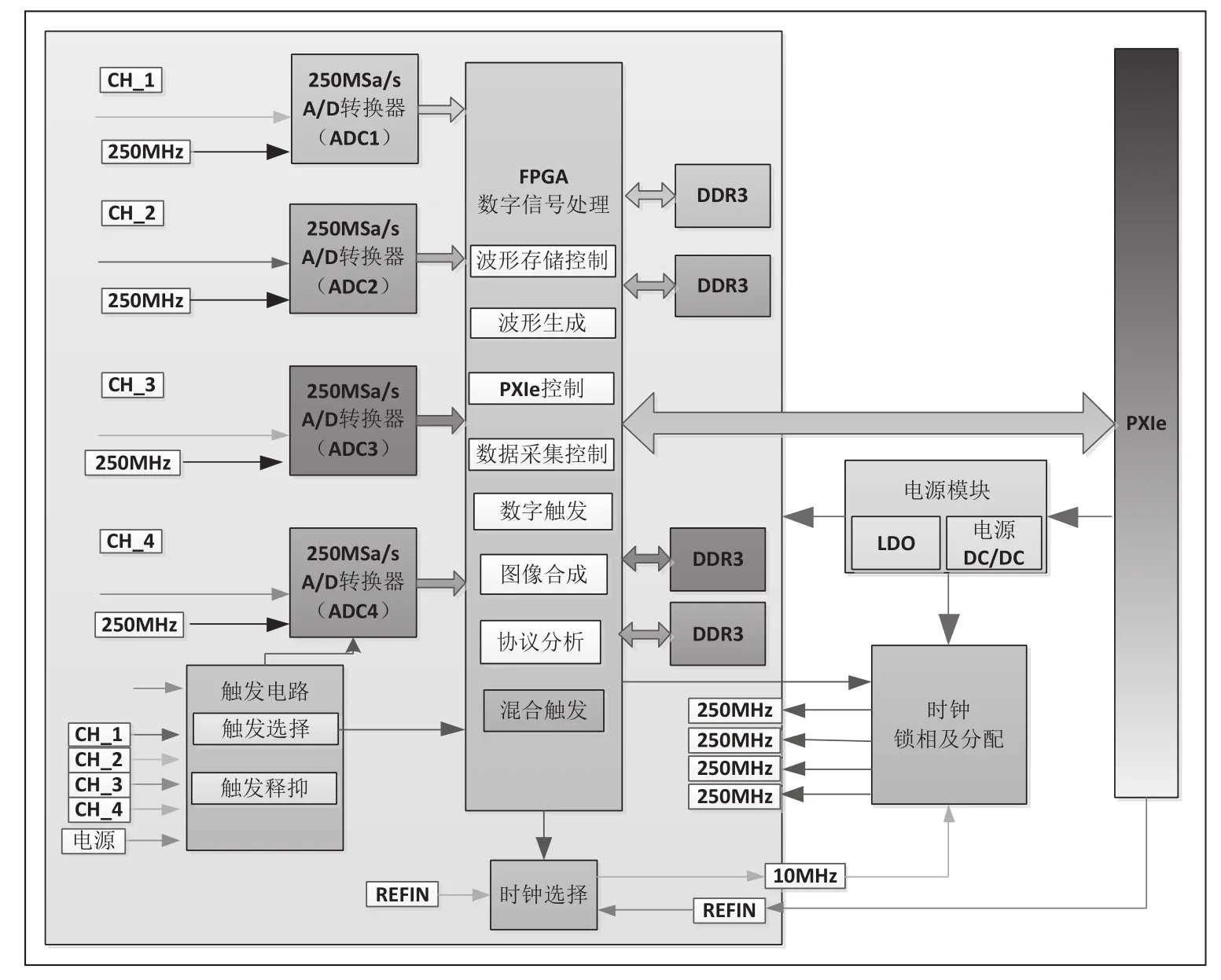

1.2.3 FPGA模块设计

FPGA内部主要实现采集数据的接收、处理及波形存储控制、数字触发,与PXIe的通信接口、图像合成、PXIe总线收发等,数据采集板采用1片FPGA,内部实现如图4所示。板卡采用PXI Express Gen2高速总线,利用DMA模式实现主控单元与采集单元及主控单元与上位机之间的高速数据通信,采用×8模式与上位机之间的数据传输速率达到4GB/s。

图4 FPGA 设计方案

1.2.4 模拟触发设计

PXIe多通道数字化仪模块触发源包含四部分,分别为前面板输入触发信号、通道间的触发信号、软件触发信号及来自PXIe背板的触发信号。其中四个通道均可设置为触发源信号供其他通道同步采集数据使用,具体来说,通道信号经过4:1视频复用器输出1路信号,送入运放,进行信号放大,再送入比较器进行整形,然后单端信号转换成差分信号,最后将信号送入FPGA进行处理。

2 数字化仪模块软件设计

数字化仪软件基于QT进行软面板及驱动程序的设计开发,既保证了模块跨平台应用,又能获得友好的人机界面,控制硬件电路实现模拟信号的采集、显示、分析功能。首先它支持信号的实时采集和显示;可以将时域信号转换为频域信号,并能进行特性分析;能够对信号进行校准、处理以及保存。

QT是一个跨平台的C++图形用户界面应用程序框架,它是一个面向对象的程序框架,易于扩展。QT的良好封装机制使其模块化程度非常高,可重用性较好,对于用户来说使用起来非常方便。QT的API 和开发工具对所有平台都是一致的,从而可以进行独立于平台的程序开发和配置。它使得跨平台软件编程直观、简易和方便。开发环境选用QT Creator 4.10.0,该开发环境完全支持Linux(32位及64位)、Mac OS X以及Windows系统,可以非常好的实现跨平台应用,具有完整的图形用户界面设计功能。

数字化仪软件采用两级设计,底层为驱动层,上层为界面层,如图5所示。

图5 软件结构图

(1)驱动层指数字化仪板卡驱动,用来实现上位机对板卡的控制,以及进行

数据交流。控制驱动选用C++ Library模板,采用动态库形式设计,内部采用函数格式设计,支持C、C++和C#语言,兼容32位、64位系统,支持Windows和Linux系统。

(2)界面层包括上位机软件,主要实现人机交互,辅助用户进行模拟信号的采集、显示、分析。上位机软件通过控制驱动对数字化仪板卡进行控制,使用GCC编译器对驱动进行加载。

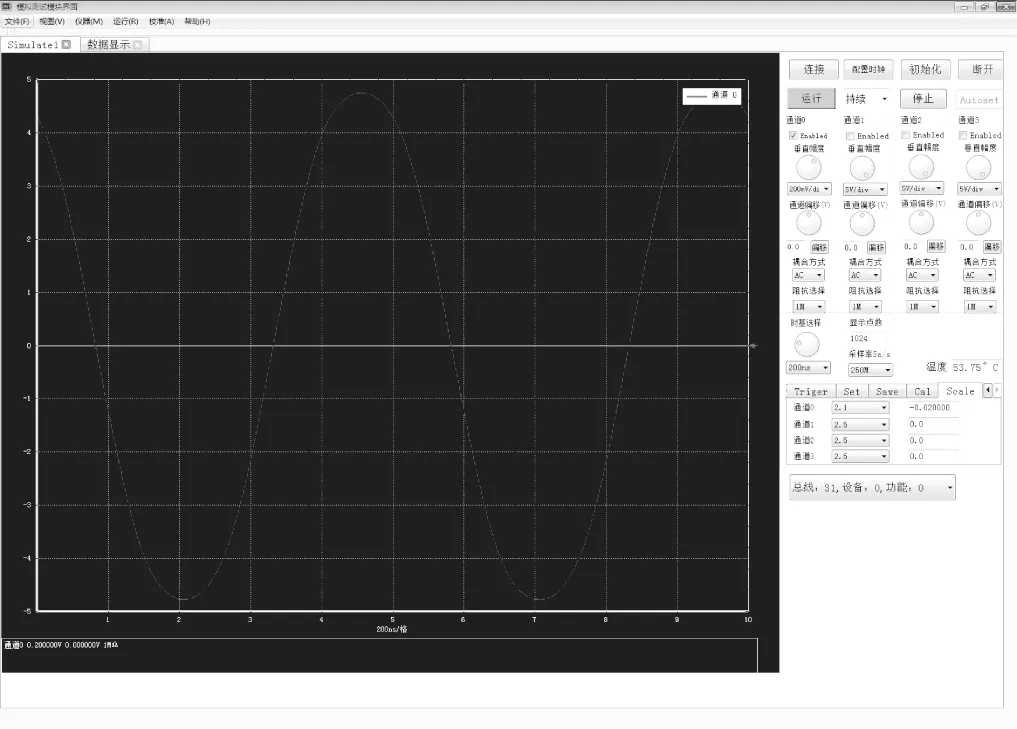

数字化仪软件主界面如图6所示。

图6 数字化仪软件主界面