基于FPGA的图像采集与二值化处理系统设计

2022-03-17杨娅洲张志伟史瑞忠赵辉

杨娅洲,张志伟,史瑞忠,赵辉

(中北大学信息与通信工程学院,山西太原, 030051)

0 引言

随着现代电子技术的不断发展,在图像采集和处理领域,CMOS图像传感器逐渐被大多数人所接受。CMOS图像传感器的集成度高,操作更加便捷,相较于CCD图像传感器有了更大的改进。此外CMOS图像传感器在抗辐射性能,系统复杂程度和可靠性,非破坏性读出方式,优化的曝光控制都要优于CCD[1-3]。结合上述的分析比较,本系统设计将使用CMOS图像传感器作为图像的采集。

FPGA是一种在线可编程的硅芯片,可以根据设计的需求在线更改设计的电路。FPGA可以由硬件描述语言设计出要实现的电路功能,然后编译工具可以自动生成电路结构,FPGA的内部也会自动的布局布线,搭建电路。与ASIC专用电路相比,FPGA是一种半定制的开发芯片,它的开发周期短,可以反复擦除程序,反复更改代码,直到设计出最优的需求电路,但是ASIC专用集成电路,开发流程复杂,不易开发。FPGA的另一个优点是并行执行机制,与基于处理器的系统串行执行不同。基于处理器的系统的任务切换由中断优先级控制,面临着严格限时的任务相互取占的风险。而FPGA的内部设计是基于硬件电路的思想,是真正意义上并行执行操作,符合实际电路的设计过程,每次执行都是为实现某一电路功能,可以减少处理器系统多线程带来的不稳定性。由于FPGA并行数据的处理能力十分强大,在数据的传输过程中又很高速、稳定[4],所以FPGA更加适合作为主控芯片。

1 系统设计

本系统以FPGA作为主控芯片,首先通过FPGA配置CMOS图像传感器的设置参数,如曝光补偿,自动对焦,图像增益等,尽可能使采集到的图像最佳。CMOS图像传感器采集外界的图像信息,图像信息通过IIC总线[5]送入FPGA系统,然后FPGA系统将处理之后图像信息缓存在SDRAM中。经过处理后的图像信息通过USB接口传到PC机上,在计算机上用上位机软件可以实现图像的实时显示和保存。本设计系统框图如图1所示。

图1 系统整体框图

2 硬件设计

本此设计的主控芯片使用的是Cyclone IV系列的EP4 CE10E22C8芯片,该芯片具有10320个逻辑单元,414Kbit RAM,654个逻辑块,IO口的标准电压为3.3V,集成了加法器和乘法器,该芯片完全满足设计需求。而且芯片的功耗低,性价比高,适合用来批量生产和使用。CMOS图像传感器选用豪威公司的OV5640摄像头,该图像传感器可以达到500W像素,具有自动对焦和防抖技术可以清楚的采集到图像信息。由于主控芯片基于SRAM结构,在电路掉电后无法保存数据和程序,所以需要配置一片外的flash芯片,配置芯片选用EPCS4,在quartus II软件中生成jic类型的文件后,可以通过下载器USB Blaster下载到flash中固化程序。时钟部分使用了24M的有源晶振,CLK0和CLK1为FPGA提供时钟,USB_CLK为CY7C68013芯片提供时钟。供电部分选用USB输入的5V电源经过LDO芯片AMS1117-3.3、 AMS1117-1.2和AMS1117-2.5。输出的3.3V电压为VCCIO端口BANK电源和其它电路的工作电源。输出的1.2V电压为VCCIOINT供电,输出的2.5V电压为PLL所在的BANK单独供电。

图像的传输模块采用USB2.0[6],在接口驱动的部分采用了 USB 驱动芯片 CY7C68013A-56LFXC,它集成了 8051 微控制器和可编程的外围接口,在传出数据时可以通过相应的寄存器设置完成传输方向,传输速度的配置。USB2.0的数据传输率可达到56Mbytes/s。

SDRAM采用型号为MT48LC16M16A2的芯片。它具有16bits 的数据位宽,256M的存储容量。为了保证图像的实时性和帧率的稳定性,对于图像的缓存采用了乒乓存储方式,当上一帧图像数据输出时,下一帧图像数据也可以同时缓存,这种缓存模式可以保证图像显示的不间断性和显示出来的图像完整性。

3 程序设计

FPGA使用 Quartus Ⅱ软件作为开发工具,软件程序开发使用 Verilog HDL 语言设计。

FPGA内部模块的具体设计如图2所示。

图2 FPGA 内部的模块

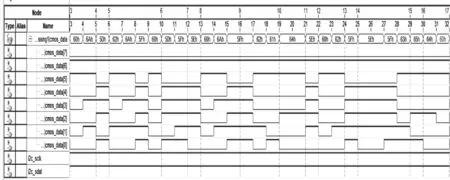

OV5640摄像头采用的两线式SCCB总线,和IIC总线协议基本一致,把OV5640摄像头看作IIC器件。本次设计可以用IIC配置模块主要是通过对IIC总线的操作实现对OV5640摄像头参数的配置和控制,IIC通信协议分为起始信号、结束信号、应答信号。当SCL为高电平时,SDA由高电平向低电平跳变,FPGA向OV5640摄像头发送一个起始信号,等待OV5640摄像头应答。待FPGA收到应答信号之后,开始写入OV5640摄像头器件地址。FPGA再次收到应答信号之后,开始写入OV5640摄像头的寄存器地址加数据。待FPGA收到应答信号之后,开始对OV5640摄像头的下一个寄存器写入数据。配置OV5640摄像头参数的数据传输结束之后。FPGA会向OV5640摄像头发送一个停止信号,此时在SCL信号为高电平时,SDA信号从低电平拉高为高电平。总线又回到空闲状态。

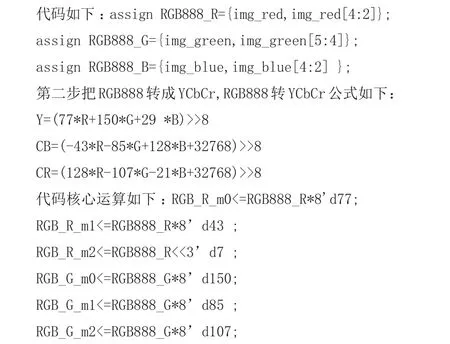

图像采集模块主要是用来采集初始的图像数据,用于后续的处理模块调用。在图像灰度化的算法中,把一个具有 RGB三个颜色通道的图像数据转换为只有一个灰度通道的图像数据,第一步是把RGB565通过verilog语法的位拼接转成RGB888。

img_y0即为要提取的灰度值,通过灰度化计算只是过滤掉了图像的颜色信息,而不改变改变图像的其他特征,极大的保证了图像的完整性。图像的灰度化是保留原有像素的透明度的,即透明度不参与像素的运算,极大的保证了图像的完整性。图像灰度化模块首先用三个寄存器分别对RGB三个不同颜色数据进行存储,然后根据灰度化的公式对三个颜色的数据进行计算得到一个灰度化的值,计算过程中用到FPGA的乘法器和移位寄存器等。经过灰度化的图像数据可以减少后期二值化处理[7]的运算量。下一步是图像的二值化处理。图像二值化是将图像上的像素点的灰度值根据设定的阈值设置为白色或黑色,使图像显示黑白效果,凸显出图像的特征信息,为后续应用进一步简化计算量。这里我们以8bit表示的灰度图像为例,灰度值的范围为0~255,二值化就是通过选取适当的阈值,与图像中的256个亮度等级进行比较。本次设计将阈值设为70,如果亮度值大于设定的阈值70,像素点就设置为白色(255),如果亮度值低于阈值70,像素点就设置为黑色(0)。从而明显地反映出图像的整体和局部特征,处理之后的图像数据通过FIFO接入SDRAM缓存模块,用来供外部设备读取。

在本次设计中FIFO1完成二值化数据和 SDRAM 控制器之间的异步数据发送和同步,FIFO2 完成 SDRAM 控制器和USB传输模块之间的异步数据发送和同步。

4 实验结果与分析

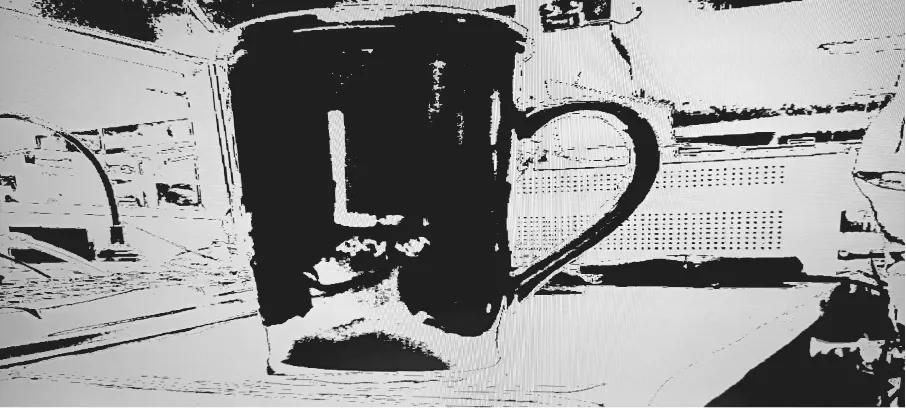

本系统的上位机使用赛普拉斯公司 USB Control 来实现图像的显示和保存。使用 Signal Tap II 抓取的经过FPGA处理的8位图像数据如图3所示。实验结果用深绿色水杯进行测试,实时采集到1280×1024 分辨率下 20 帧的原图像,如图3所示。经过FPGA处理之后的图像结果如图4所示。由于FPGA的并行处理能力强大,运行速度快,可以快速处理采集到的图像,同时通过USB的高速传输使采集的图像实时显示在PC机上,可以更加精准的保存实时图像。

图3 Signal Tap II 数据

图4 实时采集的原图像

图5 经过FPGA处理之后的图像

5 结束语

本设计将FPGA、CMOS图像传感器、USB等电子器件集成在一块,可以弥补传统工业相机体积庞大,操作不便的缺点。同时FPGA高速的并行处理能力,不仅可以节省图像采集和处理的时间,而且采集数据更加可靠稳定。经过实测,采集图像的实时性高,延迟低,分辨率高。