基于VPX的高速跳频信号接收处理平台设计

2022-03-17安效君

安效君

摘要:提出一种基于VPX架构的高速跳频信号接收处理平台,平台基于VPX总线技术保证并行多处理器之间高效、快速、低时延的数据传输。平台软件的动态加载实现功能重构,大幅提升对高速跳频信号的截获和并行处理能力。结合实际工程应用,充分利用硬件资源改进设计方案,使平台简单化、模块化、适用化,经过实际工程验证,性能优越,稳定可靠。

关键词:VPX;跳频信号;RTM

中图分类号:TP391.4文献标志码:A文章编号:1008-1739(2022)02-52-4

0引言

当前通信技术的发展日新月异,跳频、扩频和跳扩频结合等新体制通信信号的应用,通信频段内的信号类型变得更加多样,复杂多变的信号交织在一起,信号的接收处理必须适应目标信号的快速多变性,因此设计开发一种功能可重构、宽带高速跳频信号的新一代接收处理设备是当前通信对抗技术的迫切需求。

针对宽带高速跳频信号,本文提出了基于VPX的高速跳频信号接收处理平台的设计方法。基于VPX架构的处理平台具备强大的数据处理能力、高性能网络交换能力以及丰富的I/O接口能力,运用硬件多通道设计和软件动态加载技术,增强对宽带跳频信号的接收能力,使平台可以更便捷地适应信号处理的更高需求。

1 VPX总线

VPX总线是在VME总线基础上提出的新一代高速串行总线标准[2],可以适应对结构要求复杂、数据速率高的应用环境,而且可以满足多核多CPU计算,以及DSP数据处理,结合高性能FPGA,是国防及航空领域应用中模块化处理平台的发展趋势。VPX平台超越了长期以来以并行总线为主的VME和CPCI平台,VPX定义了集中式和分布式2种系统互连结构,采用基于交换开关的互连网络,有多种串行开关协议映射在VPX中,如SRIO,PCIe,GbE等[3],高速串行传输与交换技术的应用使得信号处理平台向更高处理性能发展,在结构方面增加了模块的坚固性要求,可以满足对冲击、振动、电磁辐射等复杂环境下的高可靠性要求。

2平台设计

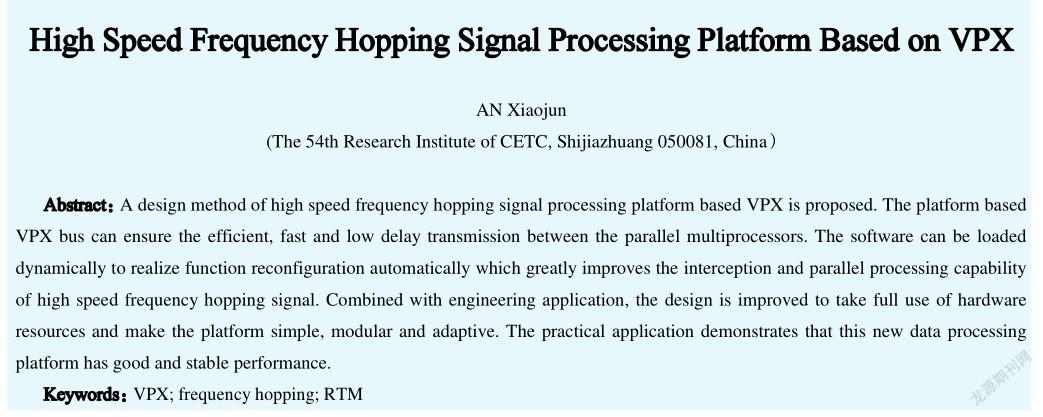

平台整机设备是标准19英寸的上架设备,高度为7U,风导冷结合散热。平台中的模块采用前后插互联方式,模块包括主控单元、处理单元、信道单元、时钟源单元、电源单元、接口单元和采样单元,其中接口单元和采样单元是RTM模块,设备通过RTM后出线[4],平台组成如图1所示。

背板支持9个6U前/后插模块槽位,1个6U VPX电源槽位,设定功率1 000 W,1~3槽位的板卡可以任意互换,4~9槽位的板卡可以任意互换,根据实际业务进行板卡的灵活配置。

3 VPX背板设计

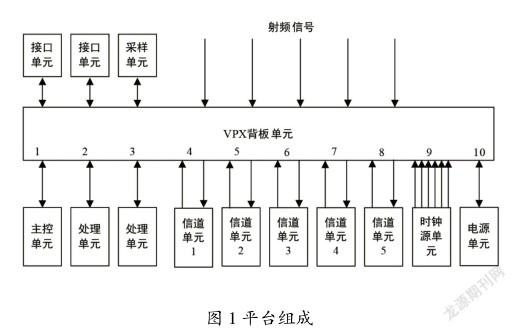

VITA65定义了用于描述数据通道宽度:

UTP(Ultra-Thin Pipe):是1×的链路宽度,由收发差分信号各1对组成;

TP(Thin Pipe):是2×的链路宽度,由收发差分信号各2对组成;

FP(Fat Pipe):是4×的链路宽度,由收发差分信号各4对组成。

VITA65将系统中的数据传输通道从逻辑上划分为控制平面(Control Plane)、数据平面(Data Plane)、扩展平面(Expansion Plane)、管理平面(Management Plane)和公用平面(Utility Plane)。控制平面用于传输设备控制信息;数据平面用于传输应用层的高吞吐量、实时性数据;扩展平面用于相邻槽位主从设备数据传输;管理平面用于智能平台管理总线(IPMB)带外信息传输通道;公共平面包括电源、复位、时钟、槽位号、JTAG等杂散信号[4]。

背板拓扑结构如图2所示。

SLOT1是主控模块,SLOT2和SLOT3是数字处理模块,数据平面和扩展平面采用FP数据通道,各1个4×的链路,各模块之间数据传输总线采用SRIO进行数据传输,SRIO网络拓扑结构为Full Mesh结构,不必设置专门的数据交换模块,模块内部设计有SRIO交换电路,使应用SRIO的模块形成全互连网络,所有的SRIO设计速度均为6.25 Gbps,可滿足任意2个模块间高速的数据传输。

控制平面采用LVDS串行总线,点对点的传输方式,主控模块与其他模块之间通过2对LVDS实现控制指令的发送和接收,可以满足主控模块对其他模块工作参数的控制,节省更多的高速资源用来进行高速宽带数据的传输。

管理平面作为平台硬件信息的管理和监控,采用基于I2C总线的IPMB总线。I2C总线可以连接各种外围设备,如处理单元、信道单元、电源单元等。同一时刻,总线只能有某一主控模块控制允许连接不同传送速率的设备,保证设备的可扩展性。IPMB总线用于各模块硬件信息的管理和监控,如温度、电压、电源状态等。机箱管理采用通用指令,通过IPMB接口访问智能平台管理接口(IPMI)协议获取机箱内所有的IPMC。

公共平面包括平台通用时统、电源、同步时钟等,时统和同步时钟采用MLVDS总线。

4硬件设计

处理平台主要有采样单元、接口单元、处理单元、主控单元、信道单元和时钟源单元等。其中采样单元、接口单元采用VITA46/VITA48规范标准RTM模块。

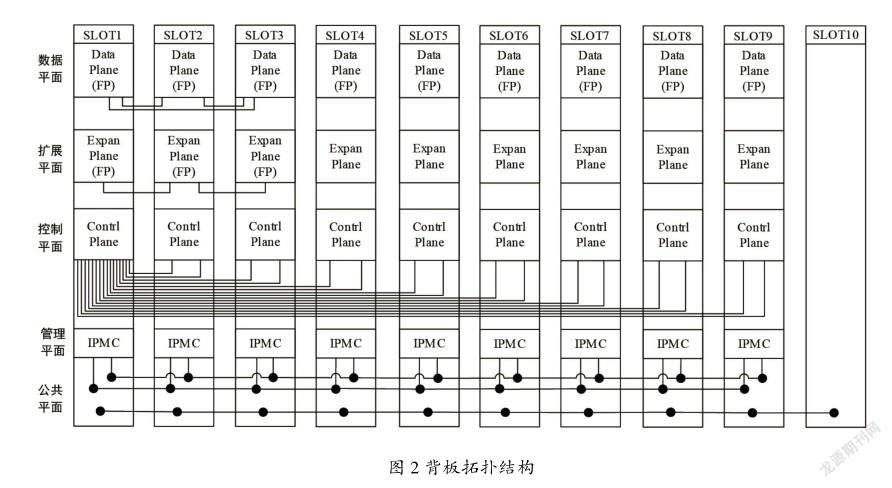

4.1 RTM模块设计

后插SLOT1、SLOT2、SLOT3采样单元和接口单元根据需要采用RTM模式,RTM与各功能模块相耦合,采用VPX 6U标准结构,支持风冷散热。为了减少模块种类,降低平台维修成本,模块做了兼任设计,模块定义完全兼容。RTM模块组成如图3所示。

模块具备多通道采样、接口转换功能,根据不同功能需求,配置合适的电路,满足平台采样和接口转接功能需求。RTM模块有设备管理总线(I2C)、公共总线(MLVDS)、数据总线(SRIO)和控制总线(LVDS)4种总线。

SLOT1接口单元的主控单元是主模块,采用I2C总线实现从其他从模块获取管理信息的手段,同时本单元通过控制接口接收时统和同步时钟,经由MLVDS分发到各个处理单元,保证平台工作的同步,其他控制功能接口通过LVDS总线实现。

SLOT2接口单元配合前插处理单元独立完成处理结果数据的输出,输出接口为网络接口。

SLOT3采样单元实现多路高速宽带数据的同步采样,通过SRIO总线经由背板传输给前插处理单元进行宽带数据同步并行处理。

4.2通用处理模块设计

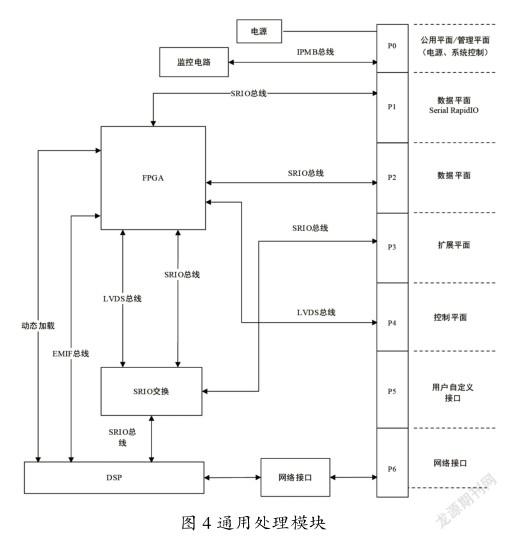

主控单元和处理单元采用统一的硬件平台———通用处理模块。通过软件重构,通用处理模块可以实现数据处理和控制管理,主要由FPGA、DSP、SRIO交换和电源等电路组成。通用处理模块如图4所示。

SLOT1主控单元负责管理平台各模块的工作状态,并根据实际工作模式完成平台内部资源的检测识别和管理调度。模块中DSP选用TI公司的TMS320C6678,具有8个内核,其丰富的外设接口为用户提供了多种可选择的引导设备[5],包括Flash,I2C,SPI,PCIe,SRIO,HyperLink,Ethernet等,满足其对外围设备的控制管理。

SLOT2和SLOT3处理单元实现高速跳频信号通过SRIO接收同步高速宽带数据,共同完成高速跳频信号的侦收和測向处理。TMS320C6678集成的8个处理核,可达1.25 GHz的定浮点处理核,提供40 Gmacs定点运算和20 GFlops浮点运算能力,可以侦收处理50多个跳频点并以76 000跳/s的速率快速跳变的脉冲信号。板载FPGA选用Xilinx公司的XC7V690T,拥有52 920个RAM资源、3 600个25×18的乘法器和693 120个逻辑资源,且通道数据率达10 Gbps以上的SRIO数量达80个,其工作速度快,主要进行采样数据接收、宽带数字下变频、滤波等处理运算,然后利用内部高速SRIO来进行数据传输,可以满足海量数据传输的要求;SRIO交换芯片IDT公司第二代RapidIO交换产品CPS-1848,有18个端口,48路全双工串行通道,每个通道的最高传输速率可达6.25 GBand,最高240 Gbps持续峰值非阻塞交换带宽,支持直通模式和存储-转发模式,支持单播和多播模式,支持全局路由和端口本地路由模式[6],2块处理单元板间和板内高速宽带数据通过SRIO路由进行实时交换。

4.3其他处理模块

信道单元用来实现模拟信号变频、滤波,时钟源单元用来给平台提供同源的参考时钟。二者基于OpenVPX\VITA65标准进行设计。接口功能划分如图5所示。P0实现供电和系统对模块的控制功能,其他位置用于对外模拟接口,采用背板盲插方式,可以根据实际需求配置接口。

电源单元为平台提供符合VITA62规范的电源,为平台提供最大1 000 W的电源。

5软件设计

平台一共有3片TMS320C6678、25个主频1.25 GHz的处理核。同一单元模块内部TMS320C6678通过1路4×SRIO与交换电路互联,单元模块之间有2路4×SRIO互联,彼此之间可以通过路由交换指令和数据,通过软件的任务管理,充分发挥各个单元模块的并行运算和高速数据传输的能力。

多核任务分配采用主从方式,主核负责与外部指令和从核进行数据交互,从核负责数据处理,3片TMS320C6678分别接收一帧数据单独完成全部处理,并行处理实现高速跳频信号的实时处理。

6工程应用

宽带跳频信号工作在260 MHz的带宽内,具有跳频点数目多、跳速高的特点,每一个跳频点的持续时间不足7μs,经过MSK调制后信号的3 dB带宽约3.5 MHz,通过模拟信道单元和数字处理单元资源的合理划分,极大减少了硬件资源的消耗,在工程上得到了广泛的应用,高速宽带跳频信号接收机如图6所示。

7结束语

VPX作为目前主流的串行总线标准,硬件平台、平台软件环境组合成开放式高速信号处理平台,加载功能软件程序配以应用软件,实现阵列处理、并行处理、流水处理等;平台在总线上采用高速串行SRIO总线作为模块间和模块内节点间的数据传输通道,既保证高传输带宽,又有较强的扩展性;通过多核并行处理和高速数据交换,保证了对高速跳频信号全概率接收和实时性。

参考文献

[1]孙高俊,丁岐鹃.基于VPX总线的雷达数据处理平台设计[J].雷达科学与技术,2019,17(1):99-103.

[2]汪宁.一种基于VPX架构的机载计算机的设计方法[J].电子设计工程,2019,27(19):59-63.

[3]邓豹,刘冲.一种高性能通用处理模块的设计与实现[J].电光与控制,2014,21(10):75-79,88.

[4]向巍,李牧.基于OpenVPX的宽带交换平台设计[J].工业控制计算机,2015,28(11):43-45.

[5]吴沁文.多核DSP芯片C6678引导过程的研究与实现[J].现代雷达,2016,38(11):35-39.

[6]任成喜,徐定良,梁慧.基于SRIO交换的雷达通用数字信号处理模块设计[J].现代雷达,2017,39(3):42-48.

3531501908237