一种双通道的交叉数据采集存储系统设计

2022-03-15豆根生周小刚

豆根生,周小刚

(河南农业大学理学院,河南郑州 450002)

0 引言

近年来,我国在科技领域的实力不断提升,在智能汽车和新能源智能化方向不断提高自主研发能力,在研制各类型号的汽车时,需要对其安全性能参数进行全面评估,尤其是在撞击试验和高速行驶试验中,存在高速运动、剧烈振动、瞬时撞击以及空气摩擦等复杂测试环境,给测量系统的搭建造成困难。以太网传输的传输方式简单[1]、应用范围广泛且传输速度快,以太网的传输速率在近年来发展迅速,可以达到千兆甚至是万兆[2]。当前,以太网技术在工业领域成熟运用,但传输速率仍然无法满足实际应用的要求,为拓展测量参数,增加实际测量的数据,千兆以太网与RS485混合交叉存储成为一种新的方案。基于千兆以太网与RS485并行交叉采集存储技术,为高速公路汽车在复杂行驶环境试验过程中图像数据以及音频PCM码的获取提供了新的解决方案。本文详细地介绍了总体设计方案以及关键技术,为相关项目提供了技术参考,本方案的提出对汽车、航空航天、船舶等领域的发展具有重要的参考价值。

1 总体设计

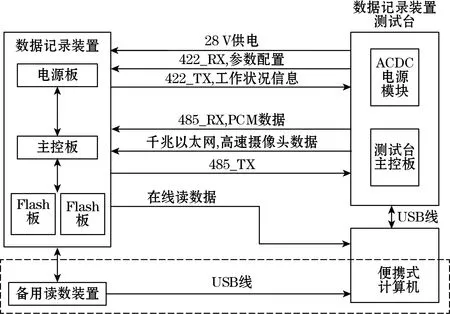

整个存储测试系统由数据记录装置、测试台、备用读数装置三部分组成。当汽车计算机发送无效块检测指令时,数据记录装置内的存储模块完成无效块检测与处理,当汽车计算机发送存储指令时,数据记录装置将执行存储操作[3],配置交叉存储的模式将高速图像与音频PCM数据存储在FLASH中,等待试验完成后对存储数据进行回读,测试台用于模拟高速图像数据和PCM数据,为数据记录装置提供数据源。同时模拟综合测量单元发送擦除指令给数据记录装置,并接收数据记录装置的反馈结果[4]。数据记录装置通过参数配置接口接收测量综合单元输出的参数配置,并将配置结果与工作状态反馈给测量综合单元;接收综合测量单元转发的擦除指令,完成擦除,并将擦除完成信息反馈给综合测量单元;接收高速摄像头输出的千兆网接口的数字信号和PCM输出的RS485接口的数字信号,对数据进行采集、打包编帧,存入FLASH阵列。试验终止或者完成后,千兆以太网2读取数据记录装置数据,最终通过汽车上位机软件对数据进行解析等,总体设计如图1所示。

图1 总体设计组成原理图

2 硬件设计

本系统硬件设计主要由高速数据存储单元设计、配置RS422接口设计、高速音频RS485接口设计、高速摄像头千兆以太网数据接口设计组成。

2.1 高速数据存储单元设计

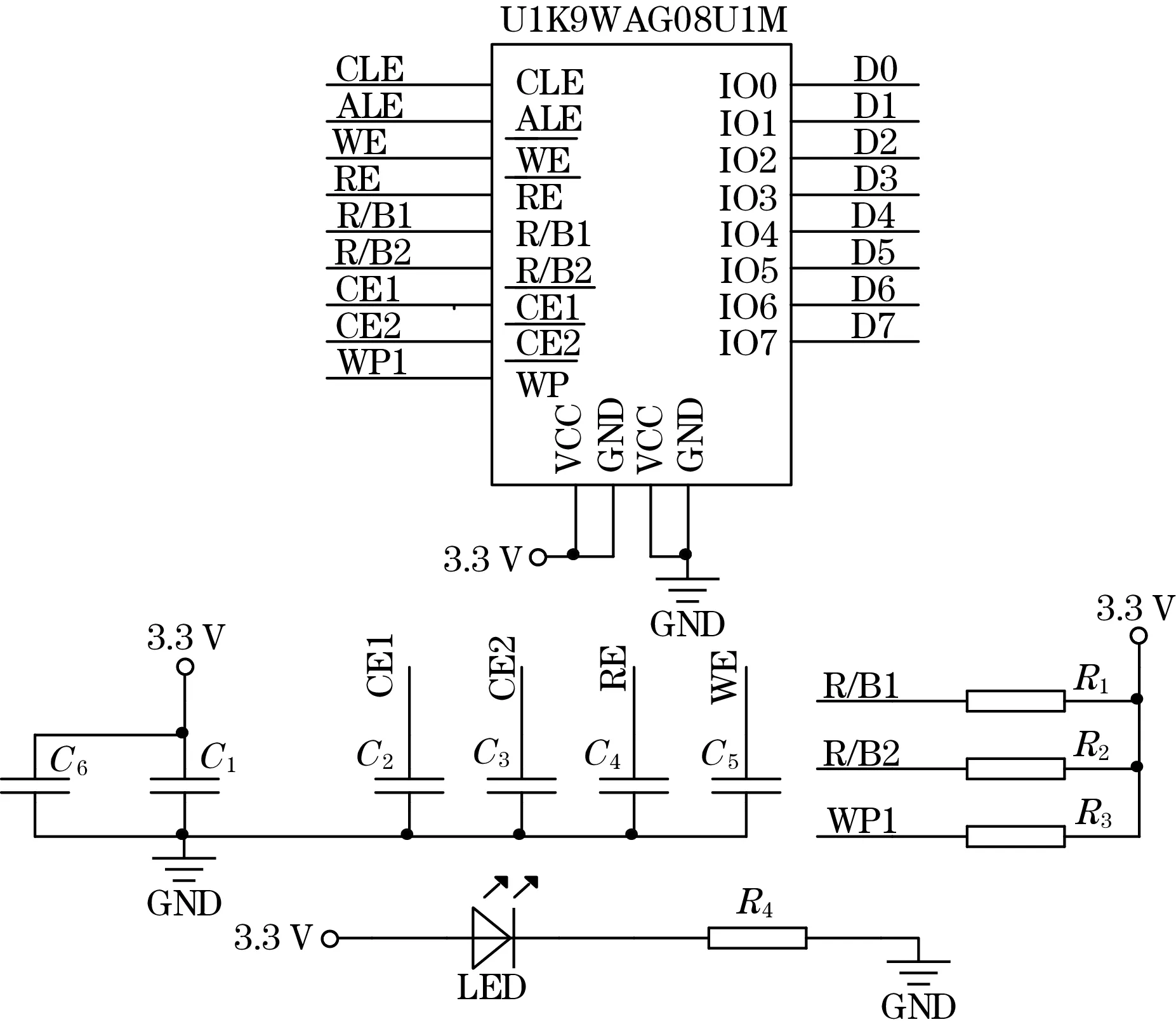

为增强系统稳定性,对存储电路板采用独立设计的方法,电路板上只放置单块FLASH芯片和相应的配置电路,FLASH芯片采用的是K9WAG08U1M,通过特殊导线将主控板与FLASH板进行连接,FPGA控制片选信号“CE”与完成/忙碌信号“RB”等主要信号即可实现对FLASH进行操作,其中采用Q2、Q3接口连接FPGA与存储器,采用Q5接口作为备用读数[5],本设计根据设计需求合理选择FLASH存储容量,采用2片8 GB的FLASH,图2为存储板电路设计图。

图2 存储板电路原理设计图

2.2 配置接口电路设计

通过RS422接口为数据记录装置外部输入指令与状态信息反馈,数据结构为一位起始位、八位数据位、一位停止位,波特率为115 200 b/s[6];接收汽车上位机输出的配置参数并更改工作状态,比如PCM码速率设置,并将配置结果通过RS422返回给汽车上位机[7]。接收综合测量单元的擦除指令。图3为存储装置的RS422接口电路示意图。

图3 RS422接口电路

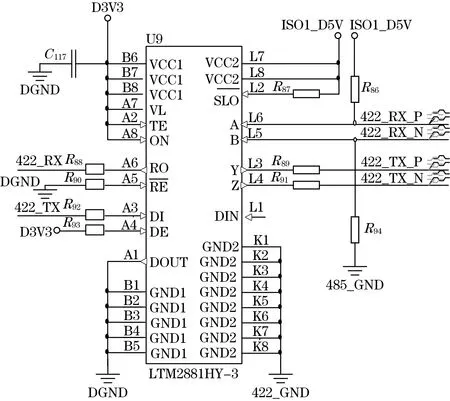

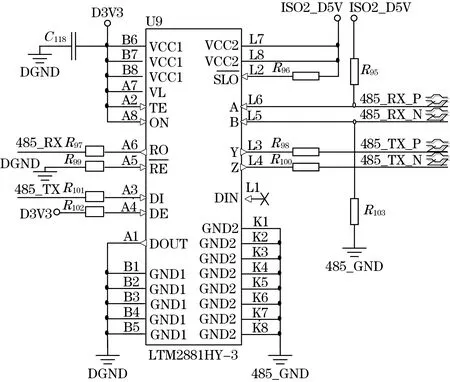

2.3 PCM异步RS485接口电路设计

通过异步RS485接口接收音频PCM数据,误帧率不高于10-5。PCM数据帧格式如下:帧长512 B(其中1~508 B为数据,509~512 B为同步码)[8],单字节数据先发高位,后发低位,码速率10 Mb/s,帧同步码0x9ABCB52C,每16帧反码1次,即每16帧帧同步码为0x65434AD3。PCM输入波特率可设:通过配置接口设置数据记录器PCM输入信号波特率为4/10 Mb/s,默认波特率为10 Mb/s[9]。选用的接口芯片为LTM2881HY-3,芯片为BGA-32封装,该芯片VCC1供电3.3V,内部自带DC-DC隔离电源,输出VCC2电源ISO_5V。图4为存储装置的RS485接口电路示意图。

图4 RS485接口电路

2.4 数据存储与回读接口设计

采用UDP/IP协议接收高速摄像头输出的图像数据,并将数据存储起来,输入数据的平均输出速率不大于400 Mb/s,UDP数据包格式的总长固定可调。有效数据长度为1008 B;根据汽车上位机指令输出存储数据,采用配套电缆测试时,输入/输出接口的丢包率不高于10-5。数据回读接口能够将存储器中的摄像头数据和音频PCM数据回传至测试仪或上位机[10]。数据回读时有效数据的平均传输速率不小于200 Mb/s。数据回读接口也采用千兆以太网接口,千兆以太网用的PHY接口芯片选用88E1111-BAB1I000,芯片为BGA-117封装。网络变压器选用HX5008NL。

3 FPGA逻辑设计

本次程序FPGA逻辑设计主要采用交叉写的方式向FLASH芯片中写入数据,写入方式如图5所示。数据写入时,首先写平面0的第1块,然后写平面1的第1块,然后写平面2的第1块,然后写平面3的第1块。即4个平面的同一块地址作为1组,写完这1组以后,再进行块地址加1的操作,继续写下一组,以此类推[11]。依据系统需求,图像与PCM的存储速率为50 MB/s+2 MB/s=52 MB/s,单片Flash不能满足需求,所以设计2片FLASH并行存储。单片存储速率需要26 MB/s。目前验证了2片FLASH并行存储[12],单片存储速率为28 MB/s>26 MB/s,满足设计要求。

图5 编程示意图

4 关键技术研究

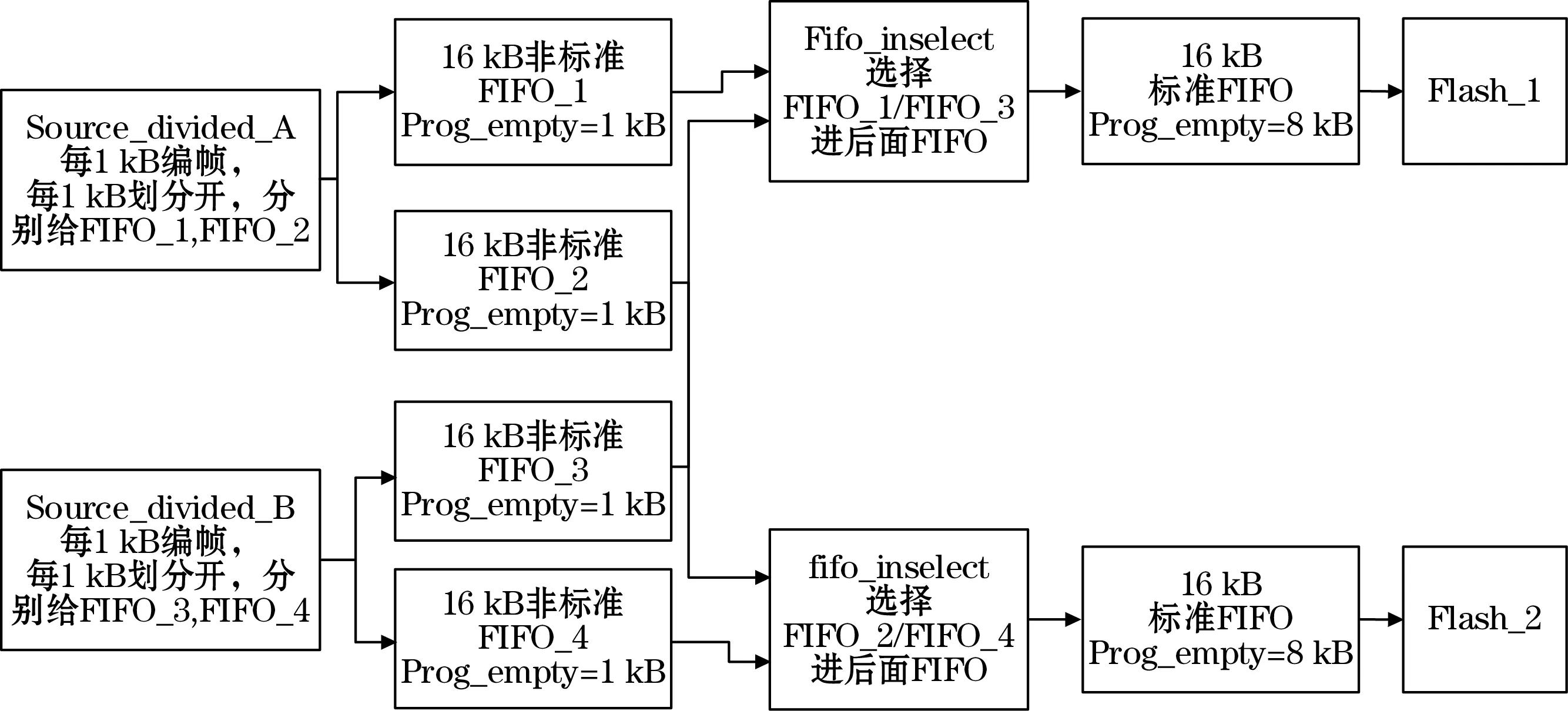

如图6所示以千兆以太网数据为例,数据进来先向FIFO存数据,对每1 kB数据进行编帧,每1 kB数据进行划分,然后Fifo_inselect分别对FIFO_1与FIFO_3的数据进行选择[13],如果达到1 kB的数据就进行存标准FIFO,并且将结果存在后面FLASH,当取数据的时候,Fifo_inselect在2个16 kB的标准FIFO循环切换取1 kB的数据利用后面的千兆以太网口进行数据的发送,同理可得PCM数据也采用这种方式进行数据的发送[13]。通过RS422接口进行参数配置模块,接收上位机的擦除命令,并将参数配置存在EEPROM,上电读取更新配置参数,并将结果通过RS422返回上位机,对FLASH的存储模式进行合理的配置[14],采用“交叉写”的模式,能够明显的提高FLASH页编程速度。能够快速完成存储图像与PCM数据,图6为总体的流程图设计。

图6 总体流程图设计

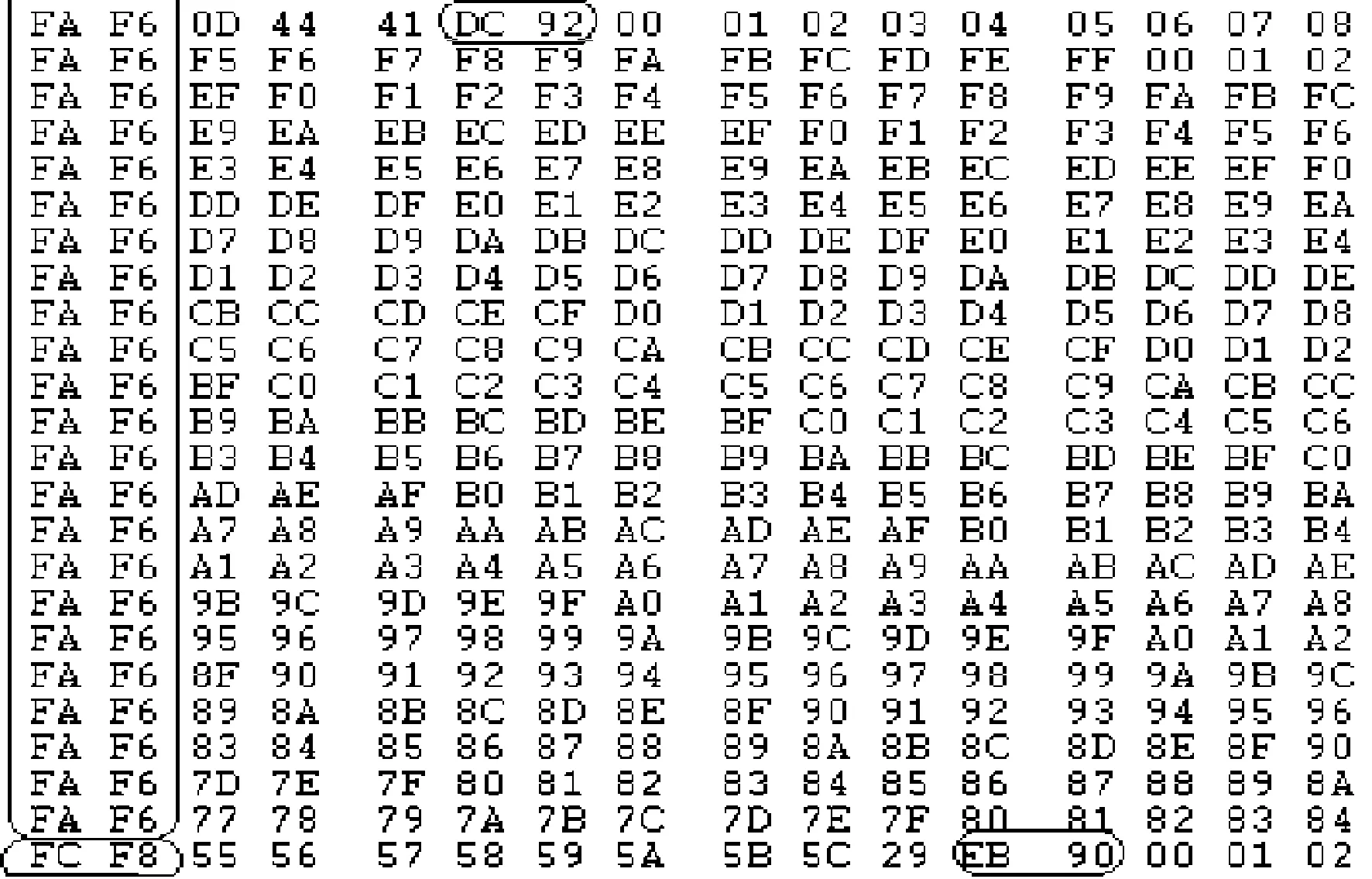

本系统采用某单位的系统单机进行测试,在试验完成后对数据进行回读,并将结果采用HeEdit软件显示,本文部分结果如图7所示,每行显示有1024个字节,在接收到的每一帧的数据中,“FC F8”为RS485接口有效数据帧格式标志,在接收的每一帧数据中,“FA F6”为千兆以太网接口的有效数据帧格式标志,在接收的每一帧的数据中“DC 92”为图像数据自身帧标志,“EB 90”为PCM数据自带的行标志[15]。

图7 Hex Edit软件中对部分数据结果进行显示

对部分数据结果进行展示,分析图7可以得到:数据整齐有序排列,数据规则跟系统单机测试中数据形式比较吻合,并且在测试的过程中,每帧的数据中不存在误码信息,帧结构较为完整,数据具有可读性,后续经过数次试验,并且对回读数据进行分析,每帧数据没有错误信息,误码率几乎为0,因此整个系统具有可行性。

5 结论

根据试验结果对整个系统进行评估,对其进行可行性分析以及整个数据记录装置的总体设计分析,经过可行性分析以及多次读取数据并分析可知,误码率为0,存储容量为16 GB。性能稳定、可靠,数据传输稳定,满足系统任务要求。