基于J750的ARINC429总线协议芯片测试技术研究

2022-03-15宋尚升龙永佳

宋尚升,龙永佳

(中国空空导弹研究院,河南洛阳,471000)

0 引言

ARINC 429总线是一种航空总线,广泛应用于航空领域,它将飞机的各系统或系统与设备通过双绞线互连起来,是各系统间或系统与设备间数字传输的主要途径。在这些应用中,ARINC 429总线接口电路起了重要作用。本文关注的就是该类电路的测试,并具体以DEI1016A芯片为例,基于美国Teradyne公司的J750平台,详细介绍了一种测试解决方案。

1 ARINC429 数据总线

ARINC429 总线是通过一对单向、差分耦合、双绞屏蔽线进行数据传输,本质属于串行通讯范畴,支持最高100 kbps的传输速率,具有接口方便, 数据传输可靠等特点。

■1.1 数据字格式

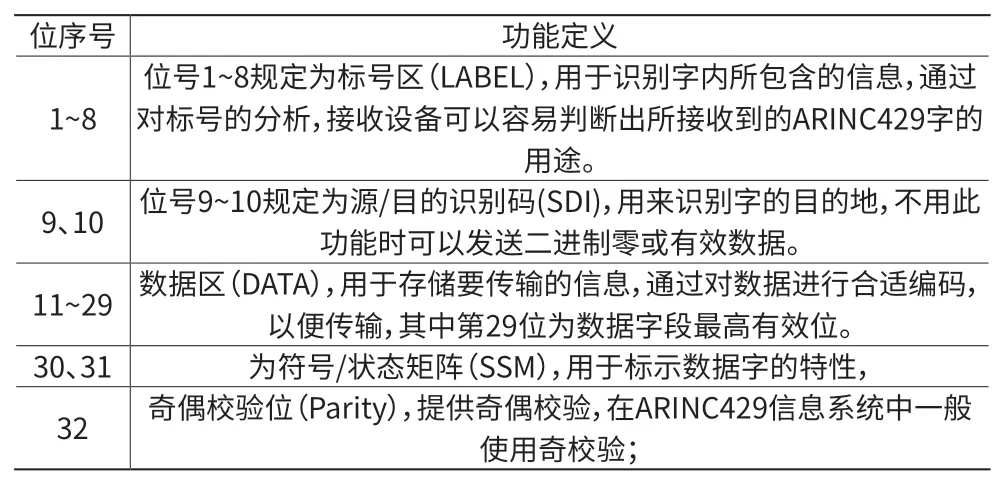

数据总线以串行的方式传输数字数据信息,总线传输速率为12.5~100kbps,一个数据字就是一个基本信息单元,由32位构成,分别为数据位(21位)、标志位(8位)、状态位(2位)、奇偶校验位(1位)。表1为数据字32位格式功能定义[1]。

表1 ARINC 429 数据字格式

■1.2 ARINC 429总线信号电平特点

ARINC429 的数据传输采用双极性归零码,在每一个信号周期,前半周期包含数据,后半周期电位回到0V,以维持自身同步。当前半周期为高电平10V时,表示逻辑“1”,为低电平-10V时,表示逻辑“0”,为0电平时,表示空数据“Null”。图1为ARINC 429双极归零信号和对应逻辑电平定义[2]。

图1 ARINC 429双极归零信号和电平

每一个32位数据字传输完毕后,都需要有4-bit的间隔,作为本数据字的结束标志。间隔后接收到第一个有效数据,表示新数据的开始。

2 DEI1016A芯片介绍

DEI1016A是一款ARINC 429通讯协议芯片,它为标准航空串行数据总线与16-bit位的数字数据总线之间的通讯提供了一个便利接口。它内部包含了一个的单通道发送器,两个接收器和一个通过编程可实现不同操作控制寄存器。两个接收器相互独立,均可直接与ARINC429数据总线通讯。

发送器电路具有一个8×32bit缓冲存储区,通过控制逻辑,可以写入数据到发送器。当发送器使能时,这些写入的数据可以自动发送,使得主控计算机在写入数据后不必进一步关注。数据经发送器输出,变成与TTL电平匹配的信号,利用ARINC 429线驱动器,可以方便地与ARINC 429数据总线连接。DEI1016A功能框图如图2所示[3]。

图2 DEI1016A功能框图

■2.1 控制字格式

DEI1016A支持多种操作,这些都是通过向寄存器写入不同数据实现的。在/LDCW信号为“0”逻辑电平时,通过16-bit 数据总线,就可以向寄存器写入数据。

DEI1016A的控制字格式如表2所示,通过这12 bit 的控制字可控制以下功能[4]:

表2 DEI1016A控制字格式与功能

(1)数据字字长(32 或 25 bits);

(2)传输数据第32位(奇偶校验或数据);

(3)环绕自测试;

(4)接收数据的源/目的检测;

(5)发送器奇偶性;

(6)数据发送/接收速率。

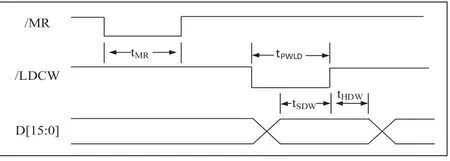

■2.2 DEI1016A芯片复位及初始化

电路上电后,给/MR一个至少200ns的低电平脉冲下,使芯片复位。然后将控制字写入16 位数据总线上,在/LDCW 引脚低电平时,可将控制字写入控制寄存器,然后进行数据的接收和发送,如图3所示。

图3 DEI1016A复位与初始化时序

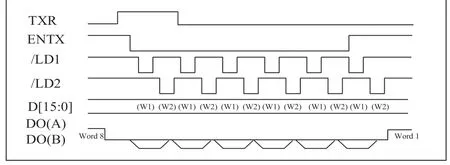

■2.3 数据发送

发送数据时,首先应查询TXR 引脚状态,若是高电平,表明发送存储器已空,可重新装在数据。此时置ENTX引脚为低,置LD1 为低,LD2 为高,则装载数据1,若置LD1为高,LD2 为低,则装载数据2,如此最多可装载8个32 位字长的数据,此时再查询TXR引脚状态,若为低电平,表明发送数据已准备好,置ENTX引脚为高电平即可发送数据。DEI1016A采用的是先进先出的发送顺序[5]。具体发送时序如图4所示。

图4 DEI1016A发送数据时序

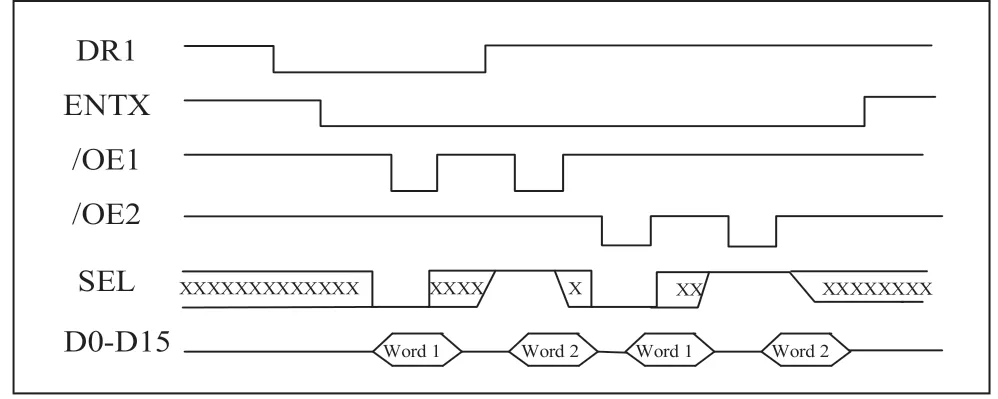

■2.4 数据接收

接收数据时,接收器经过串并转换后,将接收的数据放到寄存器中,每收到一个数据字,发出一个“收到”信号,等待外部命令对此数据的读取。当接收器接收到数据后,系统会置DR为低电平。欲使接收器1将接收数据的字1送至16位数据总线上,应先置SEL为低电平,再置OE1为低电平且置OE2为高。而后再置SEL为高电平,便可将字2送至16位数据总线。具体接收时序如图5所示。

图5 DEI1016A接收数据时序

接收器2操作类似。

3 测试方案

■3.1 测试原理图设计

DEI1016A在泰瑞达J750设备上的测试原理图见图6。

图6 DEI1016A在泰瑞达J750设备上的测试原理图

考虑到J750设备上数字通道支持的电平范围与ARINC 429电平的不匹配情况,我们选择了驱动器BD429,作为连接J750数字通道与DEI1016A的ARINC 429 信号端的桥梁。

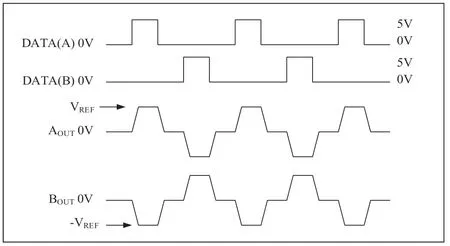

■3.2 ARINC 429 信号电平的产生

利用BD429驱动电路来产生DEI1016A所需要的ARINC 429 差分输入信号。如图5所示, BD429输入端DATA(A)、DATA(B)是TTL电平,即逻辑“1”为5V,逻辑“0”为0V的正逻辑,可以和J750数字通道直接相连,经过驱动后,AOUT、BOUT输出端输出的是ARINC 429差分电平,其值和参考电压VREF有关,如图7所示[6]。

图7 BD429的输入与输出

为了能顺利获得上图中的输出信号,输入端DATA(A)、DATA(B)需有相同周期的脉冲信号,不过DATA(B)的信号相比DATA(A)要延迟半个周期。

■3.3 时钟设置

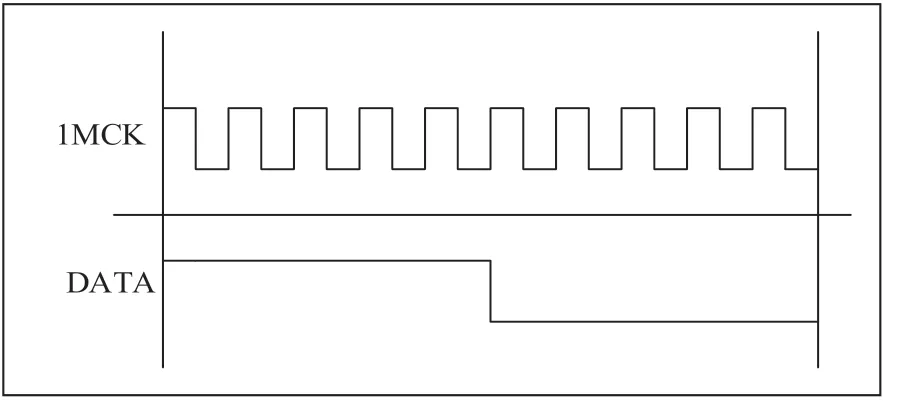

DEI1016A的发送器和接收器的数据的高传输速率为100 kbps,低传输速率为12.5 kbps。数据的发送与接收,共用一个时钟,这个时钟信号通过1MCK引脚从外部输入,工作频率为1MHz。由此可以看出,1MCK主时钟频率与数据端口时钟频率并不相同。对高数据传输速率(100 kbps)而言,1MHz速率是一个×10倍的时钟,对低传输速率(12.5kbps)而言,是一个×80倍的时钟。

一般来说,可以利用外部晶振来解决,但需要考虑晶振与测试设备时钟的同步问题。测试设备J750提供了MCG mode,即Multi-ClockGeneration ,这种模式允许一行向量可以有多个时钟周期,对于解决时钟频率比其它信号频率快的器件非常有用。正常情况下,对同一行向量,对应一个时钟周期,如数字信号DATA。而在MCG mode 下,1MCK时钟有多个周期。如图8所示。

图8 MCG mode 时钟信号

MCG mode的设置,是在Time Sets Sheet中,在Cycle选项中设置CPP的值,同时在Pin/Group选项中,设置Setup为MCG。CPP的值,取决于时钟频率与其它信号频率的关系,对DEI1016A来说,当数据传输速率为100 kbps时,设置CPP值为10,即可实现主时钟频率为1MHz。

■3.4 字间隔

在数据发送时,DEI1016A芯片内部有Word Gap Timer逻辑电路,用来产生字与字之间的4 bit 间隔。在传输完一个字后,4-bit间隔在装载新数据字时自动产生,这样对传输一个32位的数据字来说,至少需要36-bit的时间。

■3.5 向量实现

根据上述功能描述,我们按照相应时序,便可实现发送和接收功能向量。需要注意的是,字与字之间的4-bit间隔,奇偶性设置等。以接收器功能为例,向量如下所示。

■3.6 软件编程

按照J750的标准编程方法,完成对器件的Pin脚定义,通道定义,Pin Levels、 Time Sets、Test Instance、Test Flow等的设置,装载测试向量,即可调试验证程序,实现具体参数和功能测试,具体流程这里不再赘述。

4 结论

本文以DEI1016A为例,基于Teradyne公司的J750测试系统,提出了一种测试解决方案,实现了32位数据发送和接收功能,在对芯片性能评价的应用中取得了较好效果,也为后续解决其它ARINC 429接口电路的测试问题提供了途径。