FPGA 内部资源测试探讨

2022-03-09贺云肖梦燕唐锐

贺云, 肖梦燕, 唐锐

(工业和信息化部电子第五研究所, 广东 广州 511370)

0 引言

由于现场可编程门阵列(FPGA) 器件具有体积小、 能耗低、 高性能、 高可靠性和可重复编程等优点, 所以其在电子通信、 人工智能和军工等领域得以广泛地应用。 从最初的万门级到目前的千万门级乃至更高, FPGA 朝着高集成度、 大规模化方向不断地发展。 如何快速高效、 低成本地筛选出不合格产品, 判断故障类型并实现故障定位具有重要的意义。

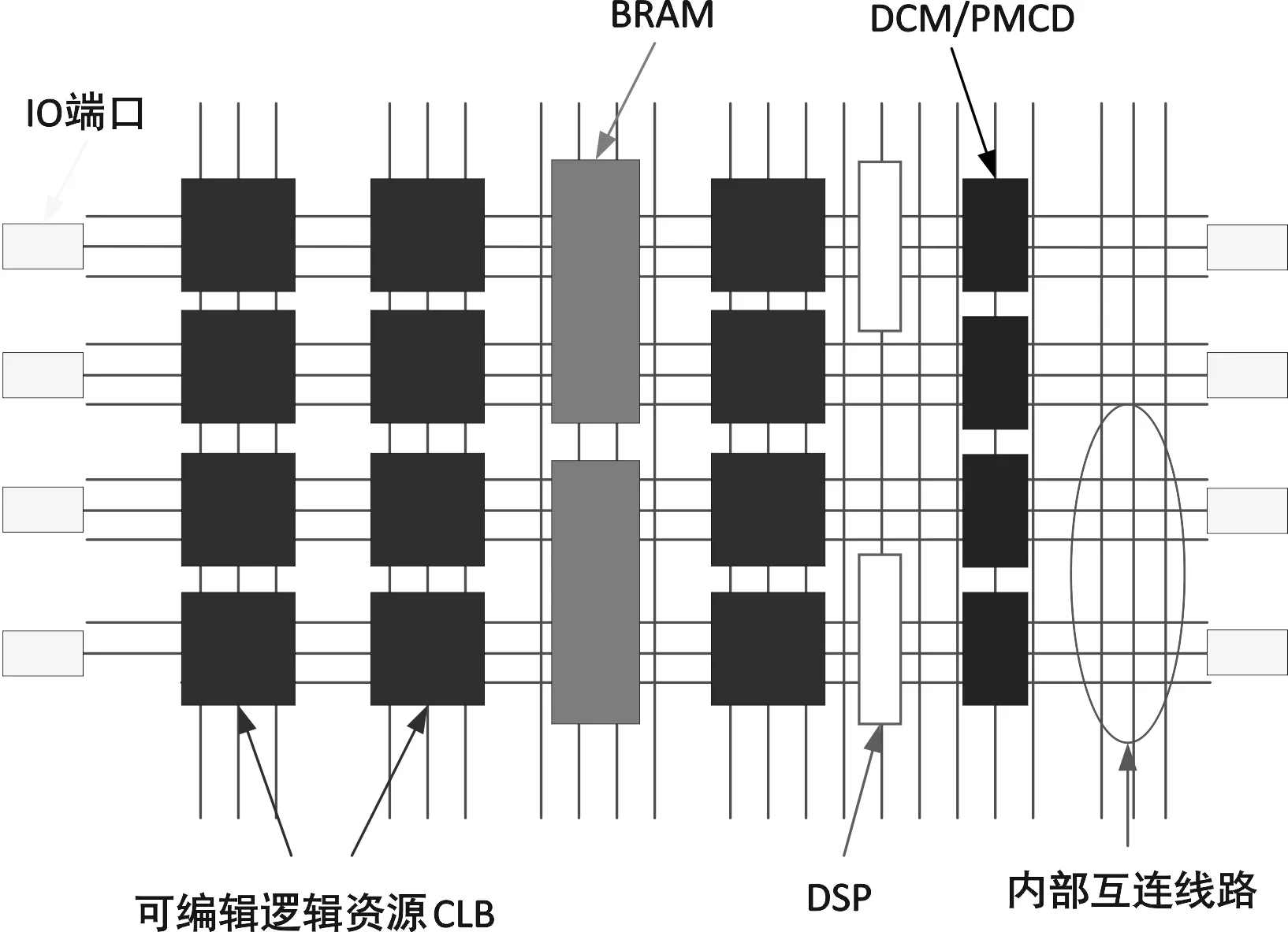

FPGA 的测试是配置后施加测试向量并对输出进行检测比较的过程, 完整的测试需要大量的测试配置。 FPGA 内部包含可编程逻辑资源模块(CLB)、输入输出组(IOB)、 内部互连线路(IR)、 块RAM、DSP 和时钟管理单元(CMT), 以及其他特殊的功能模块, 因此在测试中常采用分治法将FPGA 以模块进行划分, 根据各个模块的典型故障有针对性地选择测试方法。 本文将简要地介绍和总结FPGA 内部各个模块的故障类型和常用的测试方法。

1 FPGA 器件结构与故障分类

1.1 FPGA 基本结构

CLB 是FPGA 中最基本同时也是数量最多的功能模块, 它呈行列状遍布于芯片内部。 以Xilinx 的FPGA 为例, 每一个CLB 均由Slice 组成, Slice 分为普通逻辑单元SliceL 和可配置为存储器的逻辑单元SliceM。 两种Slice 内部的资源类别相同, 均由查找表(LUT) 单元、 触发器(FF)、 进位逻辑及若干与门、 异或门和选择器构成[1]。

IOB 是直接连接芯片内部硅片管脚(PAD) 的输入输出缓冲单元, 在不同的电气标准下对输入/输出信号进行匹配输入或驱动输出, 所有的IOB都就近布置有一组对输入输出信号进行逻辑处理的

IOLOGIC。

岛型FPGA 的内部互连线路(IR) 最初描述为开关盒 (SB) 和连接盒 (CB) 模型[2], 随着FPGA 连线资源的丰富, SB/CB 模型难以描述, 取而代之为开关矩阵(SM) 的结构[3]。 IR 主要包括SM 和金属互连线, 其中SM 主要是由可编程连接点PIP 构成。

BRAM 模块是片内集成的专用双端口可读写存储单元, 分布于CLB 之间, BRAM 功能、 数据位宽、 读写模式、 FIFO 模式和标志信号等可配置。CMT (比如数字时钟管理器DCM、 相位匹配分频器PMCD、 锁相环PLL 和MMCM 等) 实现时钟信号的倍频分频、 时钟偏移、 频率综合和时钟抖动滤波去歪斜等功能。 此外, 为了进一步地加强FPGA性能, 片内还会集成PCIE、 DSP 和乘法器等功能模块。 典型的SRAM 型FPGA 的主要构成如图1所示。

图1 FPGA 内部结构示意图

1.2 FPGA 故障类型

FPGA 芯片内部电路资源种类多, 对应的结构和功能各有差异, 因此表现出的故障类型也不同。一般地, 各个功能模块可能出现的故障有: 固定型故障、 短路故障、 开路故障、 暂态故障和延迟故障等[4]; 此外还有存储资源中的地址译码故障、 转换故障、 字内或位耦合故障、 读写破坏故障和码敏感故障等。

固定型故障是指电路中至少一条线路不论输入什么电平始终固定为逻辑高或低电平, 分为固定1故障和固定0 故障。 常见的有CLB 模块中的查找表断开故障、 PIP 的常开和常闭故障、 IOB 端口的固定高或低电平故障等。

短路故障, 或被称为桥接故障, 常见的有IR中互连线与电源短接、 接地故障和线之间的短路故障等。

集成电路中某些缺陷不能描述为门级的固定型故障, 需要在晶体管级建立故障模型, 定义为晶体管开路、 栅极源极漏极开路等。

不同于固定型故障, 暂态故障表现为瞬态或间歇性, 一般认为由电源电磁干扰、 粒子辐射、 噪声和生产制造工艺不达标等导致。

延迟故障是电路中信号的动态故障, 多为触发和响应时延, 表现为脉冲信号的边沿参数变化等,常发生于IOB 模块、 IR 模块和CMT 模块等, 对电路时序的影响极大, 常归因于元件参数变化或电路结构设计不合理等。

其余故障模式不再赘述, 聚焦于器件的典型故障有助于简化测试工作。

2 FPGA 测试方法

FPGA 的测试有多种分类方法, 比如: 按测试目的分为设计验证测试、 生产测试、 特性分析测试和失效分析测试; 按测试阶段分为晶圆测试、 成品测试和来料检验测试; 按产生配置模型的途径, 又分为面向制造的测试(MTP) 和面向应用的测试(ATP); 按测试内容分为参数测试、 功能测试和结构测试; 按测试激励的生成方式进行分类, 又分为确定性方法、 穷举测试、 伪穷举测试和伪随机测试等。

Toutounchi 等人提出了学术界关于FPGA 测试的参考标准: 1) 测试方法应与具体芯片结构无关,具有普遍适用性; 2) 与芯片阵列规模无关, 容易

推广; 3) 测试方法具有可重复性、 自动化程度高;4) 覆盖率易以统计[5]。

2.1 ATE 测试

FPGA生产企业多以ATE 进行流水线测试, 常用的ATE 机台主要包括ADVANTEST V93000、Teradyne J750 和UltraFLEX。 测试机台均集成高精度电源、 计量仪器、 信号发生器和模式生成器等,可保证测试速度和自动化要求, 操作便捷且易以扩展, 因此, 对ATE 的测试方法和效率提升有着大量的研究。

ATE 测试需反复修改FPGA 配置数据以生成ATE 可识别并执行的测试向量。 配置数据较多时会占用ATE 内部大量的存储资源, 若使用设备商提供的板卡来扩展ATE 的存储深度则是一笔巨大的开销, 通常也使用U 盘、 存储卡、 硬盘和FLASH 存储器作为外部存储介质存储配置数据,不过控制相对复杂, 需要使用专门的控制芯片或占用FPGA 部分资源。

测试时间是测试成本的一个关键因素, 近年来为了缩短测试时间有着大量的研究[6]。

2.2 内建自测试

图2 BIST 逻辑简图

在对部分资源测试完毕后, 通过FPGA 的可编程性将TPG、 ORA 和BUT 模块资源调换, 即可测试另一个部分的资源, 从而能通过若干次配置、 测试覆盖到所有的逻辑资源。

BIST 还分为在线和离线两种模式。 在线测试时芯片正常工作, 主要有并发和非并发两种测试方法: 并发模式下测试与电路正常操作同时进行, 互不干扰; 非并发模式在电路空闲状态下进行, 常用来进行故障诊断测试, 可随时中断。 离线模式对电路的实时故障无能为力。 离线模式也分为功能性离线BIST 和结构性离线BIST。

BIST 可以测试CLB、 IR 和部分内嵌模块。

2.3 边界扫描链测试法

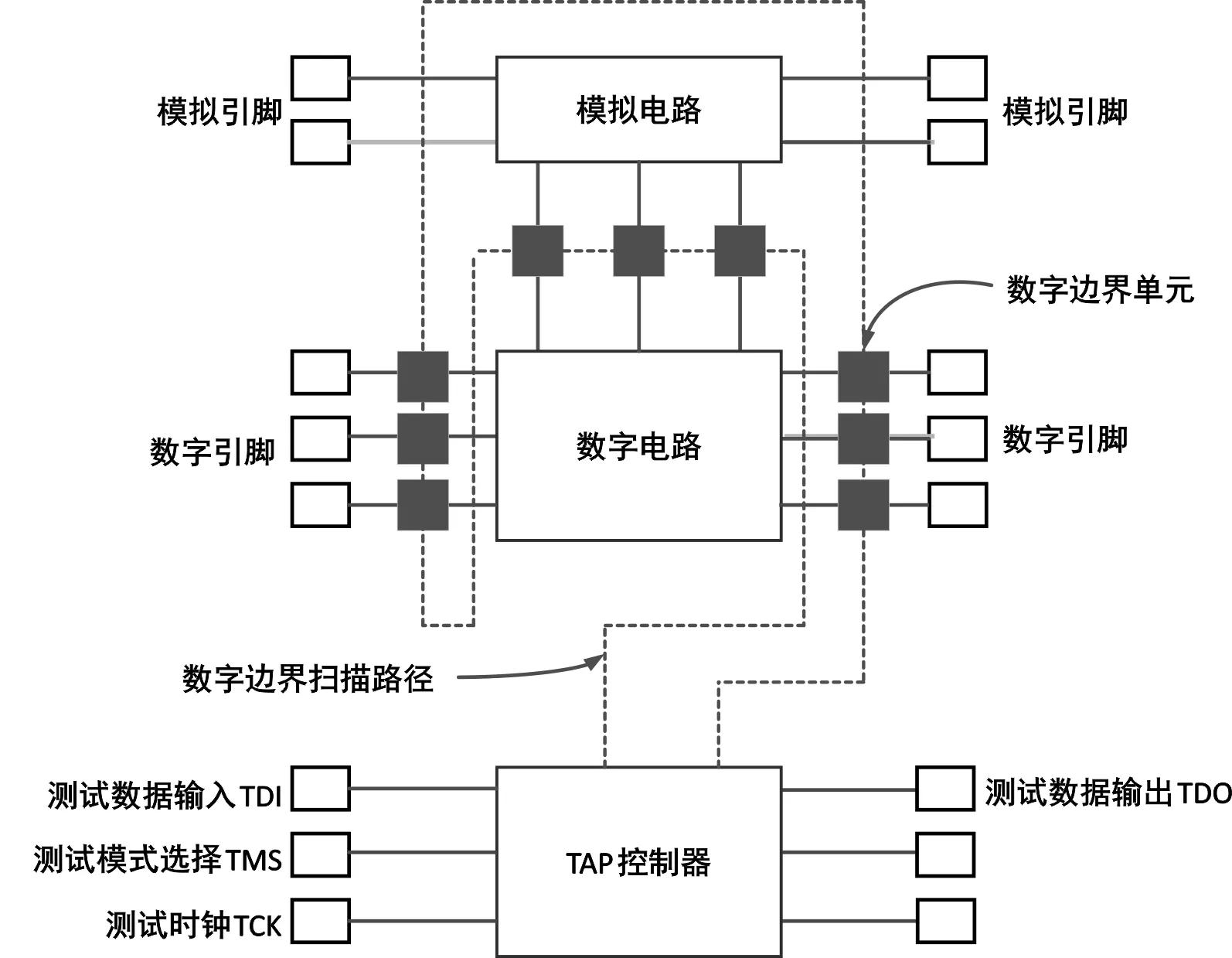

FPGA的配置可以采用两种方法: 1) 将位流文件转换为ATE 可识别的数据文件进行测试; 2) 在测试过程中直接通过边界扫描链(JTAG) 和专用下载电缆, 通过一个专用PROM 将位流配置数据下载到FPGA 中。 边界扫描结构主要由测试存取接口(TAP)、 TAP 控制器和几类寄存器组成[7-8],TAP 包 含测试 模 式 选 择 (TMS)、 测 试 时 钟(TCK)、 测试数据输入引线(TDI)、 测试数据输出引线 (TDO) 和测试重置 (TRST) 5 个端口。TRST 端口非必需, JTAG 结构示意图如图3 所示。

图3 边界扫描结构示意图

要实现芯片的边界扫描测试功能, 芯片内部必须集成有边界扫描模块, 对信号的输入输出处理也要在芯片设计阶段就加以考虑。 此外, JTAG 测试法属于黑盒测试, 只能通过IOB 的输出判定故障是否发生, 无法进一步地实现故障定位, 而且受限于IOB 数量导致操作时配置难度较大。

3 CLB 测试

CLB 资源较多, 除了与或等基本逻辑外还可配置为查找表 (LUT)、 函数发生器、 RAM 或FIFO、 触发器/锁存器和移位寄存器等, 实现加乘法、 快速进位链和高速串并-并串转换等高级逻辑功能。 CLB 模块功能通过将所有的电路单元划分为不同的功能电路进行测试。

3.1 LUT

CLB 数量大且呈行列分布, LUT 测试可将FPGA 中一列LUT 单元级联成链进行。 要对电路中所存在的固定型故障、 开路故障、 桥接故障、 译码故障和转换故障等进行100%覆盖测试共需(K+1)种电路配置方式, 其中K 是LUT 输入端口数目[9]。LUT 可用存储器的测试方法进行, 但也需要考虑其特殊结构。 要将SRAM 存储单元测试完整, LUT需要配置为ROM、 RAM 两种架构, 先测RAM 再测ROM, 因为ROM 其实是通过SRAM 来模拟的(把ROM 的数据写进SRAM, 接受后关断写数据和写地址译码功能, 只保留其读功能, 形成ROM模式)。

鞋子华丽、高贵,这在以前,李若定然是发狂地欢喜,这是她梦寐以求的事。可是当她真的站在琳琅满目的橱窗前,心却是灰的。

3.2 可配置寄存器测试

Slice 内的存储单元可以配置为边沿触发的D触发器和电平敏感的锁存器, 都包含专门的使能端(CE)、 清零端(SR) 和时钟输入(CK) 等。 可配置寄存器故障主要为功能性故障[10], 需测试CE 功能、 初始值设置功能、 SR 置位和RS 复位功能,以及它们的组合并保证故障能被检测到。

CE 功能测试从输入端施加CE=0 或CE=1 来测试固定故障。

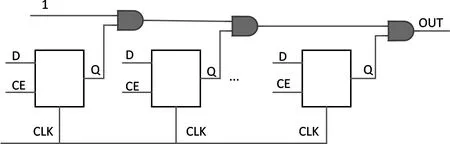

初始值设置和置位复位功能采用路径扫描法,输入端的输出与1 相与或与0 相或后作为下一级输入往下传递, 通过固定故障进行判断。 以设置初始值1 为例, 如图4 所示, 将n 个寄存器输出值与1相与, 结果作为下一级与门的输入, 与下一级寄存器的输出相与, 一旦不能初始为1, 则寄存器输出值为0, 激活固定0 故障。

图4 寄存器初始化1 功能配置示意图

当然也可以采用位流回读技术进行测试, 直接对触发器/锁存器施加测试信号, 读取响应值进行故障判断, 但过程繁琐, 难度较大。

3.3 快速进位逻辑测试

由进位信号和函数复用器组成的进位逻辑可以进行快速的加减法运算, 进位逻辑链可以显著地提高CLB 模块的处理速度。 常见的故障为功能性故障, 表现为逻辑进位失效, 因此测试时将所有的逻辑配置为全加器, 串联在一起测试, 根据输出值来判断故障。 需要设置对应的数据发生器、 比较器和移位寄存器等配合测试完成。

3.4 分布式RAM 功能测试

LUT 单元除可配置为函数发生器或ROM 外,还可配置为分布式RAM 和移位寄存器使用。 LUT存储数据在前两种模式下只能通过芯片配置时序初始化设定, 而分布式RAM 模式下可通过SliceM 中写电路进行修改。 与函数发生器或ROM 相比, 分布式RAM/移位寄存器拥有译码电路及控制电路,其余部分如LUT 内部存储单元完全一致, 因此只需对写控制电路功能进行测试。

测试中可以使用March 算法来覆盖固定故障、开路故障、 转换故障、 地址译码故障和耦合故障。

4 IOB 测试

IOB 是FPGA 与外部进行数据交互的接口, 在不同的电气标准下对输入/输出信号进行驱动输出或匹配输入。 通过配置每个IOB 所对应的IO 逻辑资源可实现单双边信号的输入输出、 高速串并输入、 高速并串输出和输入输出延迟等功能。

IOLOGIC 的功能测试按照其功能分为: 单端输入输出功能电路、 差分输入输出功能电路、IDELAY 模块功能电路、 IDDR 功能电路、 ODDR数据输出和三态控制输出功能电路。 IOB 故障主要为固定故障、 短路故障和三态故障, 可以通过各个管脚的漏电流进行故障判断, 也可以通过边界扫描和阵列法进行测试。

5 内部互连线路测试

在FPGA 中, IR 占据了50%~90%的芯片面积和60%以上的信号延迟。 互连资源主要包括SM 和互连线, 因此故障主要分为开关故障和线的故障。

开关故障有常开和常闭两种。 开关常开可以理解为开关两端的线桥接在一起, 即单线常开。 线的故障分为单线和多线情况。 单线情况有单线断路、与电源桥接和与地桥接, 多线情况还有线之间的短路故障即多根线之间的桥接[11]。 金属互连线的覆盖率测试极大地影响到FPGA 的性能和安全, 在实际电路中, IR 的故障率也大于CLB。

目前针对IR 资源测试算法的研究较为深入, 3次配置测试算法基于IR 的布线规律, 采用一次正交配置和两次斜向配置, 能够完全覆盖所有的互连金属线和开关盒中的PIP, 但该算法基于XC4000系列, 不适用于Virtex-4 及之后系列且不具备故障定位功能。

在3 次配置基础上发展出6 次配置测试算法,通过增加配置次数来实现故障定位, 但同样不适用于Virtex-4 及之后系列[12]。 也有研究基于图论相关思想, 结合深度优先算法和启发式搜索算法等完成配置图形生成[13]。

BIST 也被应用于IR 测试中。

6 BRAM 测试

BRAM 模块是FPGA 中集成度较高的资源, 可被配置为单端口RAM、 双端口RAM、 内容地址存储器和FIFO 等常用的存储结构, 可以根据设计需求改变存储位宽和深度[14]。 常出现SRAM 故障、双端口读写故障、 位宽模式故障、 级联功能故障、 ECC 功能故障、 FIFO 功能及标志位故障和初始化功能故障等7 种故障[9]。 其核心电路SRAM 存储序列可能出现的故障有地址译码故障、 固定型故障、 开路故障、 转换故障、 写破坏、 读破坏和耦合故障等, 被统称为SRAM 故障。

在BRAM 功能的测试中, 采用多种测试算法对各种故障进行全覆盖测试。 常用的算法有MSCAN、 GALPAT、 步进码序列、 棋盘法、 蝴蝶法、 March 及其改进算法 (March SS、 March s2df 和March d2pf 等)、 ATS 及其改进的MATS 和MATS+等。 比如: 使 用MSCAN 算法对BRAM 的初始化功能进行验证, 算法对SRAM 阵列中的故障进行测试,使用算法对BRAM 双端口读写故障进行测试, MATS+算法对各种位宽模式故障及Cascade 功能ECC 功能故障进行测试。

6.1 MSCAN 算法

MSCAN 算法形成固定的存储器扫描序列, 对所有的单元进行全0/1 的读写, 用于检测固定型故障。 后续测试需在BRAM 初始化功能无误的情况下进行。

6.2 March SS 算法

March SS 算法用于覆盖SRAM 故障及最大位宽模式的BRAM 读写功能故障, 在实际的使用中,March SS 算法前经常先通过初始化算法排除了固定型故障。 March SS 算法对于1 位宽度数据之间的读写破坏故障、 地址译码故障及耦合故障已实现100%覆盖, 当将其扩展到多位位宽时, 需考虑读写数据字内的耦合故障。 由于FPGA BRAM 模块不同位宽模式使用相同的存储阵列, 所有的SRAM 故障测试中不需要扩展算法到多位位宽, 但在BRAM多位位宽读写功能测试中需考虑字内耦合故障。

6.3 MATS+算法

MATS+算法用于ECC 功能测试中, 即升序写0→升序读0→升序写1→降序读1→降序写0。 在FPGA 中需将两个BRAM 组合成72 位位宽模式才能使用ECC 功能。

如果电路规模为N, 部分算法的复杂度和可检测的故障如表1 所示。

表1 存储器测试几种常用算法对比情况

7 其余资源测试

FPGA内部还集成有DSP、 乘法器和CMT 等功能模块, DSP 和乘法器的测试类同CLB, 主要采用边界扫描和位流回读技术。 FPGA 中DCM、 PMCD等时钟管理单元数量少, 集成度高且原始输入信号少, 测试中可直接在其输入引脚输入10~200 M 频率范围内的时钟信号, 测试其输出时钟的频率相位。 PMCD 模块四输入时钟信号CLKA、 CLKB、CLKC 和CLKD 之间保持45°的相位关系以测试模块的相位匹配功能。

8 结束语

FPGA 高度集成化, 内部资源结构复杂, 各个功能模块的故障表现不一, 在测试过程中需要大量的配置文件, 测试成本高。 本文从FPGA 的基本结构出发, 简要地总结和概述了CLB 模块、 IOB 模块、 IR 模块、 BRAM 模块和内部其余功能模块的常见故障, 在此基础上根据分块测试的原理, 针对每个模块梳理了目前常见的测试方法并适当地加以比较和归纳。 本文的研究成果可用于市场上主流FPGA 的测试工作中。