某通信设备激励模块自检偶发报故的分析与解决措施

2022-03-02肖琳

肖 琳

(中国电子科技集团第十研究所,四川 成都 610036)

0 引言

随着通信技术的飞速发展,越来越多的通信设备被应用到日常生活中及各个领域。其中激励模块作为通信系统中发射的组成部分主要完成信号的上变频并产生激励信号,为了提高电路稳定性,简化维修过程,BIT自检作为检测发射电路是否正常工作的重要手段被广泛应用于航空电子设备中,其性能的好坏直接影响着通信的质量,因此合理的设计对信号质量有着重要影响。

1 激励模块硬件架构[1]

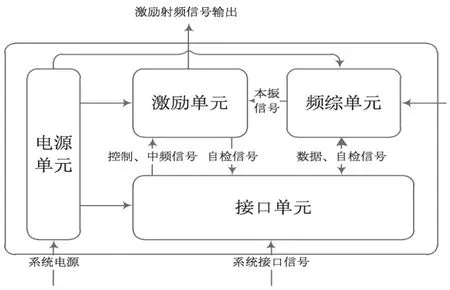

激励模块架构由电源单元、频综单元(含高本振和低本振)、激励单元及接口单元组成(如图1所示)。

图1 激励模块架构图

(1)电源单元提供各种直流电源以供模块内各单元正常工作所需。

(2)频综单元产生模块工作所需的本振频率信号。

(3)接口单元完成模块与系统接口的驱动电平转换,完成模块与系统的通信接口协议处理,并按模块内部射频电路的要求,提供对射频模块的内部控制。

(4)激励单元对中频信号进行变频,放大和滤波处理,最后产生射频信号输出。

2 BIT工作原理

系统通过CAN总线向通用激励模块下发上电自检指令,模块接口单元接收并解析指令信号随即启动模块上电BIT模式。接口单元产生PTT控制信号给激励单元,将激励单元置为发射状态,同时输出中频信号给激励单元,并在10 ms以后结束发使能信号;接口软件在PTT信号发出10 ms时开始采集硬件检测后输入的激励指示信号,判断是否正常工作,判断完成后锁存结果,等待系统下发BIT结果查询ICD后,上报BIT结果[1]。

图2 模块上电BIT运行流程图

3 故障定位分析

3.1 故障单元定位

根据故障现象和超短波激励模块自检原理建立故障树,如图3所示。激励模块自检报故可分为电源故障、激励单元故障、接口单元故障和频综单元故障四类单元级故障。

图3 激励模块自检报故故障树

根据实验室故障复现后的回传记录数据,对比数据解析得知自检过程中模块本振、电源、接口电路正常,激励单元故障,进一步对激励单元故障进行排查。

3.2 单元故障排查

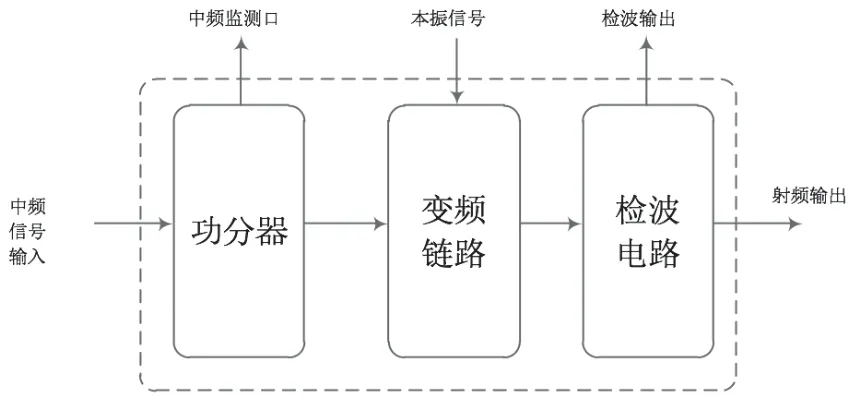

激励单元由功分器、变频链路、检波电路三部分组成,其工作流程如图4所示。中频信号由接口单元产生并送至激励单元,经功分器二分后,一路送至中频监视口;一路送至变频链路,经变频链路滤波、放大、变频后形成射频信号,经检波后输出。

图4 激励单元工作流程图

利用示波器检测模块自检时功分器输出信号,幅度、频率均正常。然后检查变频链路输出,射频信号频率、幅度均正常,排除功分器与变频链路的故障,需要进一步对检波电路进行排查。

3.3 电路故障排查

激励模块软件接收到上电BIT命令后将PTT信号置为发射状态,同时向DA输出中频信号,中频信号经过功分器、变频链后到达检波电路。

测试检波电路输入激励信号幅度、电压均正常,满足设计要求,可以正常输出激励检测信号。

PTT信号发送后第10 ms时,接口软件开始采集从检波电路输出的激励指示信号,进行故障判断。

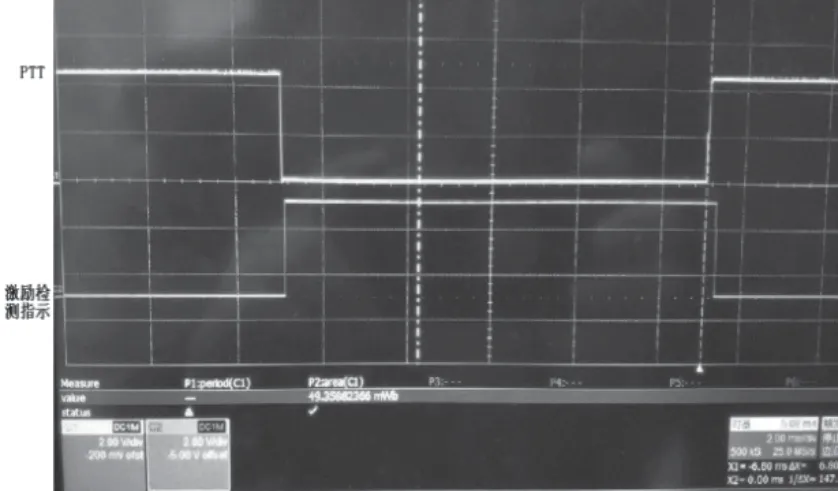

用示波器检测自检过程中BIT控制信号与激励指示信号见图5。自检期间,PTT开关控制信号为低电平,表示发使能信号,激励检测指示信号为高电平,表示在此期间硬件有检测到激励信号输出。由此确定自检期间PTT开关及激励指示信号正常,BIT控制功能正常。

图5 BIT控制信号与激励指示信号

由于电路存在响应时间,PTT使能无效后,激励检测指示信号仍有一段时间有效,如图6所示。

图6 PTT使能信号与激励指示信号的时间差

于此同时,软件开启BIT功率指示信号检测判断(原则为5判3,即采集5次功率指示判断,若大于3次则认为功率发起,否则则判断功率未发起)。由于采集从功率发射结束开始,采样时间间隔约为140 μs,进行5次采样,前3次采样约在280 μs内完成,当故障发生时,PTT无效后功率约在275 μs处变为无效,导致采样只有2次信号有效,通过5判3机制,判定激励无效。因此软件上传BIT故障结果,系统自检报故。

3.4 故障确定

综上所述,由于功率检测是在功率发射结束时刻进行采集判断,软件检测时间与指示信号有效时间临界,从而导致功率检测时误判,进而导致激励模块自检时报BIT故障。

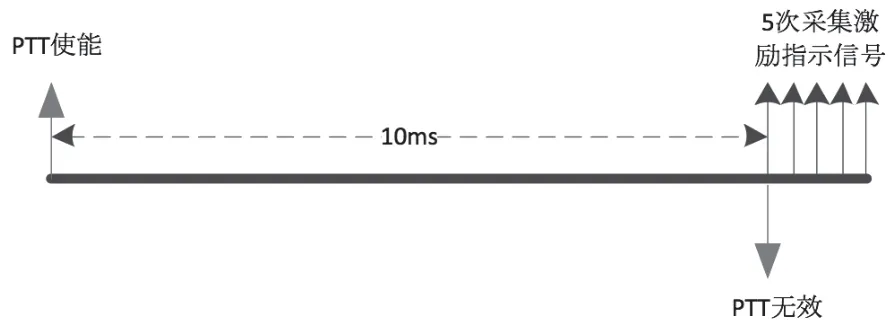

4 机理分析

UCE软件BIT过程判断激励是否故障的时序见图7,上电启动BIT自检后,软件控制PTT信号使能,同时输出检测所需信号给链路,经链路处理后输出至检波电路,在PTT使能后10 ms时PTT关闭,同时软件开始采集功率指示信号,原设计为了保证采集准确性,一共采集5次,软件内实际采集间隔时间约140 μs,判断逻辑为只要有3次以上的采集结果则为有效,判断激励正常,否则判断为激励故障。

图7 激励故障BIT过程

链路发射时,PTT开关开启(电平拉低),发射信号经过通道时延后到达发射末端的耦合器,检波器对耦合器输出的信号功率进行检波,得到检波电压U1,U1通过运放电路放大后与设定的电压U2进行比较,当U1大于U2时,信道上报电压输出为高电平,表示激励指示信号有效;当链路不发射时,PTT开关关闭(电平为高),U1会逐渐降低,经过时间t后,U1小于U2,此时信道上报电压输出为低电平,表示激励指示信号无效。

这里的时间t主要由通道时延、检波器响应时间、运放电路响应时间三部分构成。信道时延主要由晶体滤波器、跳频滤波器时延等组成,为固有时间,时延大约为47 μs;运放比较电路的响应时间为固定时间8 μs;而检波器响应时间主要有检波器外部配置的滤波电容决定。

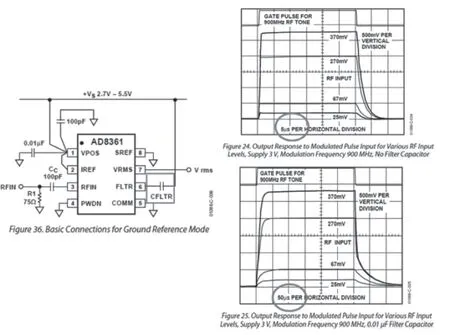

根据器件AD8361的资料[2],需要在期间的第6脚FLTR配置一个电容来降低调制滤波器的转折点频率。如图8所示,当不匹配该电容时,脉冲信号终止后大约经过5 μs检波电压下降;配置0.01 μF的电容后,脉冲信号终止后大约100 μs检波电压才下降。该电容的大小将较大程度地影响信号终止后的检波器响应时间。

图8 检波器配置滤波电容响应时间

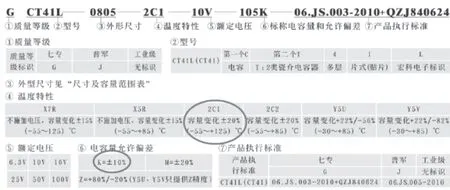

在该信道设计中,该位置的滤波电容选用的是0.1 μF(GCT41L-0805-2C1-50V-104K)的电容。根据器件资料(图9)[2],该电容容值偏差为±10%,高低温(-55~125°C)下电容量变化为±20%。在环境试验下,考虑到极限情况,电容的容值偏差为±30%,即该电容的容值范围为0.07~0.13 μF。

图9 电容容量偏差与温度变化特性

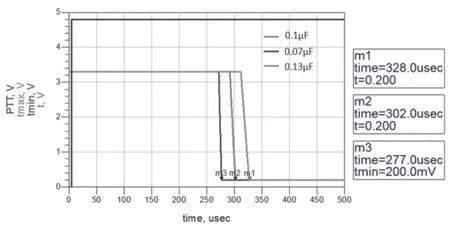

在电容的该范围下对检波链路进行仿真,加上信道时延和运放电路响应时间,得到了PTT无效后信号降为低电平的仿真时间,如图10所示,由于电容的容值范围变化,整个PTT无效后的响应时间范围为277~328 μs。

图10 PTT无效后信道响应时间

当因使用环境、器件的差异,出现在PTT信号无效后,激励检测指示信号有效时间低于280 μs时,则会导致模块采集5次中的第3次采集指示信号无效,不满足3次采集有效地判断,判定为故障;而当模块激励指示信号在PTT开关使能无效后仍然保持有效地时间超过280 μs时,5次采集中第三次采集指示信号有效,满足5次中3次有效,判定为正常。

综上,由于软件采样时间设计不合理,导致检测时间与指示信号有效时间为临界值,从而激励检测误判,出现上电BIT偶发报故。

5 改善措施

为了纠正上述采样时间的缺陷,提出2种方案:①将采集激励指示信号的时间提前,留够足够阈值,以确保采样时刻激励检测信号的准确、稳定。②增大检波器第6脚的滤波电容,延长PTT信号无效后激励指示信号的有效时间,进一步延长有效采样时间。

综合来看,检波器滤波电容的调整会对调制滤波器转折频率、BIT响应时间造成影响,且该产品在产数量较大,电容更换工艺流程较烦琐。将采样时间提前则不会对其他指标造成影响,且不会产生实际采购费用,决定采用第一种方案。

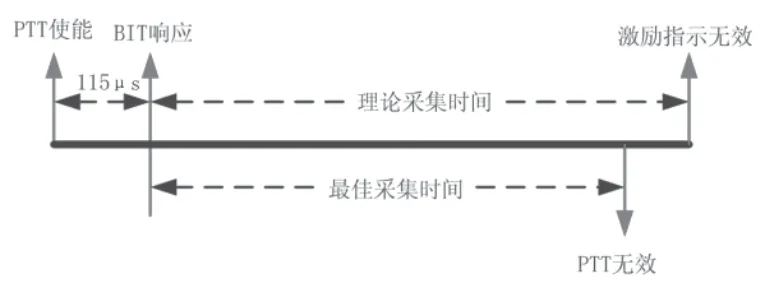

要提前采样时间,首先要确定有效采样的时间范围。从PTT信号的有效开始,到激励指示信号的正确建立,发射信号经过通道延时后到达耦合器,检波器对耦合信号功率进行检波,得到检波电压U1,再利用运放对U1进行放大后与设定电压U2比较,经过时间T后,当U1大于U2时,信道上报高电平指示信号,这个时间T称为BIT响应时间。

对电路进行仿真,加上信道时延和运放电路响应时间,得到了PTT有效后信号变成高电平的仿真时间如图11所示,由于电容的容值范围变化,整个PTT有效后的BIT响应时间范围为68~115 μs。

图11 PTT有效后信道响应时间

根据仿真结果表明激励指示在PTT信号有效后115 μs内已经稳定。最佳指示信号采集时间范围就应该是BIT响应后到PTT无效之间这一时段,如图12所示。

图12 指示信号采集时间范围

从设计角度考虑,在总的模块BIT时间10 ms不变的情况下,将采集激励指示信号的时间折中处理,在保证采样时刻激励的正确性的同时,又留有足够阈值,将采集开始时间设置在BIT启动后PTT使能5 ms时,同样采用5判3原则作故障判断,在10 ms BIT结束时再关闭PTT开关。修改之后的流程如图13所示。

图13 修改后的采样时序

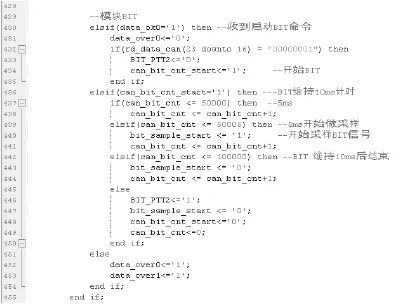

参照图15的思路对激励模块的逻辑处理软件进行修改,修改前后代码对比如图14、15并进行验证。

图14 修改前相关代码

图15 修改后相关代码

6 结论验证

(1)将故障模块的软件烧录修改后的程序,对比同样故障但未修改过软件程序的模块,做反复做上电BIT,修改过程序的模块没有出现报故,未修改程序的模块依然偶发报故。

(2)将该修改过程序的模块重新烧录回修改前的版本,重复做上电BIT,出现BIT结果报故的现象,故障复现。

(3)对该模块进行相关模块指标测试,随后将其进行系统测试,包括接收、发射相应指标、功能测试,测试结果表明功能正常。

(4)为避免自检期间采样时间与指示信号有效时间出现临界值,导致误判报故,修改软件版本,对该批次及后续交付的激励模块进行软件修改、升级。

7 结束语

本文针对综合通信设备中激励模块BIT偶发报故的故障进行分析,逐级排查,列举各级工作原理,最终定位故障;得出故障原因为采样时间的设置没有系统地考虑到激励指示信号的有效时间,将采样时间设置到了指示信号临界点,导致系统误判,出现自检偶发报故;推导了自检过程中指示信号的最佳采样时间,以此为思路,对软件采样相关部分进行了修改。■