基于FPGA的空调显示设定器程序升级方案设计

2022-02-17田地李康乐杨春宇

田地,李康乐,杨春宇

(西安中车永电捷通电气有限公司,陕西西安,710016)

0 前言

2016年7月,国家发展改革委、交通运输部、中国国家铁路集团有限公司联合发布了《中长期铁路网规划》,勾画了新时期“八纵八横”高速铁路网的宏大蓝图,即以沿海、京沪等“八纵”通道和陆桥、沿江等“八横”通道为主干,城际铁路为补充的高速铁路网。“八纵八横”可实现相邻大中城市间1-4小时交通圈、城市群内0.5-2小时交通圈。随着“八纵八横”铁路网络建设有序推进、逐步完善,使我国高速铁路网络四通八达。加之高速动车组有载客量大、速度快、到点准时、乘坐舒适、行驶平稳、受雷雨等恶劣天气影响较小等特点,成为越来越多的人出行交通工具的首选。高速动车组优异的舒适性不仅体现在行驶平稳性上,其精确的车厢温度控制与通风控制也是重要的原因之一。

空调显示设定器作为动车组列车空调运行控制的核心部件,广泛应用于我国CRH2系列、CRH380系列等动车组上,其主要功能为接收列车网络(TCMS)下发或自身按键手动设置的空调运转模式、控制温度等指令信息,进一步传输至空调微机室实现车厢空调系统温度、风量等控制。同时将空调运行状态、温度信息、故障状态上传至列车网络,并且同步在空调显示设定器面板进行显示。以上功能逻辑是由控制器通过软件实现的,我国幅员辽阔、高速动车组线路长、自然环境复杂多变,为适应不同的线路环境,对于空调系统控制逻辑的优化更改在所难免。当前在运营动车组空调显示设定器均由国外进口,更改软件依赖于国外厂家,存在更改费用高、响应周期长的弊端。在进行升级作业时,需拆开显示设定器面板,升级完毕后需进行面板安装恢复,做紧固标记,作业时间较长。本文基于FPGA芯片的国产化空调显示设定器,创新性的提出了通过串口升级FPGA程序的方案,使升级作业效率大幅提高,节省了人力成本,缩短作业时间。

1 系统方案

由于空调显示设定器需同时与列车网络、两组空调微机室实时通信,并及时响应空调控制指令,还需响应面板与按键操作,同步执行复杂的控制逻辑,因此控制器性能成为方案设计重要因素之一。FPGA以并行执行,可重复、灵活配置等优势,成为国产化显示设定器主控芯片的首选。按照设计要求,空调显示设定器外部需预留串口作为数据下载接口,故本方案不再额外增加接口,设计数据下载与程序升级公用同一串口。根据功能评估结果,本文选取Xilinx公司Spartan6 系FPGA作为主控芯片。因为FPGA基于SRAM结构,配置文件掉电会丢失,需要在外部配置存储介质进行配置文件存储或通过额外的处理器进行配置文件写入。Spartan6系列FPGA程序配置方式可分为主模式(Master Modes)、从模式(Slave Modes)、JTAG模式。根据存储介质接口的不同又可细分为主串、主并、从串、从并等模式。

1.1 主模式

主模式即FPGA作为主设备,存储介质作为从设备, FPGA的CCLK引脚给存储介质提供工作时钟,上电后FPGA将主动从存储介质中读取程序配置文件,典型的模式可分为PROM模式和SPI-Flash模式,具体介绍如下。

①主串模式-PROM

FPGA作为主设备,Xilinx PROM作为从设备。此方案需要通过JTAG将配置文件烧写至PROM中,FPGA上电后将主动从PROM中读取配置文件。DIN与CCLK管脚在程序配置完成后可作为用户IO使用, PROM成本相对较高。

②主串模式-SPI Flash

此模式下需FPGA外部配置SPI Flash,FPGA作为主设备,SPI Flash作为从设备。配置模式选择后, FPGA上电时主动从SPI Flash中读取程序文件,MOSI、DIN、CSO_B、CCLK等信号在FPGA配置完成后可作为用户IO使用,串行Flash的特点是占用引脚比较少,器件封装小,容量大,不但可以节约电路板空间,还能降低功耗核噪声。存储程序文件的同时也可用作用户数据存储。

③主并模式-NOR flash

此模式下FPGA外部需配置并行NOR Flash, FCS_B等接口信号,在程序引导完成后,也可以作为用户IO使用,并行NOR Flash占用FPGA管脚数量较多。

④主并模式-并行PROM

并行PROM模式下FPGA作为主设备,并行PROM作为从设备,配置文件可通过JTAG写入PROM中,FPGA上电时,主动从并行Flash中引导配置文件,引导完成后,配置管脚可作为用户IO使用,此方案特点是占用FPGA管脚资源较多成本较高。

1.2 从模式

从模式根据外部处理器接口分为从并模式和从串模式。

①从串模式

即FPGA作为从设备,需要外部处理器通过串行接口将配置文件写入FPGA。

②从并模式

即FPGA作为从设备,需外部处理器通过并行接口将配置文件写入FPGA,虽然从模式不需要额外的存储介质,但需要外部额外配置处理器进行配置文件写入,成本较高,增加了开发难度。

根据项目应用场景要求,控制板卡安装在显示设定器箱体内,显示设定器整体安装于动车组车厢电气柜中,在实际运营、程序升级作业时,一般禁止打开显示设定器面板,故通过JTAG升级配置文件方案不能满足要求,若使用从模式配置程序文件,需额外增加处理器,增加了成本和开发工作量。主模式里,PROM成本高于SPI Flash,串行SPI Flash接口比并行FLASH简单,节约FPGA管脚资源。综合考虑,本项目使用主串配置模式,选择SPI Flash作为存储介质,通过FPGA数据手册可知,SPI接口MOSI、DIN、CSO_B、CCLK在程序配置完成后可以做用户IO使用,则当程序引导完成后,FPGA可以操作上述接口操作SPI Flash。那么通过显示设定器外部DB9接口,就可以使用PC把程序配置文件下发至FPGA,FPGA将配置文件缓存后,再写入SPI flash,从而实现配置文件自升级功能。

1.3 硬件方案

结合研发成本与工作量本项目总体方案设计如图1所示,系统主控芯片采用Spartan6系列FPGA,SPI Flash选用成本较低的M25P32,需要进行配置文件更新时,通过PC上位机将BIN文件下发至FPGA,FPGA完成SPI FLASH擦除后,边缓存配置文件,边通过SPI驱动将数据写入Flash,从而完成程序文件更新,文件写入完成后,只需空调显示设定器重新上电,新程序即可完成配置。

图1 系统硬件方案

2 软件实现

本方案软件部分包括上位机软件和FPGA软件两部分。

2.1 FPGA软件

FPGA实现与上位机通信,接收上位机升级指令及程序文件数据并进行数据缓存、实现SPI Flash 驱动管理、程序文件的flash写入等功能,软件模块架构简图如图2所示。

图2 软件结构模块

波特率生成模块:根据系统时钟生成目标波特率,提供数据发送接收模块使用,作为异步串行通信的协议基准。

数据接收模块:对串行RX信号的起始位、数据位、停止位进行识别与判断、完成奇偶校验并进行数据串并转换。

数据发送模块:对并行字节数据进行并串转换、补充起始位、校验位、停止位数据,配合波特率模块完成TX串行数据发送。

指令数据解析模块:对接收到的数据帧进行解析判断及校验,如果是升级指令,将指令转发至FLASH控制逻辑模块,完成FLASH擦除等程序升级准备工作。如果是程序数据,将数据写入文件接收双口RAM中进行缓存。

双口RAM:因为接收数据速率与写FLASH速率不一致,使用双口RAM对程序文件的缓存,起到Flash和上位机数据间桥梁和数据缓冲的作用,本项目使用IP核利用BRAM生成FPGA内部双口RAM。

FLASH控制逻辑模块:根据指令完成SPI-Flash读、写、擦除命令生成,包括各寄存器指令、读写擦除流程控制,读、写、擦除、程序文件写入完毕的判断,是整个升级流程的“指挥官”。

SPI驱动模块:按照M25P32数据手册中对于读写时序要求,完成SPI控制协议时序实现。

(1)串行通信协议

本项目与PC的串行通信波特率为57600bps,数据位8位,起始位1位,偶校验。

(2)FLASH 驱动实现

M25P32具有32Mb容量,时钟频率最高支持75MHz,支持256bytes页编程,整个空间由64个扇区组成,每个扇区包含256页,每页包含256bytes数据,M25P32支持扇区擦除和整片擦除。SO8封装的M25P32共有8个引脚,驱动的实现主要是跟据数据手册相关要求,操作相应管脚高低电平,各电平必须符合读时序、写时序要求。本项目SPI Flash在完成配置后,时钟信号作为用户IO由FPGA提供,频率选用5MHz,占空比50%,所有接口信号执行均有较大裕量,满足时序要求。

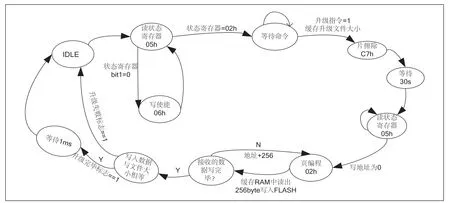

(3)升级软件处理逻辑

软件处理逻辑如图3所示,FPGA内部使用状态机编码实现,状态机包含有上电读状态寄存器、等待命令、执行片擦除、页编程等。当接收到程序升级命令后,先对SPI Flash执行整片擦除操作,因擦除时间较长,内部BRAM容量有限,需完成擦除后再开始接收配置文件数据,一边接收数据写入内部双口RAM中,一边进行SPI Flash页编程操作,直到全部配置文件数据写入完毕。并对上位机下发的文件大小与接收的文件大小进行对比,若文件大小比照正确后,向上位机返回升级完毕指令,若对比失败,则向上位机返回升级失败提示,重新进行上述升级流程即可。

图3 升级软件处理逻辑

2.2 上位机软件

本项目上位机软件使用NI公司Labview软件进行开发,界面分可为数据下载、软件升级、时钟设定等功能,进入界面后会首先会选择波特率等串行通信协议参数。

数据下载:可下载空调机组运行数据,并生成EXCEL格式文档,方便对空调机组运行情况进行查看,便于故障定位分析,此功能非本文重点,不再赘述。

软件升级:用于选择FPGA配置文件所在位置、下发FLASH擦除指令、对BIN文件进行大小计算并分包下发、判断是否升级成功。

时钟设定:可重置空调显示设定器内部时钟芯片。

3 验证

(1)整体实物图

图4为空调显示设定器实物与上位机界面图,可以看出显示设定器与上位机通过USB转RS232串口线进行连接,通过操作上位机软件,选择正确的异步串行通信协议,操作简单的菜单即可完成FPGA程序升级。

图4 空调显示设定器实物图

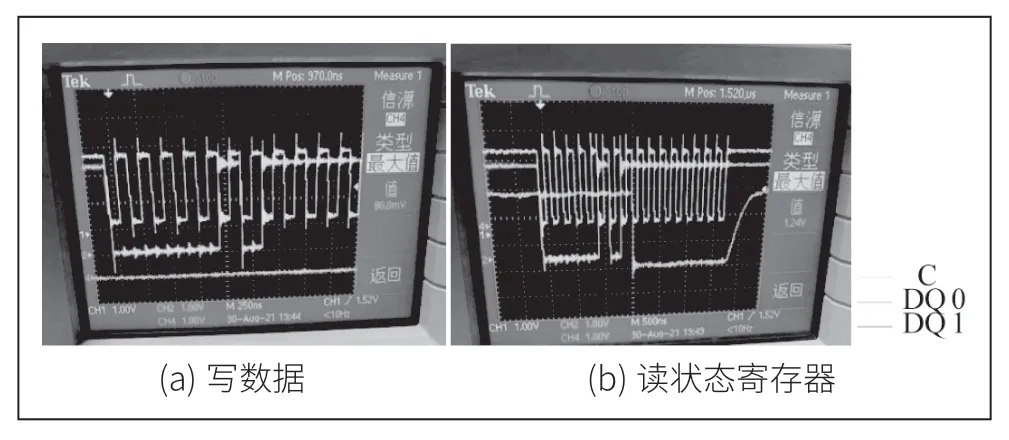

(2)驱动实现

图5所示为SPI驱动时序实测图,读写数据的时钟频率5MHz,占空比50%,时序满足要求,相较于数据手册时序要求,均有较大裕量,对于Flash的读写擦除均可稳定执行。

图5

(3)上位机

图6为程序升级完成后上位机提示框,表示程序升级完成并且升级成功,此时需对显示设定器进行重新上电,新的配置文件即可加载。若提示框显示升级失败,则重新选择文件,再次执行升级步骤,直至提示升级结束。

图6 上位机升级完成界面

4 结语

本文设计了基于FPGA的空调显示设定器程序自升级方案,通过与数据下载功能共用串口进行程序文件升级,使升级流程极大简化,升级作业不需要打开空调显示设定器机箱盖板,只需通过串口线连接电脑即可升级,方便快捷,提升了售后服务效率,单人即可完成操作,缩短了升级作业时间,节省了人力成本,目前本方案设计空调显示设定器已在380AL车型载客运营2年,性能稳定。