基于FPGA的EnDat协议绝对式光栅尺通讯实现

2022-02-06柯帮维杨志军阳志林白有盾

柯帮维,杨志军,彭 皓,阳志林,白有盾

(1.广东工业大学,精密电子制造技术与装备国家重点实验室,广东广州 510006;2.佛山市华道超精科技有限公司,广东佛山 528225)

0 引言

随着科学技术的进步,高端机器人、数控机床、雷达等行业对伺服控制系统要求越来越高[1-2]。位置编码器反馈精度直接影响伺服控制系统的定位精度,因此在高精密运动领域对位置编码器要求越来越高。常用的位置编码器有增量式、绝对式和混合式编码器[3-5]。增量式编码器价格相对便宜,然而每次掉电后都要重新找零点,并且有误差累积现象。另外,受到采集卡截止频率限制,增量式编码器存在速度与精度的矛盾,无法应用在高速度高精度运动控制场合。相比较而言,绝对式编码器每一个位置都有固定的编码值,零点固定、无累积误差、数据可靠性高。

绝对式位置编码器主要有SSI、Biss-C、EnDat等传输协议[5-8]。其中EnDat协议可靠性高、传输速度快、抗干扰性强。

通常,单片机、FPGA或者ASIC都可以与EnDat编码器通讯。然而,单片机一般适用于EnDat时钟频率较低的场合。ASIC对于确定功能和大规模批量生产的产品有优势,但是编程灵活性较低。FPGA具有并行特性、灵活性高和快速处理数据的能力。综合考虑,本文采用FPGA来实现EnDat协议通讯。

本文分别从EnDat协议的时序分析、硬件电路设计和软件各模块设计进行介绍,并把位置信息和部分参数通过串口发送到上位机显示。实验测试结果表明FPGA与EnDat协议的光栅尺正常通信。

1 EnDat协议时序分析

EnDat接口是面向编码器应用的双向数字接口,带有错误检测位和CRC校验功能,并且EnDat 2.2协议可以发送附加数据的位置值,以便系统实时监控编码器反馈状态,使得编码器的数据传输可靠性高[9]。

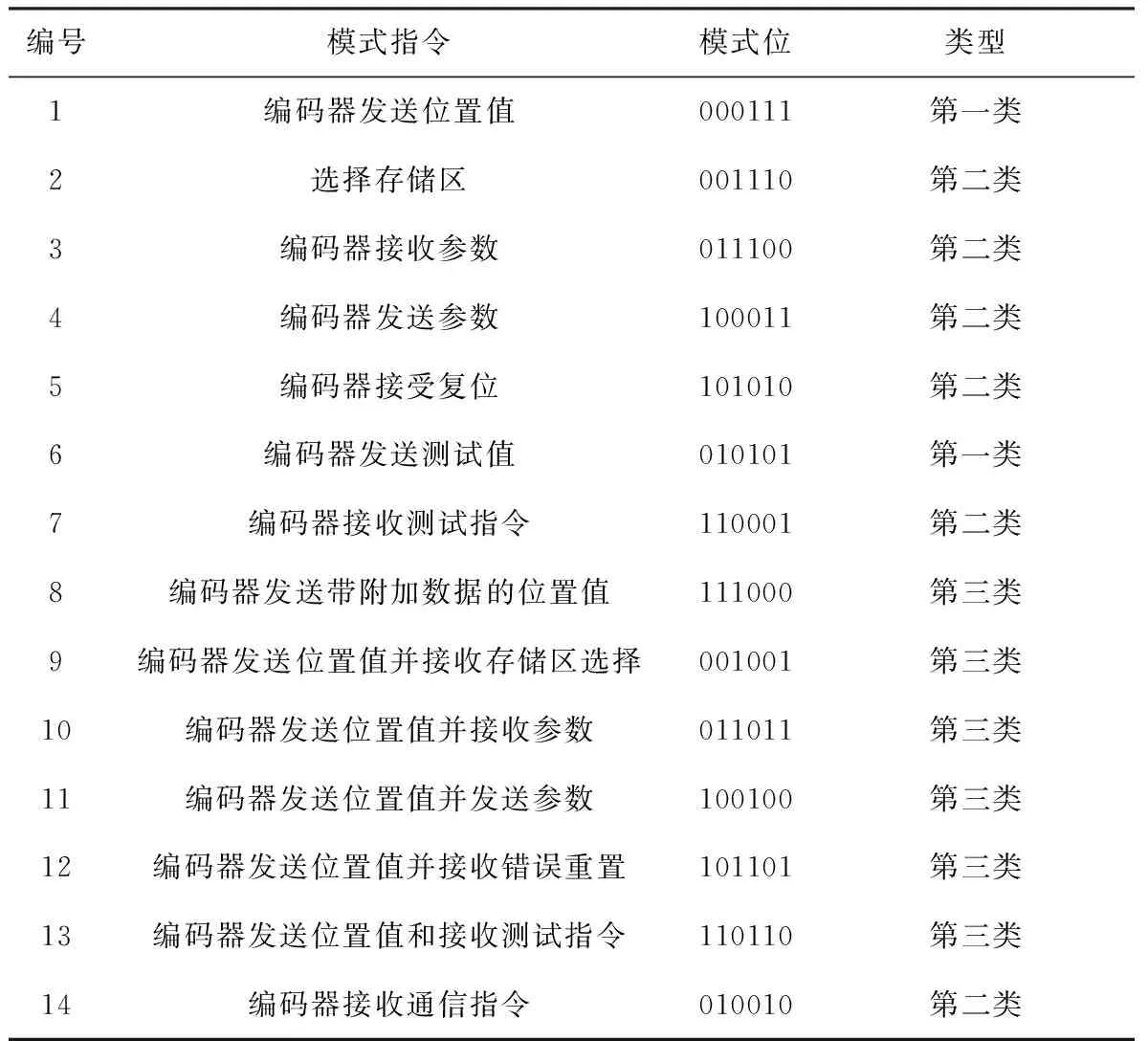

EnDat 2.2协议有14种指令,如表1所示,FPGA可以通过这些模式指令读取编码器的位置、存储器信息、OEM等参数[10-11]。EnDat 2.2协议在EnDat 2.1协议上扩展了7个指令,使得附加信息可以和位置信息一起传输。

表1 EnDat指令表

如表1所示,本文把EnDat 2.2协议的模式指令划分为第一类、第二类和第三类。其中主机发送第一类模式指令后只接收位置或测试值;而通过第二类和第三类模式指令可以读取或者修改编码器的参数。本文以第一类为例介绍,时序如图1所示。传输过程为主机发送模式指令给光栅尺后,光栅尺返回“Start”位和“Error 1”位,紧接着是nbit的位置值或40 bit的测试值,最后是5 bit的CRC码。

图1 第一类时序图

具体通信请求如下:

(1)空闲时,主机保持时钟线为高电平,当光栅尺保持低电平时表示光栅尺已经准备就绪。

(2)位置请求信号到来时,主机拉低时钟信号并保持tst时间的低电平后,连续输出固定频率的时钟信号。同时主机在第2个时钟信号的下降沿开始发送模式指令。

(3)等待光栅尺准备数据,直到光栅尺返回1个“Start”位后,主机在时钟的下降沿读取光栅尺返回的数据。

(4)光栅尺发送完数据后,主机拉高时钟信号,并一直保持高电平。

(5)当光栅尺返回数据信号为低电平时,则主机可以进行下一次读取请求。

2 系统软硬件设计

2.1 硬件电路设计

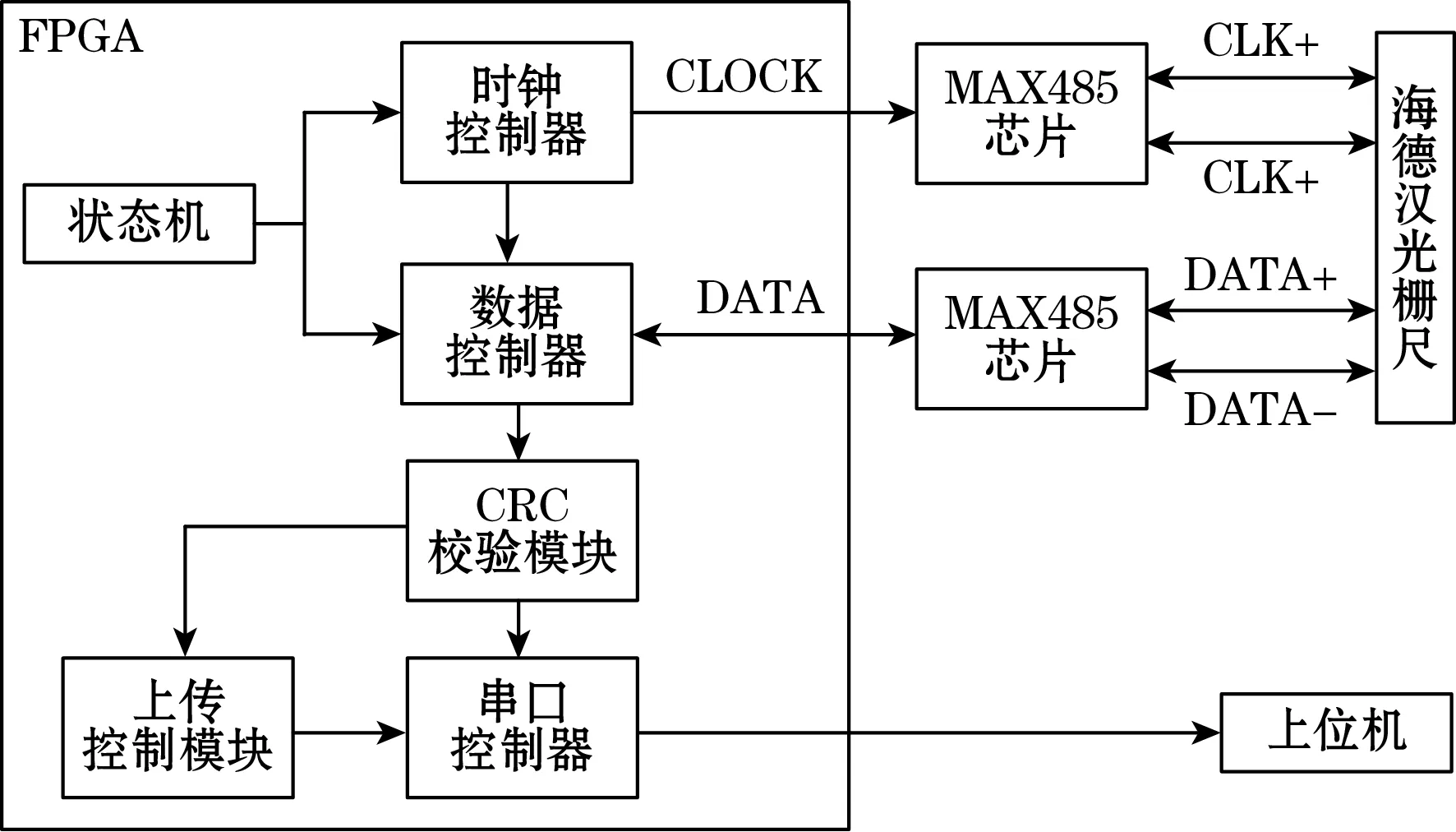

硬件系统由FPGA(Cyclone IV系列芯片EP4CE10F17C8)和绝对式光栅尺构成,该绝对式光栅尺的时钟信号和数据信号都是RS485差分驱动信号,因此需要电平转换电路。

硬件电路如图2所示,采用电平转换芯片MAX485对时钟和数据信号进行处理,使得TTL电平与差分信号RS485电平得以相互转化。光栅尺的时钟线和数据线经过电平转换芯片后再与FPGA控制板连接,FPGA端生成的CLOCK、DATA信号经过MAX485芯片把TTL电平转为差分信号输出给光栅尺。另一方面,光栅尺返回的DATA信号经过MAX485芯片把差分信号转为TTL电平发给FPGA。FPGA通过串口与上位机进行通讯,上位机可以发送命令给FPGA,FPGA接收命令后把采集到的位置和参数依次发送给上位机,上位机把接收到的位置进行描点画图。

图2 差分信号转换电路

2.2 软件系统设计

本文设计的数据采集系统控制流程如图3所示。系统主要由时钟控制器、数据控制器、CRC校验模块、上传控制模块和串口控制器构成。时钟控制器作用是产生光栅尺需要的不同频率的时钟信号。数据控制器根据时钟信号同步发送模式指令、MRS码、存储器地址、参数给光栅尺,以及接收光栅尺返回来的位置、参数、附加数据。时钟控制器与数据控制器都是在状态机预设的状态下产生时钟和收发数据。FPGA把从光栅尺采集到的数据经过CRC校验后,再通过串口控制器发送到上位机显示。上传控制模块作用是控制数据上传到上位机的频率,使其满足串口的通讯速率要求。

图3 采集系统框图

根据EnDat 2.2协议的时序特点,本设计用状态机实现光栅尺数据采集过程,总共分为8个状态,状态机的工作方式如图4所示。系统在默认情况下处于空闲状态,输出高电平的时钟信号。当接收到请求信号en_flag时,状态跳转到同步状态,同时拉低CLOCK信号。同步状态下CLOCK一直保持低电平,直到计数到给定的tst后跳转到模式指令发送状态。在模式指令发送状态下,FPGA在第2个时钟的下降沿开始发送模式指令或地址、参数。

图4 系统采集状态机

FPGA发送完模式指令后,状态跳转到等待状态。当光栅尺返回来一个“Start”位,状态跳转到数据接收状态。由于光栅尺在CLOCK的上升沿开始返回数据,因此FPGA应当在CLOCK的下降沿读取数据,防止在电平转换期间读出错误的数据。第1、第2类EnDat 2.2模式指令在接收完数据后拉高CLOCK信号,直接进入恢复状态。当光栅尺DATA信号从高电平转换为低电平,表明光栅尺可以进行下一次位置请求。此时状态机跳转到默认状态,等待下一次请求信号。第3类模式指令(除了111000)在接收完位置和附加数据后进入地址发送状态,FPGA在CLOCK的下降沿发送地址、MRS码、参数值,发送完成后进入恢复状态。在恢复状态下,如果检测到错误位Error 1置1,或者Error 2置0,说明有错误出现,状态跳转到复位状态,复位完成后进入默认状态。

FPGA接收完数据后会产生一个done信号,并把接收到的位置、CRC码传输到下一层CRC校验模块。CRC校验模块在接收到done信号后开始对位置值进行CRC校验运算。光栅尺的CRC多项式为6’b101011。为了提高数据处理的效率,充分利用FPGA并行处理的特性,CRC校验模块采用并行CRC校验算法,只需1个系统周期就完成CRC码的校验[12-13],主要代码如下:

crc_out[0]= d[32]^ d[30]^ d[27]^ d[26]^ d[24]^ d[23]^ d[22]^ d[17]^ d[15]^ d[12]^ d[11]^ d[9]^d[8]^ d[7]^ d[2]^ d[0]^ c[2]^ c[4];

crc_out[1]=d[32]^d[31]^d[30]^d[29]^d[27]^d[25]^d[24]^d[21]^d[17]^d[16]^d[15]^d[14]^d[12]^d[10]^d[9]^d[6]^d[2]^d[1]^ d[0]^ c[2]^ c[3]^ c[4];

crc_out[2]= d[31]^ d[30]^ d[29]^ d[28]^ d[26]^ d[24]^ d[23]^ d[20]^ d[16]^ d[15]^ d[14]^ d[13]^ d[11]^ d[9]^ d[8]^ d[5]^ d[1]^ d[0]^ c[3]^ c[4];

crc_out[3]= d[32]^ d[29]^ d[28]^ d[26]^ d[25]^ d[24]^ d[19]^ d[17]^ d[14]^ d[13]^ d[11]^ d[10]^ d[9]^ d[4]^ d[2]^ c[0]^ c[2];

crc_out[4]= d[31]^ d[28]^ d[27]^ d[25]^ d[24]^d[23]^d[18]^d[16]^d[13]^d[12]^ d[10]^ d[9]^ d[8]^ d[3]^ d[1]^ c[1]^ c[3];

其中d[32∶0]是接收的数据从高位到低位是32 bit position+Error 1。c[4:0]初始值为5’b11111;crc_out[4∶0]是用CRC校验模块对数据d[32∶0]进行计算得到的校验码。把接收到的crc_code与取反的crc_out比较,如果两者一致,则输出一个高电平脉冲的crc_done信号,同时把接收正确的数据输出给下一模块。否则丢弃该数据,等待下一次校验。

3 上位机软件设计

MATLAB-GUI图形化界面设计工具提供各种基本控件和各种函数库接口、支持RS232/RS485串口通信,可以直接利用按钮、可编辑文本、坐标区等控件直接组成上位机的图形界面,并利用回调函数实现上位机的功能[14-16]。因此本文利用MATLAB-GUI设计上位机实现串口通信、图形显示、发送命令等功能,并提供良好的人机交互界面。

由于光栅尺的位置有32位,而串口通信一次只能发送8位数据,因此在FPGA端把位置值拆分为4组8位的数据,分4次依次通过串口发送给上位机,上位机再把接收到的数据进行拼接。最后把拼接完的数据在坐标区绘制图形。

4 功能测试仿真

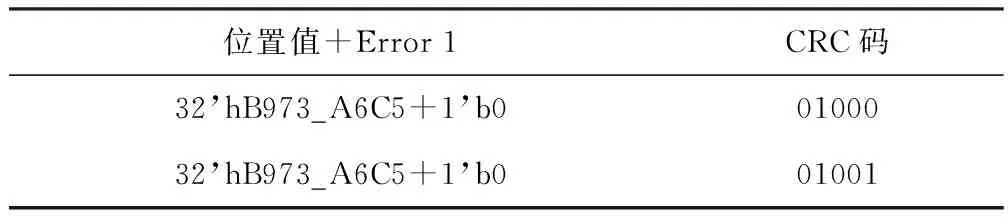

为了验证FPGA程序的正确性,编写测试文件模拟光栅尺,通过Modelsim仿真工具验证各模块是否正常工作。本文以模式指令为000111为例,在测试文件中模拟光栅尺准备了2组数据,如表2所示。分别为2组32位的位置值+1位的Error 1+5位的CRC,其中第1组的CRC校验码的最低位与第2组是相反的,并且第2组CRC码是正确的。因此可以根据接收的位置和CRC码测试数据控制器以及CRC校验模块是否正常工作。

表2 Modelsim仿真数据表

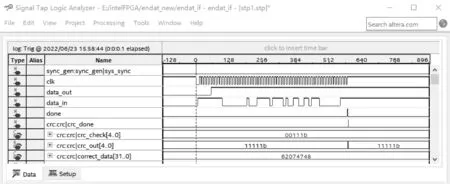

仿真结果如图5所示,当en_flag信号使能时,时钟控制器输出5 MHz的clk信号给光栅尺。数据控制器在时钟的下降沿通过data_out发送模式指令,测试文件接收到指令后,在时钟的上升沿通过data_in返回数据。当数据控制器接收完数据后会产生一个done信号,并进入CRC校验模块。

图5 模式指令为000111的Modelsim仿真图

图5的check_data为接收到的数据,check_data由32位的位置值+1 bit 的Error 1组成,高位在前、低位在后。从图中可得,数据控制器正确接收位置状态信息和CRC码,由于第1组接收到的CRC码和实际的CRC码不一样,所以第1组数据没有产生crc_done信号。而第2组数据产生crc_done脉冲。综上分析,CRC校验模块、时钟、数据控制器各模块正常工作。因此设计的EnDat协议程序通过仿真验证。

5 实验结果与分析

把仿真测试成功后的程序下载到FPGA板卡上,并把光栅尺连接到FPGA上。本次实验通过发送模式指令000111,读取光栅尺的位置值,验证程序。本实验通过Quartus Prime的Signal Tap Logical Analyzer抓取FPGA内部信号,如图6所示。图6的data_in和data_out分别代表光栅尺发送给FPGA的数据信号、FPGA发送数据给光栅尺的串行数据信号。

图6 Signal Tap Logical Analyzer捕获图(模式指令为000111)

从图6可知,当FPGA接收到请求信号en_flag时,clk信号立刻拉低并正常工作;当接收到完成信号done后,clk停止工作并一直保持高电平。数据控制器控制data_out和data_in正常工作,并把接收到的位置信息输入到CRC校验模块,CRC校验模块产生crc_done信号,说明接收到正确的位置并且整个采样周期在40 μs之内。经过以上分析,图6的波形图符合EnDat协议的时序,校验模块也能正常工作,程序验证成功。

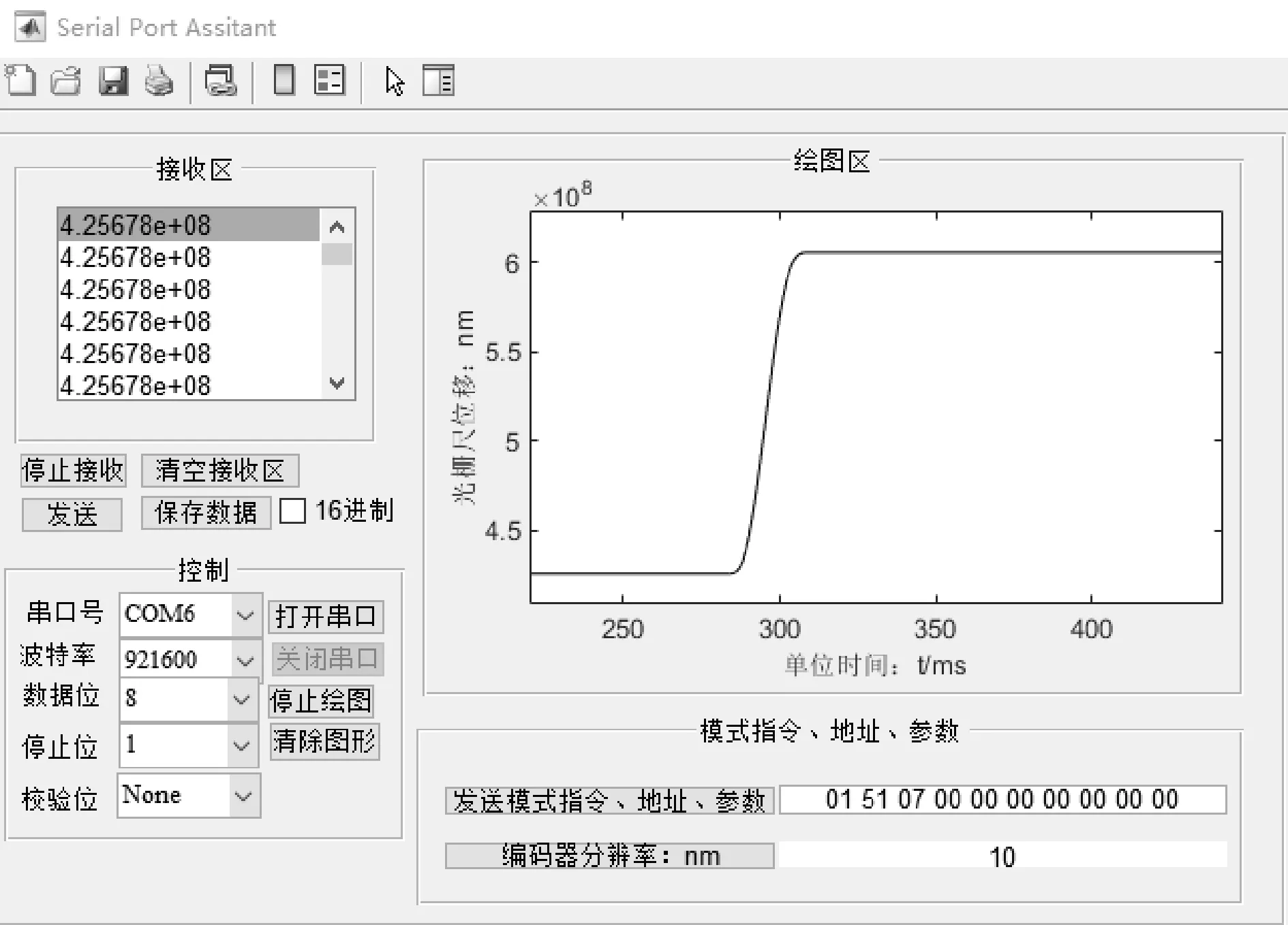

为了更直观观察采样的位置信息,通过串口控制器把校验正确的位置发送到上位机显示。如图7所示,上位机能够正确接收数据并描点绘图。

图7 上位机采集数据图

6 结束语

本文根据光栅尺的EnDat协议时序设计了硬件电路和FPGA控制程序,并开发了上位机实现位置数据采集和绘图功能。FPGA控制程序适用于EnDat 2.1、EnDat 2.2的模式指令,具有并行CRC校验功能,这样不仅提高了程序的通用性还缩短了工作周期。由于FPGA具有并行的特性和强大的数据处理能力,还可以在该程序的基础上扩展采集多路光栅尺数据。实验结果表明,设计的FPGA程序可以与EnDat协议的光栅尺进行通讯,并且能够把采集到的位置值通过串口发送到上位机进行显示。