基于信息技术的电子密码锁的系统电路设计

2022-02-06张鹏骞

张鹏骞

(河北省儿童医院,河北 石家庄 050031)

0 引 言

随着人们安全意识的不断提高,防盗问题引起人们的重视,传统的机械锁已经很难满足人们的要求,智能锁应运而生,它们有着不同的特点,但是也有着智能锁共同的缺点。例如,手部问题会影响智能指纹锁识别、应用场景有限以及卡片钥匙成本高等。这些问题得不到解决,智能锁在一定程度上很难得到普及应用和推广。而电子密码锁由于保密性高、使用灵活性好、安全系数高,受到了广大用户的认可[1]。

1 电路的功能模块设计

AT89C51作为本系统的微控制器,是整个电路的核心部分,晶振频率采用6 MHz,使单片机的运行速度不至于太快[2]。系统由键盘、发光二极管(Light Emitting Diode,LED)显示电路、开锁驱动电路及报警电路组成。开始运行工作时,操作员或者用户可以从键盘敲入6位密码,待按下确认功能键后,单片机会将输入的密码同原始设定的6位密码进行判断校验。若键盘敲入的密码同设定的6位密码一致,则发出开锁指示信号,绿灯闪亮,开门;若密码错误,就会有相应的红灯亮起,这时需要重新输入密码。原程序设计输入密码的次数超过3次或者3次以内密码都提示输入错误,就会触发报警指示信号。另外,电子密码锁成功打开后,程序还设定了对密码的修改功能,以便于重新设置新密码。

1.1 密码输入及显示电路

本设计从系统功能扩展考虑,保留串行通信口,采用单片机外接扩展输入输出(Input/Output,I/O)接口芯片8155H实现6位LED显示和矩阵键盘接口电路。8155H的输入输出口地址是FF20~F23H,其中PA口是控制键盘列线扫描的输出口,也是6位共阴极显示器的位扫描口,显示器的段码(字码)口为PB口,键盘行线状态的输入口为PC口[3]。

因为按键比较多,所以在设计上采用了行列式的键盘。每1条横线(行线)与竖线(列线)的交叉点都不是相通的,而是通过1个按钮连接起来,利用这种行列式矩阵结构只需要M线和N线就可以组成一个键盘,上面有M×N个按钮。此外,显示电路采用动态方式,将所有位的段码线对应的段并联在一起,由1个8位I/O口控制,形成多路复用的段码线,而每个共阴极分别由对应的I/O线控制,形成各自的分时选通。

1.2 AT24C02掉电储存模组设计

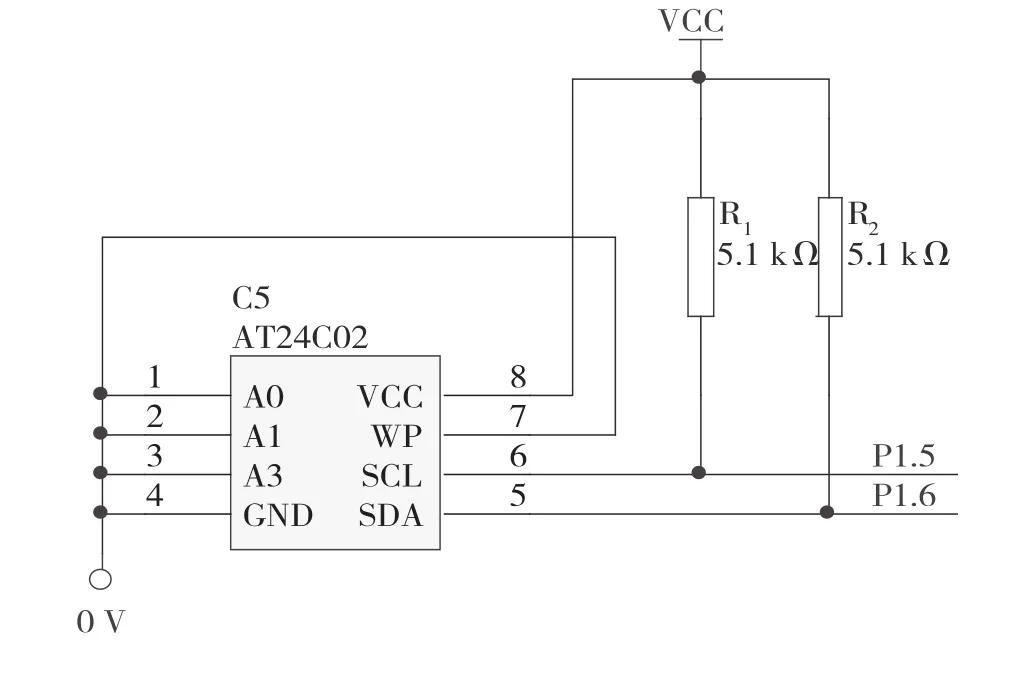

AT24C02是电可擦除存储芯片,限制的最低电压为2.5 V,限制约束的正常工作电流为1 mA,静态电流为10 μA(5.5 V)。芯片内的资料可储存约40年之久,同时以8脚双列直插式(Dual In-line Package,DIP)的形式封装,以便使用[4]。其电路如图1所示。

图1 AT24C02掉电存储模块设计

图1中的R1、R2为上拉电阻,其设计能够减少AT24C02芯片的静态功耗。由于AT24C02芯片的数据线和地址线是复用的,因此采用串口的方式传输数据,只用2根串行时钟线(Serial Clock,SCL)和串行数据线(Serial Data,SDA)与单片机传送数据,其中SCL用于输入输出数据的同步,在上升沿时串行写入数据,在下降沿时串行读取数据;SDA用于串行数据的输入输出。

1.3 AT24C02的寻址

一般微处理器/微控制器称为主器件,产生串行时钟和起始停止信号。带电可擦除可编程ROM(Electrically Erasable Programmable Read Only Memory,EEPROM)工作在从机方式,称为从器件[5]。无论是主器件还是从器件,都可以充当发送器或接收器的角色,由主器件来控制数据的传输。

主器件发送启动信号后,再发送1个8位含有芯片地址的控制字对从器件进行片选[6]。这8位片选地址字由3部分组成:第1部分是8位控制字的高4位(D7~D4),固定1010是集成电路总线(Inter-Integrated Circuit,IIC)的特征编码;第 2部分是最低位D0,即读写选择位R/W,决定微处理器对EEPROM进行读写操作,R/W—=1表示读操作,R/W—=0表示写操作;第3部分即A0A1A2,本设计设A0A1A2为000。

1.4 AT24C02的时序分析

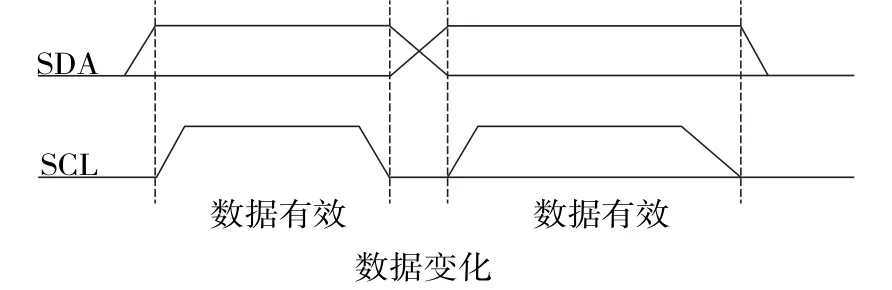

AT24CXX EEPROM存储器采用二线制传输,遵循IIC总线协议[7]。SCL和SDA的时钟关系与IIC协议中规定的相同。加在SDA的数据只有在串行时钟SCL处于低电平时钟周期时才会发生变化,如图2所示。

图2 AT24CXX SDA和SCL时钟关系

当SCL处于高电平时,SDA由高电平向低电平转变时表示启动信号,由低电平向高电平转变时表示停止信号,启动与停止信号如图3所示。

图3 AT24CXX启动和停止信号

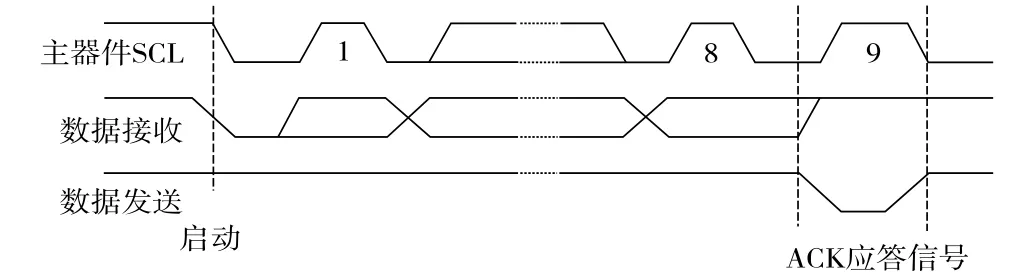

应答信号由接收数据的存储器发出,每个正在接收数据的EEPROM收到1B数据后,需发出1个“0”应答信号ACK,单片机接收完存储器的数据后也需发出1个应答信号。ACK信号在主器件SCL时钟线的第9个周期出现。

在应答时钟到达第9个周期时,SDA线变为低电平,表示1个8位数据已经收到。若主器件没有发送1个应答信号,则器件将停止数据的发送,且等待1个停止信号。应答信号如图4所示。

图4 应答信号

1.5 AT24C02读操作

采用顺序读操作来得到用户设定的密码。顺序读存在2种地址读的情况,一是立即地址读,二是随机地址读,无论采用哪种地址读的方式都可操作启动。随机地址读通过1个“伪写入”操作形式对要寻址的EEPROM存储单元进行定位,然后执行读出。要想达到主器件对存储器无限制、无顺序的字节进行读操作,可以采取随机地址读的方式,器件和信号流即主器件首先发送起始信号、从器件地址、读取字节数据的地址,执行1个“伪写入”操作。在从器件应答之后,主器件重新发送起始信号、从器件地址,此时。从器件发送1个应答信号之后,输出所需读取的1个8位数据,主器件发出应答信号,告诉从器件需发送更多的数据,与每个应答信号相对应。当确认器件为主器件时,发出的信号收到至确认是停止信号时,运行结束。从器件输出的数据按顺序从N到N+I,地址计数器的内容相应相加,计数器也会产生翻转继续输出数据。

1.6 AT24C02写操作

采用页面写操作将修改后的密码保存到EEPROM中。主器件发出启动信号和从器件地址给从器件,从器件收到信号确认为应答信号后,主器件再选择从某个指定的器件中以字节地址的形式传输发送信号,从器件将再发送另一个相应的应答信号,主器件收到信号后向被寻址的存储单元发送数据,传送1B后,主器件并不产生停止信号,而是发送15个额外字节。每发送1个数据后,从器件发送1个应答位,并将地址低位自动加1,高位不变。

当存储器的WP引脚接高电平时,将存储器区全部保护起来,可以避免用户操作不当对存储器数据的改写,将存储器变为只读状态。

1.7 报警控制模块设计

本系统密码输入错误超过3次以上将启动延时报警模块。由单片机的P1.4端控制压电蜂鸣器的发音。P1.4端输出高电平时,晶体管导通,压电蜂鸣器两端获得约+5 V电压而鸣叫;当P1.4端输出低电平时,晶体管截止,蜂鸣器停止发音。三极管驱动的蜂鸣器报警电路如图5所示。

图5 三极管驱动的蜂鸣器报警电路

1.8 操作指示灯控制电路

指示灯的作用是判别效验提示密码输入的正误。设计时使用发光二极管作为指示灯,当密码输入错误时,单片机P3.0端口通过三极管放大发出信号控制红灯亮,提示再次输入密码;当密码输入正确时,单片机P3.1端口通过三极管放大发出信号控制绿灯亮起,同时开锁。

2 程序设计

2.1 模块介绍

电子密码锁软件采用51系列单片机,使用汇编语言编程实现密码识别、智能报警等程序设计。各功能的实现采用模块化程序设计,主要程序是对中断向量和各子程序进行初始化、设置管理与调用。

2.2 键盘扫描子程序

键盘采用编程扫描的工作方式,主要是判别键盘有无键闭合,防止键盘的键发生机械抖动或者检验键号有无闭合的情况,这样中央处理器(Central Processing Unit,CPU)就只处理1次按键的闭合。

2.3 动态显示子程序

在89C51内部随机存取存储器(Random Access Memory,RAM)中设置了6个40~45 h的显示缓冲单元,显示器分别存储显示6位数据。其中总有1位高电平在8155H的PA口,经过74LS04反相后,即显示器的6个显示位元中只有一位共阴极为低电平,反之则为其他电平。8155H的PB口输出对应位元的显示数据段码,使某一位元显示1个字码,其他位元则不显示。依次改变PA口输出为高位,PB口输出对应的段码,显示器的6位将显示数据所确定的字符动态地在缓冲区显示。

2.4 掉电存储密码子程序

为了防止系统掉电时数据存储器RAM中的数据丢失,比较密码时需要读串行存储程序,再将芯片中储存的数据读取到RAM中,然后和输入的密码相比较。而修改密码时,需要把新输入的密码存储在AT24C02芯片中。

3 结 论

根据功能要求和系统设计共包含了硬件电路与软件程序2个部分,其中采纳的AT24C02芯片用于存储和密码的掉电保护策略,软件成分较高,而在实际设计中也可以采用诸如掉电保护电路等硬件电路。该电子密码锁的系统电路设计使用简便、消耗小、运行平稳,同时具备较好的网络扩展能力及安全防范技术措施。