基于FPGA的NAND FLASH坏块表的设计与实现

2022-02-02曾锋徐忠锦

曾锋 徐忠锦

摘要:在现代电子设备中,越来越多的产品使用NAND FLASH芯片来进行大容量的数据存储,而且使用 FPGA作为核心处理芯片与NAND FLASH直接交联。根据NAND FLASH的特点,需要识别NAND FLASH芯片的坏块并进行管理。FPGA对坏块的管理不能按照软件的坏块管理方式进行。本文提出了一种基于FPGA的 NAND FLASH芯片坏块表的设计方法,利用FPGA中RAM模块,设计了状态机电路,灵活地实现坏块表的建立、储存和管理,并且对该设计进行测试验证。

关键词: NAND FLASH;FPGA;坏块;坏块检测

0引言

随着技术的发展,越来越多的电子设备的数据采用 NAND FLASH 芯片存储产生的大量数据。在传统的电路设计中,常用 ARM、DSP 等处理器来用于 NAND FLASH 的接口。但是随着实时性要求的提高,越来越多的设备中采用了 FPGA 来对 NAND FLASH 进行坏块管理,释放处理器任务资源。

由于 NAND FLASH 的特点,NAND FLASH 不可避免地会有坏块产生,使用 NAND FLASH 时,需要对坏块进行管理,建立坏坏表(以下简称“BBT”)。一般处理管理 BBT 的方法,是采用建立数组的方式,将检测到的坏块编号记录在数组中,在操作 NAND FLASH 时,对将要操作的块的编号与 BBT 的数据进行对比,如果是坏块,则跳过该块,不使用。但是这是建立数组的方法并不适用于 FPGA 的设计操作,本文根据 FPGA 的特点,利用 FPGA 的 Block RAM 资源,提出了一种坏块检测、存儲的方法。

1电路说明

1.1 NAND Flash芯片说明

NAND Flash芯片使用型号是三星公司的K9K8G08U0A,

单片容量为1 G×8 Bit。该芯片总共有8192块,每块中含有64页,每页共2112个字节(前2048个为主存储空间,后64个为扩展存储空间)。芯片的读写操作均以页为单位进行。芯片容量结构如图1所示。

其中,NAND Flash 芯片分为列地址( Column Address )和行地址( Row Address ),列地址用于每页中的字节寻址,行地址用于芯片的块、页的寻址,其中行地址的 A18~A30为芯片的块地址。

1.2 FPGA电路说明

FPGA 使用型号为 Xilinx (现 AMD )公司Virtex II 系列的 XC2V1000,芯片内部有5120个 Slice、40个乘法器、720 kbit 的 RAM模块资源,8个 DCM 时钟管理模块。其主要参数如图2所示。

2坏块表设计

2.1坏块表检测机理

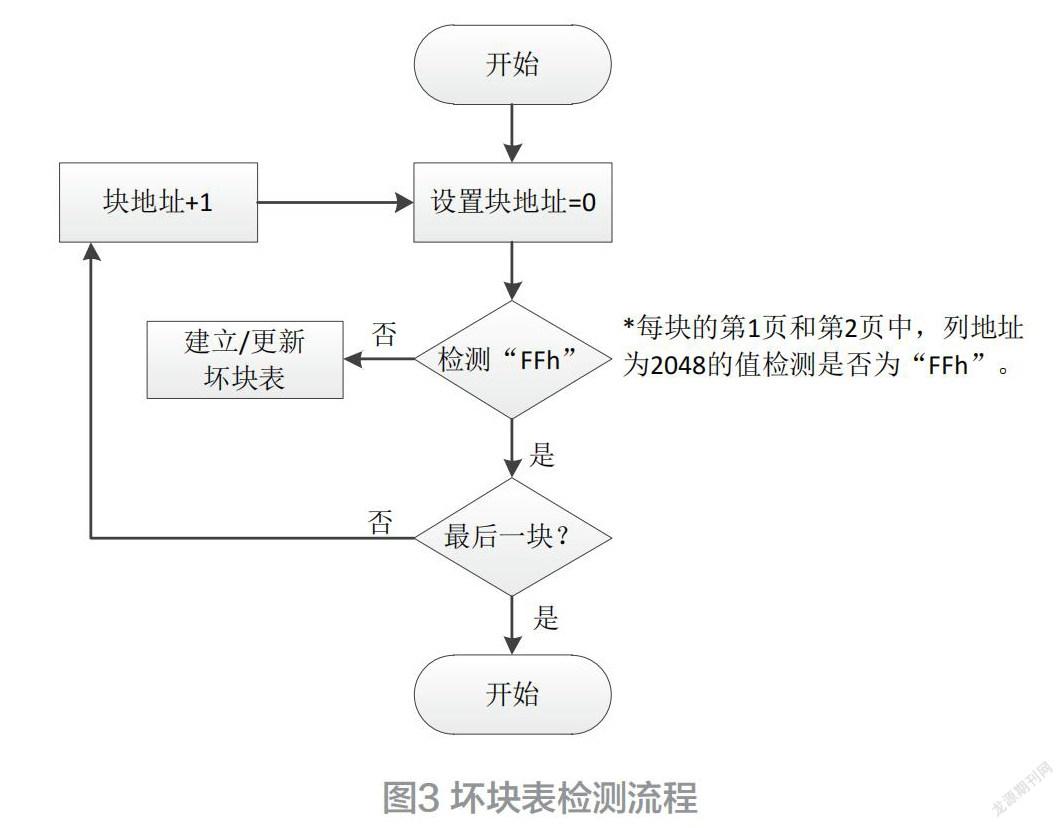

根据 NAND FLASH 芯片的检测原理,芯片出厂后的坏块检测需要检测芯片每个部分的页1和页2中列地址为2048的存储的数据值。若值为0xFF ,则该部分为好块;若值不为0xFF ,则该部分为坏块。NAND FLASH 坏块检测流程如图3所示。

2.2坏块表的设计思路

根据 FPGA 的应用特点,本次 NAND Flash 的坏块表采用对所有块建立坏块信息的方式,建立一个完整的块状态信息表,即每一个块用1个 Bit 表征其是否是好块还是坏块,定义为:0代表该块是良好的,1代表该块是故障的。本设计中,NAND Flash 有8192个块,用8192个 Bit 代表每个块的状态信息,正好用一个1024×8 bit 的 RAM对所有的坏块表数据位进行存储,坏块表存储示意图见图4。

2.3坏块表的存储

在本设计中,NAND FLASH 的坏块表储存在 NAND FLASH 的第1块的第1页处。第1块只用于坏块表的存储,不再用于存储其他数据,坏块表在第1块中的位置见图5。

2.4坏块表的建立流程

NAND FLASH 在使用时,初次上电后,写入数据之前需要对芯片的块的好坏进行扫描,从而得到坏块表。在本型号中,NAND FLASH 的出厂坏块信息需要查询每个块的第1个页和第2个页中的列地址为2048的空间上数据是否都为“0xFF”,数据为“0xFF”,则当前块为好块,否则当前块为坏块。

坏块表的建立的状态机流程如图6所示:上电后,状态机从状态1跳转至状态2,读取第一块中的数据,判断是否为数据头0xAA、0x55、0xAA、0x55、0xAA、0x55、0xAA、0x55。如果数据头相符,则状态跳转至11,直接读取坏块表到 RAM ,建立起坏块表信息。如果读到的数据头与上述的数据头不相符,则意味 NAND FLASH 未存在坏块表,需要建立坏块表。状态机状态依次跳转至状态4、状态5、状态6,即状态机对当前块的中的第1页和第2页的中列地址为2048的空间进行访问,根据读值判别当前块是否为坏块,如果是坏块将对应的寄存器位置1。当扫描完8个块,状态机跳转至状态7,则将8个块的坏块信息写入 RAM ;当未扫描满8个块,状态机跳转至状态8,块地址加1,对下一个块进行检测。当所有的8092个块都被检测后,则状态机跳转至状态10,将数据头以及 RAM 数据全部写入 NAND FLASH 的第0块,至此,初始坏块表建立完成。

坏块表建立完成后,坏块信息存在 RAM 中,在正常存取操作时,就可以直接读取 RAM 模块,获取坏块信息。

当电路下电,再次上电后,状态机就可以从块0中读取到数据头,跳过初次坏块表的建立过程,状态机从第1块中继续读取到坏块表,加载到 RAM 中,完成后交其他模块进行后续的操作。

3验证情况

为验证是否正确的建立和存储坏块表,需要将坏块表的处理模块嵌入 FPGA 的中整个 NAND FLASH 的接口控制器中,验证的电路如图7所示。坏块表处理模块与1个1024×8 Bit 的 RAM 连接,该 RAM 用于存储坏块表。NAND FLASH 接口模块根据 NAND FALSH 芯片的读写接口时序设计,包含基本的 Read 模块,Write 模块和擦除模块。 NAND FLASH 接口模块受坏块表处理模块的控制。正常工作模块在坏块表处理模块工作完成之后开始工作,通过 UART 接收上位机的命令,控制 NAND FLASH 接口模块与 NAND FLASH 交联;同时,正常工作模块也通过 UART 上报数据和信息给上位机。

验证时,通过上位机发送读取命令,正常工作模块控制 NAND FLASH 接口模块将 NAND FLASH 块0中的内容读取出来,从而判断是否正确地建立了坏块表,见图8。

通过读取内容发现,新板卡中的 NAND FLASH 成功地建立了坏块表,本测试电路中 NAND FLASH 芯片有 1 个坏块,为第 1 761 块。

4 结束语

通过验证证明,本文设计的基于 FPGA 的坏块表设计方式能够正确地实现坏块表建立和存储,坏块表能够方便地被 FPGA 使用,坏块表能完整地表征整个 NANDFLASH 芯片的块的状态,RAM 结构能很灵活方便地在FPGA 中进行调用,满足对 FPGA 对 NAND FLASH 芯片的控制需要。

参考文献:

[1] 舒文丽,吴云峰.基于NAND FLASH的海量存储器的设计[J].电子器件,2012,2(35):44-46.

[2] 赵亚慧.基于NAND Flash的高速大容量存储系统的设计[J].电光与控制,2016,5(23):37-40.

[3] 乔亚飞,,李华旺.基于FPGA的星载NAND FLASH控制器的设计[J].电子设计工程 2018,7(26):29-32.

[4] 周浩,王浩全.基于FPGA和NAND FLASH的便携式信号采集系统设计[J].测控技术与仪器仪表,2018,44(9):82-86.

[5] 张雯,崔建杰.一种多通道NAND FLASH阵列的坏块管理方案[J].电子器件,2014,10(37):33-36.

[6] 乔立岩,张鹏.一种新型NAND FLASH 坏块管理算法的研究与实现[J].电子测量技术, 2015,11(38):19-21.