一种实时频谱仪中帧检波器的FPGA 实现

2021-12-22何鹏

郭 静,何鹏

(中国电子科技集团公司第四十一研究所,山东 青岛 266555)

0 引言

随着无线电技术的快速发展,信号越来越呈现出复杂性、瞬变性、传输快、高带宽等特点,对射频信号的测试和检测要求越来越高,信号测量分析技术的发展也面临着很大的挑战和机遇[1-3]。传统的频谱仪由于不能进行实时数据处理,容易导致突发瞬变信号的遗漏,已经无法满足复杂信号对频谱分析和测试的需求。为满足复杂电磁环境下的信号测试工作需要,实时频谱分析仪应运而生并得到了快速发展[4-5]。

实时频谱分析仪具有无缝数据处理能力[6-7],实时处理FFT 模块完成时域数据到频域数据的转换,得到每秒数十万甚至上百万数量级的频谱帧,如此庞大的数据量不仅难以进行数据传输,而且更无法实时显示[8],因此需要实时检波技术来解决传输和刷新的瓶颈。传统实时频谱仪中的帧检波器通常采用RAM 资源进行实现[9-10],在检波过程中需要对RAM 进行读、写地址的控制,控制方法较为繁琐且占用逻辑资源。本文提出了一种基于FPGA FIFO 资源实现的实时检波器,不需要控制读写地址,只需控制新来的频谱数据与FIFO 中存储的数据一一比较或累加后重新写入FIFO,实现方式简单且占用逻辑资源较少。

实时频谱仪具有可变分析带宽功能,可变分析带宽滤波器通带外的频谱数据不需要进行显示,在检波运算前剔除分析带宽外的数据,可以减小后续信号处理和数据传输的压力,因此本文在检波运算前增加了是否为分析带宽内显示点的判断。

1 实时检波器原理

实时频谱仪数据处理组成框图如图1 所示。中频输入信号通过ADC 采样,采样后的数据经过下变频与可变分析带宽数字滤波后无缝进行实时FFT 频谱计算[11-12],实时检波器将多帧FFT 频谱数据根据不同检波方式保留不同信号特征,压缩成1 帧频谱数据传输至上位机进行刷新显示。本系统中ADC 采样率为204.8 MHz,最大分析带宽下数字下变频滤波经过2 倍抽取形成102.4 MHz速率的IQ 数据,若进行1 024 点数的FFT 运算,每秒可形成10 万帧频谱数据。为了适应人眼可识别的数据刷新频率,需要进行实时帧检波处理,即每4 000 帧频谱检波输出1 帧频谱,形成每秒25 帧的刷新频率[13]。

图1 实时频谱仪数据处理框图

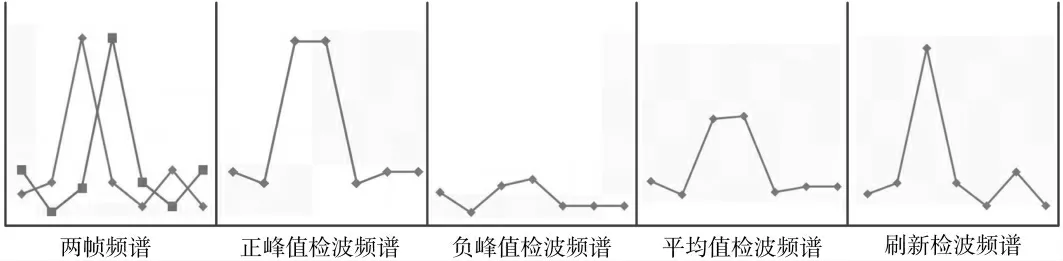

实时频谱分析仪参考传统频谱仪中的视频检波算法,同时考虑到数据处理的实时性,引入了正峰值、负峰值、平均值和实时刷新四种检波方式[14-15]。图2为对两帧频谱经过不同检波方式输出的频谱图,正峰值检波画出了所有频点的最大值包络,负峰值检波选取每个频点最小值的信号进行显示,平均值检波对每个频点的值求平均值,实时刷新检波则仅选择输出一帧频谱数据。不同的检波方式有利于观察不同特征的信号,正峰值检波有利于保留突发信号的信息,负峰值检波有利于消除突发信号的影响,平均值检波有利于提高小信号的测量能力,实时刷新检波有利于观察检波前原始信号的频谱。

图2 不同检波方式输出的频谱图

2 实时检波器设计与实现

2.1 分析带宽内显示点计算

实时频谱仪具有可变分析带宽功能,显示的频谱数据为分析带宽内的数据,因此原始的频谱数据需要根据用户设定的频点间步长、分析带宽和FFT 点数来进行截断,剔除分析带宽外的数据。显示点数计算公式如式(1)所示:

式中,ShowNum为显示点数;BW为分析带宽,Hz;Step为频点间步长,Hz。

以60 MHz 分析带宽、100K 步长为例,该参数设置下上位机软件自动关联的FFT 点数为1 024 点,通过式(1)计算出显示点数为601 点,需要选取1 024 点频谱数据中间的601 点数据进行后续的处理与显示,前后两端共423 个点应该被剔除。在本文中对输入的每一帧频谱数据进行点数计数编号,通过该点对应计数器的值即可判断该点是否位于显示点的位置,从而在该频谱帧到达检波器时判断每一个频点为显示点还是截断点,若为显示点则参与检波运算,若为截断点则舍去跳转到下一流程。

2.2 实时检波器的实现

本文使用Xilinx Kintex UltraScale 系列的FPGA 进行数字中频信号处理,通过FIFO 对检波过程数据进行暂存,设置FIFO 读数模式为First Word Fall Through,以便在新频谱数据到来时及时与FIFO 的输出数据做比较,宽度为平均值检波模式下所需累加器产生最大数据的宽度,深度为可容纳最大显示点的数据量。

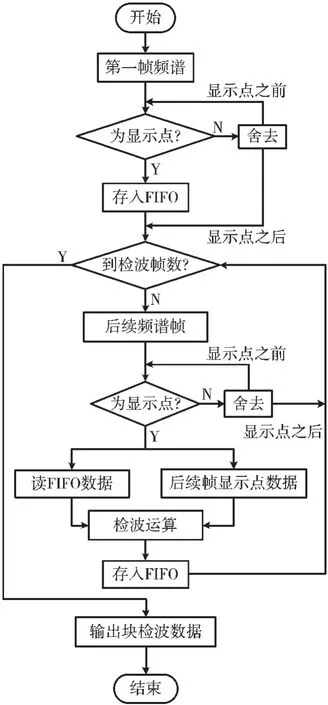

图3 所示为基于FIFO 结构实现的检波器逻辑控制框图,上位机软件设置检波帧数、检波类型和显示点数后,经过FFT 变换后的频谱数据输入至实时帧检波器进行检波,不同时间内无缝捕获的许多相邻帧组成块[6],具体块内检波实现流程如图4 所示。

图3 基于FIFO 结构实现的检波器逻辑控制

图4 块内检波流程图

(1)频谱数据编号:对每一帧到来的频谱数据进行编号,对于长度为NFFT 的频谱数据,编号应为1~NFFT。

(2)存储数据:第一帧频谱数据的显示点暂存至FIFO 中。

(3)读取数据并回写数据:后续帧频谱数据的显示点到达的同时读取FIFO 数据,新的频谱数据依次与FIFO输出的频谱数据进行比较或累加,根据不同的检波方式将得到的数据写入至FIFO(正峰值检波使用比较器写入较大的值,负峰值检波使用比较器写入较小的值,平均值检波使用累加器写入累加值,实时刷新检波直接写入输入的频谱数据),等待下一帧频谱数据的显示点到来时再进行比较或累加。

(4)输出数据:处理的频谱数据帧数达到软件设置的检波帧数后输出检波频谱数据,其中均值检波需要将FIFO 输出的累加值除以检波帧数进行平均运算,其他检波方式则直接输出FIFO 的存储数据。

(5)重置参数:清零检波帧数计数器,准备进行下一个块的检波。

由于本系统中FPGA 的处理时钟为204.8 MHz,FFT频谱数据速率为102.4 MHz,在输出检波数据帧的过程中不会被新的频谱数据所覆盖,因此只需要单路检波器即可满足要求。若存在输入频谱数据覆盖输出频谱数据的风险,可将该结构扩展为采用两个相同的FIFO 进行乒乓操作。

3 实验测试

3.1 仿真测试

使用Vivado 自带仿真器对实时检波器程序进行仿真,以正峰值检波为例。设置FFT 点数为1 024 点,显示点数为601 点,块检波帧数为2 帧,检波模式选择正峰值检波。图5为检波器仿真波形图,data_in为输入1 024点数的频谱,第一帧信号频率为143.6 MHz,第二帧信号频率为163.6 MHz,data_out为经过检波输出后的601 个点的显示频谱,可以看出输出频谱同时保留了143.6 MHz和163.6 MHz 两个信号,实现了正峰值检波与分析带宽外数据的截断。

图5 检波器仿真输出正峰值检波频谱

3.2 实际测试

连接信号源输出端和实时频谱仪输入端,设置信号源输出频率为6 GHz,实时频谱仪分析带宽为60 MHz,步长为25 kHz,块检波帧数为4 000 帧,分别设置实时频谱仪的检波方式为正峰值、负峰值、平均值和实时刷新,得到不同检波模式的输出频谱图如图6 所示。由实验测试结果可以得出,该实时检波器可以满足实时频谱仪的检波需求。

图6 不同检波模式下输出频谱

4 结论

本文利用FPGA 的FIFO 资源设计了一种可应用于实时频谱仪的帧检波器,实验证明该检波器可实现正峰值、负峰值、平均值和实时刷新四种检波功能,能够根据需要灵活设置检波帧数与检波模式,满足实时频谱仪的检波需求。在参与检波运算前对分析带宽外数据进行剔除,减轻了后续数据的处理压力。基于FIFO 资源实现的检波器结构简单,占用逻辑资源较少,可在实时频谱仪中广泛推广使用。