一种新型浮地记忆元件建模方法及实现*

2021-12-16郑辞晏庄楚源李亚练明坚梁燕于东升

郑辞晏 庄楚源 李亚 练明坚 梁燕 于东升

1) (广东技术师范大学自动化学院,广州 510665)

2) (广东技术师范大学电子与信息学院,广州 510665)

3) (杭州电子科技大学电子与信息学院,杭州 310018)

4) (中国矿业大学电气与动力工程学院,徐州 221116)

忆阻器、忆容器和忆感器是具有记忆特性的非线性元件,隶属于记忆元件系统.目前,由于现有可购忆阻器芯片尚存在许多不足,且忆容器和忆感器的硬件实物研究仍处于实验室验证阶段,因此,研究者们获取此类记忆元件硬件仍有难度.为了解决这个问题,建立有效的记忆元件等效电路模型,以促进对记忆元件及其系统的特性和应用研究.本文根据忆阻器、忆容器和忆感器的本构关系,提出一种新型浮地记忆元件建模方法,即采用搭建通用模拟器的方式,在保证电路拓扑结构不变的情况下,通过改变接入通用模拟器的无源电路元件分别实现浮地忆阻器、忆容器和忆感器模型.相比于其他能实现3 种浮地记忆元件模型的研究,本文所搭建的记忆元件模型结构简单,工作频率更高,易于电路实现.结合理论分析、PSPICE 仿真及硬件电路实验结果的一致性,验证基于该通用模拟器搭建记忆元件模型的可行性和有效性.

1 引言

忆阻器是一种新型记忆元件,其概念由蔡少棠[1]于1971 年提出,并在2008 年由惠普(HP)实验室成功制备为纳米级固态元件[2].此后蔡少棠团队[3]将记忆系统的概念拓展到容性和感性元件中,形成了一种基于忆阻器、忆容器和忆感器的记忆元件系统.现有研究表明忆阻器、忆容器和忆感器凭借其独特的记忆特性以及非线性特性,在混沌电路[4,5]、信号处理[6,7]、非易失性存储器[8]、存算一体芯片[9,10]和人工神经网络[11,12]等多个领域具有广阔的应用前景.最近研究表明存在基于磁电耦合效应实现的第4 种记忆元件—忆耦器[13,14],其概念的提出拓宽了记忆元件的定义和概念,极大地提升了记忆元件的应用潜力.

目前,市面仅有忆阻器元件可购,忆容器[15]、忆感器[16]和忆耦器[13,14]的物理实现仍停留于实验室验证阶段,尚未市场化.然而,Knowm 忆阻器芯片作为全球目前唯一一款可购记忆元件,在使用过程中存在以下问题:该器件两端存在较大的寄生电容,可能导致出现忆阻器极性翻转及记忆衰退等现象;其阻变存储技术所具有的随机性导致忆阻器可编程忆阻值参数可控性和稳定性不足;其直流和交流响应不稳定等[17,18].为此,根据记忆元件本构关系和电学特性,搭建记忆元件等效电路模型以用于其特性研究和应用开发[19,20]成为近年来的研究热点.目前,已有对记忆元件中的忆阻器、忆容器和忆感器的等效电路模型搭建研究,但尚未出现关于忆耦器的等效电路模型搭建相关研究.例如,研究者根据记忆元件的本构关系搭建单个忆阻器[21,22]、忆容器[23]或忆感器模型[24].此外,有学者根据记忆元件本构关系之间的联系,利用现有的忆阻器模型和外围转化电路来构造忆容器和忆感器模型[25,26],然而,由于上述忆容器和忆感器模型是基于忆阻器转化得到,使所转化的忆容器和忆感器模型依赖于原有忆阻器特性,且结构复杂、难以简化.因此,为了搭建模型更简单的记忆元件,Fouda 等[27]提出了不含忆阻器的忆容器模型.梁燕等[28]采用相似设计思路,提出了不含忆阻器的忆感器模型.近年来,研究者在以往单个记忆元件模型设计的基础上,提出通用的记忆元件模型.李志军等[29]提出了一个由基本电路元件和可购芯片构成的通用记忆元件模拟器,在保证电路拓扑结构不变的情况下,通过接入不同性质元件,分别模拟忆阻器、忆容器和忆感器的电路行为.然而,其搭建的记忆元件需确保模型中的场效应管工作于线性区域方能呈现出记忆特性,限制了模型的工作电压范围,且其工作频率较低(0.8 kHz 左右).Wang 等[30]基于通用模拟器实现3 种浮地型记忆元件模型,然而,其呈现磁滞特性曲线的最高工作频率约为5 kHz.Zheng 等[31]和Yu 等[32]利用变容二极管设计通用模拟器,并基于通用模拟器搭建了记忆元件模型,但所搭建记忆元件输入输出特性通过近似模型获得.Sharma 等[33]利用硬件实验实现了基于通用模拟器的记忆元件,然而其设计的模型的输入和输出电流不相等,无法等效模拟浮地型二端口记忆元器件,存在“伪浮地”的不足.

基于以上分析,本文采用基本无源电路元件及可购芯片设计一种通用模拟器,在保持其电路拓扑结构不变的情况下,通过改变接入通用模拟器元件的性质分别搭建浮地型忆阻器、忆容器、忆感器模型,针对现有的能实现3 种浮地的通用记忆元件模型存在的结构复杂、工作频率低、建模不够精准、“伪浮地”等问题对通用记忆元件模型做出改进,并通过理论分析、电路仿真和硬件电路实验验证所搭建的基于通用模拟器的记忆元件模型的可行性.

2 基于通用模拟器的记忆元件模型设计

记忆元件具有存储过往电路信息的特性,由其本构关系数学模型中的状态变量反映.以忆阻器为例,其本构关系为q-ϕ间的非线性关系,可以由分段线性、二次非线性、三次非线性等非线性数学模型描述[34-36].忆容器和忆感器模型的本构关系分别为σ-ϕ和q-ρ之间的非线性关系,也可由二次非线性数学模型描述[37,38].上述本构关系中,q代表电荷量,ϕ代表磁通量,即电压对时间的积分,σ代表q对时间的积分,ρ代表ϕ对时间的积分.因此,本文采用二次非线性数学模型分别描述忆阻器、忆容器和忆感器本构关系.

忆阻器的q-ϕ本构关系以及忆导值Wm(忆阻值倒数)可定义为

其中,α1代表忆导值Wm的变化率,β1代 表Wm的初始值.

忆容器的σ-ϕ本构关系以及忆容值Cm可定义为

其中,α2代表忆容值Cm的变化率,β2代表Cm的初始值.

忆感器的q-ρ本构关系以及忆感值倒数值可定义为

其中,α3代表忆感值倒数值的变化率,β3代表的初始值.

2.1 通用模拟器及基于通用模拟器的记忆元件电路实现

本文根据忆阻器、忆容器和忆感器本构关系,提出一种可用于构造记忆元件模型的通用模拟器等效电路,如图1所示,其电路结构包含4 个电流反馈放大器AD844 (标为U1,U2,U3和U4)、1 个乘法器AD633(U5)、2 个阻抗元件(标为Z1,Z2)、电阻R1、电容C1以及直流电压源Vs,其中端口A和B 作为通用模拟器的外接二端口,用于与外围电路进行连接.

图1 通用模拟器设计Fig.1.Design of a universal emulator for building models of mem-elements.

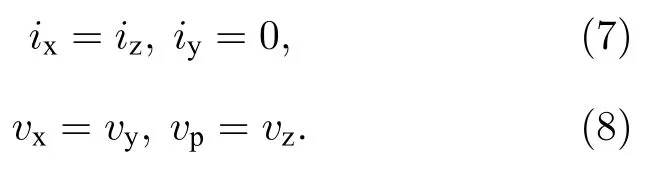

AD844 为电流反馈放大器,在通用模拟器电路中起电流传输器和电压跟随器的作用.根据其端口特性:

可得通用模拟器中A,B 端的输入电流iAB与流经阻抗元件Z2电流i4在复频域上的表达式:

电容C1在电路中起电流积分器作用,设积分电容C1的初始电压为0,根据(10)式可求得C1两端电压表达式,且由(8)式,可得U5 的 x1端输入电压vx1在复频域上的表达式:

根据AD633 芯片端口输出特性,可得其输出端w 的电压vw在复频域上的表达式:

其中Vs为常量直流电压.

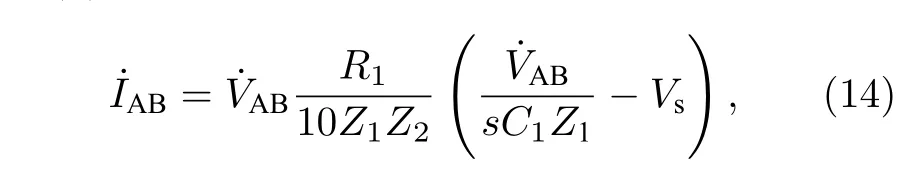

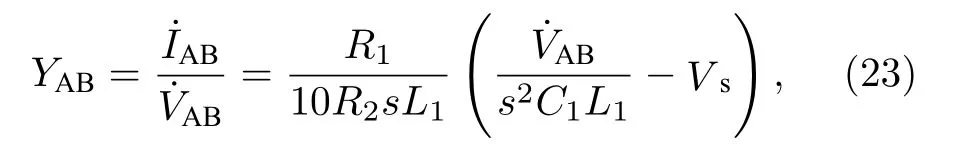

将(11)式和(12)式代入(13)式,并将(13)式代入(9)式可得通用模拟器二端口输出方程:

即通用模拟器A,B 端等效导纳可表示为

1)当阻抗元件Z1和Z2分别为电阻R2和R3时,此时模拟器模拟为磁通控制忆阻器模型,其忆导值在时域上可描述为

根据(2)式,(16)式可等效表示为

其中,α1和β1可表示为

2)当阻抗元件Z1和Z2分别为电阻R2、电容C2时,有:

此时模拟器模拟为磁通控制忆容器模型,其时域表达式如下:

根据(4)式,可得磁通控制忆容器的忆容值Cm在数学上的定义:

其中,α2和β2可表示为

3)当阻抗元件Z1和Z2分别为电感L1、电阻R2时,有:

此时模拟器模拟为磁通控制忆感器模型,其时域表达式如下:

根据(6)式,可得磁通忆感器的忆感值倒数值在数学上的定义:

其中,α3和β3可表示为

2.2 记忆元件模型特征对比

本文基于通用模拟器电路分别搭建了忆阻器、忆容器和忆感器模型,其各特征量对比如表1所示.

表1 基于通用模拟器的记忆元件模型对应特征比较Table 1.Comparison of characteristics of different kinds of mem-element models based on the proposed universal emulator.

3 基于通用模拟器的记忆元件模型仿真分析

在本节中,为了初步验证本文所提基于通用模拟器的记忆元件模型的正确性,采用PSPICE 软件进行仿真分析,并提供相对应的仿真分析结果.其中,采用正弦信号vAB=Uosin(2πft)=Uosin(ωt) (V)作为电路模型的二端口激励电压,芯片直流供电电压为±15 V.

3.1 忆阻器模型仿真分析

基于图1所示通用模拟器设计PSPICE 电路仿真模型,分别选取阻抗元件Z1,Z2为电阻R2,R3.根据正弦激励电压表达式vAB=Uosin(2πft)=Uosin(ωt)(V),由于磁通ϕAB是电压vAB对时间的积分,结合(16)式,可以得到在正弦波电压激励下,浮地忆阻器的磁通ϕAB和等效忆导值Wm(ϕAB) 为

故根据阻性元件的电压电流关系,流经磁通控制忆阻器的电流iAB可表示为

根据以上的理论分析,在仿真过程中,电路参数设置为C1=0.1 nF,R1=45 kΩ,R2=16 kΩ,R3=55 kΩ,直流电压Vs=-2.5 V.根据(18)式,可计算得到α1=3.20 S/Wb,β1=1.28×10-5S.采用U0=1 V,激励频率f分别为f=80 kHz,100 kHz 以及130 kHz 的正弦波电压vAB驱动忆阻器模型,得到如图2所示忆阻器PSPICE 仿真结果图.根据忆阻器模型中Z1是元件R2和公式(12),得到忆阻器两端的磁通ϕAB正比于电容C1两端电压,因此可以用vC1等效表示ϕAB.

图2 忆阻器模型的PSPICE 仿真结果 (a) 不同频率激励下的忆阻器 vAB-iAB特性曲线;(b) 不同频率激励下的忆阻器忆导值 Wm 与 vAB的关系图;(c) 在Uo=1 V,f=100 kHz下,vAB,iAB,ϕAB(用 vC1表示)和Wm的时域波形图Fig.2.Measured simulation results of the proposed memristor emulator:(a) Pinched hysteresis loops under different working frequencies;(b) variation curves of the memductance Wm plotted against the terminal voltage vAB;(c) timedomain wave-forms of vAB,iAB,ϕAB(represented by vC1)and the memductance Wm when Uo=1 V,f=100 kHz.

比较图2(a)中频率为80 kHz,100 kHz 以及130 kHz 时的电压vAB和电流iAB轨迹图,可以得到忆阻器的重要特征:在vAB-iAB平面内,其斜率等效为忆导值Wm且等效忆导值Wm保持形如斜“8”字形的磁滞环,在正弦激励电压幅值保持不变时,随着激励频率的增大,磁滞环向内收缩.图2(b)表明,在电压取值不为极值的情况下,等效忆导值Wm不唯一.以f=80 kHz条件下的vAB-Wm特性曲线图为例,沿着箭头方向,忆导值Wm幅值在vAB正区间增大,在vAB负区间减小.图2(c)表明在频率为100 kHz 情况下,与(29)式分析一致,电流iAB在输出电压vAB为正弦激励电压下,呈现出非标准的正弦波形,并且比较电流iAB与电压vAB波形图相位可知该记忆元件模型具有非线性特性且呈阻性,即说明该器件为忆阻器.图2表明仿真结果与理论分析一致,证明了本文基于通用模拟器的忆阻器等效电路模型的正确性.

3.2 忆容器模型仿真分析

当阻抗元件Z1和Z2分别为电阻R2和电容C2时,此时模拟器模拟为磁通控制忆容器模型,同理于忆阻器,忆容器的重要特点是其容值的受控性,当对其施加正弦电压激励时,忆容器端电压与流经忆容器电荷的相图呈现磁滞环形.对于正弦激励电压vAB=Uosin(2πft)=Uosin(ωt) (V),同理于(27)与(28)式,由(20)式可得忆容器等效忆容值Cm(ϕAB)的表达式:

分析(30)式可得:忆容器磁通ϕAB的幅值正比于Uo/ω,在相同的正弦波激励电压幅值下,随着激励电压频率的增大,磁通ϕAB的幅值逐渐减小并趋近于0,使得其等效忆容值趋近于固定值β2,从而导致端电压和流经忆容器的电荷的李萨如相轨迹vAB-qAB呈现向内收缩现象.

结合以上理论分析,所搭建忆容器PSPICE模型设置以下电路参数:电容C1=0.25 nF,C2=0.1 nF、电阻R1=3 kΩ,R2=11 kΩ、直流电压Vs=-0.5 V,计算(22)式可得α2=9.92×10-7F/Wb,β2=1.36×10-12F.根据忆容器模型中Z1是元件R1和公式(12),得到忆容器两端的磁通ϕAB正比于电容C1两端电压,因此可以用等效表示ϕAB;根据Z2是元件C2和公式(9),得到流经忆容器的电荷qAB正比于电容C2两端电压负值,因此可以用等效表示qAB.采用Uo=1 V,频率f分别取80 kHz,85 kHz 以及90 kHz 的正弦波电压vAB驱动忆容器模型,得到如图3所示忆容器模型的PSPICE 仿真结果.

图3 忆容器模型的PSPICE 仿真结果 (a) 不同频率激励下的忆容器 vAB-qAB(用 vAB-(-vC2) 表示)特性曲线;(b)不同频率激励下的忆容器忆容值 Cm 与 vAB的关系图;(c) 在Uo=1 V,f=80 kHz 下,vAB和qAB(用 -vC2表示)、ϕAB(用 表示)和Cm的时域波形图Fig.3.Measured simulation results of the proposed memcapacitor emulator:(a) Pinched hysteresis loops under different working frequencies;(b) variation curves of the memcapacitance Cm plotted against the terminal voltage vAB;(c) timedomain wave-forms of vAB,qAB(represented by -),ϕAB(represented by) and the memcapacitance Cmwhen Uo=1 V,f=80 kHz.

图3(a)表明,vAB-qAB相图由vAB-(-vC2)等效表示,在频率为80 kHz,85 kHz和90 kHz 的同幅值正弦激励电压下,其端电压vAB和瞬时电荷qAB的相图呈现斜“8”字形磁滞环,并且随着频率增大,磁滞环围成的瓣面积变小.图3(a)表明PSPICE仿真结果同理论分析一致,证明了本文设计的忆容器等效电路模型的正确性.

图3(b)表明相同电压下的等效忆容值Cm的取值不唯一,并且随着激励电压频率的升高,Cm的最大值和最小值区间上下限减小.图3(c)所示为在激励频率为80 kHz 下,忆容器各变量端电压vAB、等效于qAB的、等效于磁通ϕAB的以及忆容值Cm的时域图,明显看出,vAB和的波形存在相位差,这也是vAB-qAB相图呈现磁滞特性的原因,而vAB和的同相位表明该模拟器实现的是容性忆容器元件模型.

3.3 忆感器仿真分析

当阻抗元件Z1和Z2分别为电感L1、电阻R2时,此时模拟器模拟为磁通控制忆感器模型,采用以下电路参数:电容C1=0.02 nF、电阻R1=3 kΩ、R2=8 kΩ、电感L1=0.05 H、直流电压Vs=-2.5 V.根据(26)式可计算得α3=7.50×1011(H·Wb)—1,β3=1.875 H-1.根据忆感器模型中Z1是元件L1和公式(10),得到忆感器两端的磁通ϕAB正比于流过忆感器的电流i1,因此可以用i1等效表示ϕAB;根据模型中Z1是元件L1和公式(12),得到忆感器两端磁通的积分ρAB正比于流过C1两端的电压,因此可以用等效表示ρAB.

对于正弦激励电压vAB=Uosin(ωt) (V),可以得到正弦波电压激励情况下,忆感器的磁通积分ρAB(假设积分初始值为0)和等效忆感值倒数为

由感性元件的磁通、电流关系,可以得到流经磁通控制忆感器的电流为

通过对(31)式,(33)式分析可知:在相同幅值的激励电压下,随着频率的增大,磁通与电流幅值均减少,在同一时刻t,电流减小的幅度大于磁通减小的幅度.

图4(a)所示为不同频率下忆感器磁通和流经忆感器的电流的李萨如相轨迹ϕAB-iAB,比较频率为95,100 以及105 kHz 的相轨迹图,可以明显看出,忆感器磁通和流经忆感器的电流的相图ϕAB-iAB保持斜“8”字形的磁滞环,且随着激励频率增大,电流和磁通幅值均减小,磁滞环向内收缩.

图4 忆感器模型的PSPICE 仿真结果 (a) 不同频率激励下的忆感器 ϕAB-iAB (用 i1-iAB表示)特性曲线;(b)不同频率激励下忆感器的忆感值倒数 与 ϕAB(用 i1表示)的关系图;(c) 当Uo=1 V,f=100 kHz 时,iAB,ρAB(用表示)、ϕAB和的时域波形图Fig.4.Measured simulation results of the proposed meminductor emulator:(a) Pinched hysteresis loops under different working frequencies;(b) variation curves of the inverse meminductance plotted against the fluxϕAB(represented by i1);(c) time-domain wave-forms of iAB,ρAB(represented by ),ϕABand the inverse meminductance when Uo=1 V,f=100 kHz.

图4(b)为Uo=1 V,激励频率为95,100和105 kHz 下忆感值的倒数与磁通ϕAB的相图变化曲线.等同于忆阻器的忆导值和忆容器的忆容值,忆感器的忆感值倒数在交变激励电压的取值为非最值情况下存在两个可能值,并且沿着频率为95 kHz 的ϕAB相图曲线的箭头方向,可以发现在正磁通范围内增大,在负磁通范围内减少.

图4(c)绘制了在激励频率为100 kHz 下各变量iAB,ρAB(用vC1表示)、ϕAB(用i1表示)和的时域波形图,由(33)式可知iAB的波形呈现非标准式正弦波,说明该忆感器模型具有非线性特性,并且iAB的波形与ϕAB的波形相位相同,表明该模拟器实现的是感性忆感器元件模型.

图4表明仿真结果和实验结果同理论分析一致,证明了所搭建的浮地忆感器等效电路模型的正确性.

4 硬件实验验证

搭建基于图1所示通用模拟器的硬件实验电路,如图5所示:绿色电路板上所焊接为图1中的通用模拟器电路,以黄框标出阻抗元件Z1与Z2,以红框标出AD844 芯片,以白框标出AD633 芯片,并在右下角标出±15 V 直流电源线与接地线.根据表1所示,在通用模拟器的Z1与Z2处接入不同的电阻、电容和电感元件组合,能够分别在硬件电路实验中实现忆阻器、忆容器和忆感器模型,如图6所示,黄框与黄色字母R,L,C表示在通用模拟器中接入的不同阻抗元件的组合.

图5 通用模拟器硬件实验电路实现Fig.5.Implementation of the universal emulator in hardware experiment.

图6 在通用模拟器的Z1和Z2接入不同的电阻、电容和电感元件组合,分别实现忆阻器、忆容器和忆感器模型的硬件实验电路 (a) 忆阻器;(b) 忆容器;(c) 忆感器Fig.6.The experimenta lbreadboard implementation o f(a) memristor,(b) memcapacitor,(c) meminductor models based on the universal emulator by connecting different combinations of resistor,capacitor or inductor to Z1and Z2.

结合理论分析和仿真结果,通过硬件实验进一步证明所搭建的基于通用模拟器的忆阻器、忆容器和忆感器模型的正确性和有效性.其中,在硬件实验中采用信号发生器GW Instek AFG-2225 产生的正弦信号vAB=Uosin(2πft)=Uosin(ωt) (V),作为电路模型的二端口激励电压,芯片直流供电电压为±15 V.为了与仿真结果进行比较,采用示波器GW Instek-2102A 对实验结果进行记录,并通过Origin 9 软件绘制实验结果.

4.1 忆阻器电路响应

忆阻器硬件实验电路所采用的参数为:电容C1=1.22 nF、电阻R1=3 kΩ,R2=1.5 kΩ,R3=100 kΩ,直流电压Vs=-4 V,根据(18)式,可计算得到α1=1.09 S/Wb,β1=8×10-6S.加在忆阻器两端的正弦电压信号,幅值Uo=3 V,频率分别取70 kHz,80 kHz和100 kHz,得到图7实验结果.在实验中,根据忆阻器模型中Z2是元件R3和公式(9),得到流经忆阻器电流iAB正比于R3两端电压的负值,因此可以用等效表示iAB.

图7 忆阻器模型的硬件电路实验结果 (a) 不同频率激励下的忆阻器 vAB-iAB(用 vAB-(-vR3) 表示)特性曲线;(b)不同频率激励下的忆阻器忆导值 Wm与 vAB的关系图;(c)在Uo=3 V,f=100 kHz 下,vAB,iAB(用 -表示)、ϕAB(用 表示)和Wm的时域波形图Fig.7.Experimental results of the proposed memristor emulator:(a) Pinched hysteresis loops under different working frequencies;(b) variation curves of the memductance Wmplotted against the terminal voltage vAB;(c) time-domain wave-forms of vAB,iAB(represented by -),ϕAB(represented by ) and the memductance Wmwhen Uo=3 V,f=100 kHz.

从图7(a)可以看出,随着激励电压频率增大,忆阻器端电压与流经忆阻器两端的电流的李萨如相轨迹图vAB-iAB呈现磁滞环且逐渐向内收缩,磁滞回线的面积变小,与图2(a)一致.图7(b)显示的vAB-Wm关系图和图2(b)一致,Wm的变化区间随激励电压的频率增大而减小.等同于图2(c),图7(c)各变量在频率为100 kHz 下很好地呈现了忆阻器的非线性特性和阻性.图7的实验结果同理论分析和仿真结果趋势一致,证明了本文基于通用记忆元件模拟器搭建的浮地忆阻器等效电路模型的正确性和可行性.

4.2 忆容器电路响应

忆容器硬件实验电路参数为:电容C1=1.22 nF,C2=0.22 nF;电阻R1=3 kΩ,R2=1.5 kΩ ;直流电压Vs=-4V,通过计算(22)式可得α2=2.40×10-5F/Wbβ2=1.76×10-10F.忆容器的激励电压为正弦波,幅值Uo=3 V、频率f分别取f=65 kHz,80 kHz 以及100 kHz,实验结果如图8所示,图8(a)是忆容值的磁滞环波形vAB-qAB(用vAB-() 表示),图8(b)是忆容值Cm和vAB的关系图,图8(c)所示为vAB,qAB(用表示)、ϕAB(用表示)和Cm的时域波形图.

比较图8和图3可以看出,忆容器模型的硬件实验结果和Pspice 仿真结果一致,忆容器端电压和瞬时电荷的相图呈斜“8”字形的磁滞环,且磁滞环在相同幅值的正弦电压下,随着激励频率增大而向内收缩.并且图8(c)中呈非标准正弦波,验证了忆容器的非线性特性.通过其电路仿真和电路实验结果对比,验证了所搭建的浮地忆容器等效模型的有效性.

图8 忆容器模型的硬件实(验结果)(a)不同频率激励下的忆容器vAB-qAB(用vAB--表示)特性曲线;(b)不同频率激励下的忆容器忆容值 Cm与 vAB的关系图;(c) 在Uo=3 V,f=80 kHz 下 vAB,qAB(用 -表示)、ϕAB(用表示)和Cm的时域波形图Fig.8.Experimental results of the proposed memcapacitor emulator:(a) Pinched hysteresis loops under different working frequencies;(b) variation curves of the memcapacitance Cmplotted against the terminal voltage vAB;(c) time-domain wave-forms of vAB,qAB(represented by -),ϕAB(represented by ) and the memcapacitance Cm when Uo=3 V,f=80 kHz.

4.3 忆感器电路响应

忆感器硬件实验电路参数如下所示:电容C1=2.2 nF、电阻R1=3 kΩ、R2=10 kΩ、电感L1=20 mH,直流电压Vs=-2 V,根据(26)式可计算得α3=3.41× 1010(H·Wb)—1,β3=3 H-1.忆感器的激励电压幅值Uo=3 V,频率f=75 kHz,80 kHz 以及100 kHz,得到图9所示实验结果.根据忆感器模型中Z1是元件L1和公式(10)和(11),得到忆感器两端的磁通ϕAB正比于电阻R1两端电压的负值,因此可以用-vR1等效表示ϕAB.

图9 忆感器模型的硬件实验结果 (a) 不同频率激励下的忆感器 ϕAB-iAB(用 (-vR1)-(-vR2) 表示)特性曲线;(b)不同频率激励下忆感器的忆感值倒数 与 ϕAB(用-表示)的关系图;(c) 在Uo=3 V,f=80 kHz 下iAB(用 -表示)、ϕAB(用 -表示)、ρAB(用表示)和的时域波形图Fig.9.Experimental results of the proposed meminductor emulator:(a) Pinched hysteresis loops under different working frequencies;(b) variation curves of the inverse meminductance plotted against the flux ϕAB(represented by -) ;(c) time-domain wave-forms of iAB(represented by -),ρAB(represented by ),ϕAB(represented by -),ρAB(represented by ) and the inverse meminductance when Uo=3 V,f=80 kHz.

对比图4和图9可知,忆感器模型实验结果与仿真结果趋势基本一致.图9(a)表明忆感器磁通与流经忆感器电流的相图ϕAB-iAB呈斜“8”字形磁滞环,且随着激励频率增大,磁滞环向内收缩.图9(b)为激励频率为75 kHz,80 kHz和100 kHz下忆感值的倒数与磁通ϕAB的变化曲线,可以明显看出,具有频率依赖性,随着频率上升,取值以及ϕAB取值范围减小.图9(c)绘制了在激励频率为80 kHz 下各变量iAB(用表示)、ϕAB(用表示)、ρAB(用表示)和的时域波形图,不再为正弦型波形,但与两者相位相同,说明了此时模拟器具有非线性及感性特性,进而验证了该等效电路模型为忆感器.图4和图9表明仿真结果和实验结果同理论分析一致,证明了所搭建的忆感器等效电路模型的正确性.

5 结论

本文提出一种新型通用模拟器,并基于该模拟器实现浮地忆阻器、忆容器和忆感器建模,通过理论分析、仿真电路和硬件电路实验的一致性表明所搭建的3 种记忆元件模型具有记忆特性和非线性特性.与现有同类能够实现3 种浮地记忆元件模型的研究相比,本文所提基于通用模拟器的新型浮地记忆元件模型结构简单,易于硬件实现,工作频率高,对后续记忆元件研究和应用开发具有一定的参考价值.为了更好地完善记忆元件等效电路模型的研究理论,未来的研究工作可以着眼于忆耦器等效电路模型的搭建,并基于该模型进行忆耦器特性和应用研究.