浅析插座中浪涌保护器的设计技巧

2021-12-15郑银盛

管 丹 郑银盛 付 杰

(公牛集团股份有限公司 慈溪 315314)

引言

随着经济和科技的快速发展,越来越多高精密电子元器件被应用于智能生活电器之中,但是高精密电子元器件通常耐压水平较低,且其抗干扰能力较弱,因此这些带有高精密电子元器件的电器往往易受电网浪涌的影响,发生操作失控、卡机重启、性能衰退甚至电路烧毁等故障,由此可见,这些电器对于输入电源的稳定性有着极高的要求。然而较多插座厂商在产品研发过程中注重于产品功能的拓展,产品防护效果并不理想。

1 常见问题分析

1.1 压敏电阻损坏

如图1所示,为压敏电阻在测试时炸毁的照片。对于这款防浪涌保护器,出现该现象的主要原因为:①设计过程中,压敏电阻选型不合理所致,即施加在压敏电阻两端的工作电压超过其最大持续工作电压Uc;②脱扣保护装置未及时动作,导致压敏电阻无法承受浪涌的冲击量。

图1 VDR炸毁照片

1.2 线路板铜箔炸断

如图2所示,为脉冲过电压通过防浪涌保护器时大电流释放导致铜箔炸断的照片。出现该现象的主要原因是线路板铜箔过薄且宽度不足,铜箔载流量有限,致使脉冲过电压产生时,压敏电阻、放电管等元器件阻抗瞬间变低,极大的释放电流流经SPD非线性元件所在回路的铜箔,脱扣装置动作不及时,过高的电流在短时间积聚了过高的热量,导致线路板铜箔炸断[1]。

1.3 残压超标

关于SPD测试残压,我们可以引入欧姆定律U=I·R,将其理解为浪涌进入主回路时,释放电流乘以内阻(连接线、线路板铜箔、VDR等阻值总和)。对于残压较高的问题,其主要因素包括连接线线规不合理、PCB Layout不合理、元器件选型不合理等。

1.4 脱扣装置异常动作

在SPD设计过程中,为防止VDR失效导致起火、爆炸等问题,通常采用熔断器或断路器等脱扣装置对电路进行保护。对于插座SPD中脱扣装置的异常动作(包括但不限于未及时动作、不耐冲击等情况),往往问题出现于脱扣装置无法满足SPD性能要求。

2 设计技巧分析

本文围绕浪涌保护器的设计,结合认证测试常见问题,对插座中SPD的设计技巧进行了分析和探讨。

对于插座中的浪涌保护器,根据分类定义可知,其属于TYPE 3 SPD,通过吸收经过TYPE 1 SPD和TYPE 2 SPD的残余浪涌能量并转换为其他形式能量进行释放,从而起到保护后端电器的作用[2]。

2.1 总体设计

关于防浪涌插座的设计,我们通常采用在输入端添加电压限制型SPD或复合型SPD的方案,达到抑制瞬态过电压的效果。在SPD设计过程中,我们应根据需求确认主要参数:电压保护水平UP、最大持续工作电压Uc、标称放电电流In、最大峰值电流Imax等。在插座SPD的设计过程中,我们需注意其限制电压(在特定测试条件下SPD端子间测得的残压Ures的最大值)应低于产品要求的电压保护水平UP。

2.2 元器件选型

图2 SPD电流释放铜箔炸断照片

在插座中SPD元器件选型环节,我们需要选择正确的压敏电阻、脱扣装置、放电管等元器件型号,以满足产品性能需求。

1)压敏电阻选型

对于压敏电阻的选择,我们首先需要确定对应的压敏电压,考虑到VDR实际压敏电压U1mA与标称电压之间的偏差(我们选用1.1~1.2倍标称电压作为压敏电压),在实际交流电路中,我们需要考虑电源电压的波动(我们将其有效值的最大值设定为额定电压Uac的1.4~1.5倍),又因为正弦交流电压峰值为倍的电压有效值,经计算可知,我们选用VDR的压敏电压与额定电压之间的关系为:U1mA≈(2.2~2.5)·Uac。

在确认压敏电压后,我们还需确认所选用压敏电阻的最大持续运行电压Uc。查阅GB/T 18802.11-2020附录B,我们可知插座中SPD的参考试验电压UREF为255 V,(插座中SPD的标称额定电压应大于UREF)[3]。结合EN 61643-11:2012+ A11:2018中Annex ZC的ZC7.7提及的“电压限制元件的额定电压至少应为SPD标称额定电压的1.25倍”[4]。因此插座中SPD的VDR选型应满足Uc>1.25·UREF,因此压敏电阻的最大持续运行电压需大于319 V。

此外还需选择合适的压敏电阻的通流容量(根据VDR所需承受的暂态浪涌电流峰值进行选择),在实际选择过程中,我们应选用大于所需通流容量压敏电阻,以此在降低SPD残压的同时还能够延长器件使用寿命。

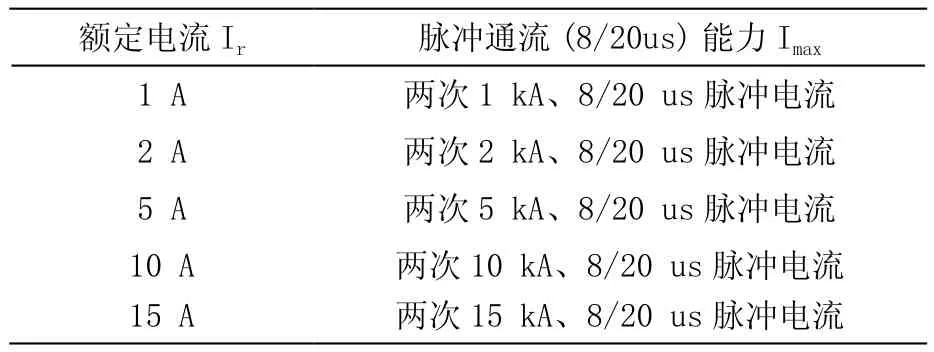

2)脱扣装置选型

关于SPD中的脱扣装置,在VDR失效形成短路时,过大的电流冲击无法被保护器吸收,脱扣装置将迅速动作,起到保护系统电路的作用。对于插座中SPD的设计,考虑成本、性能、工作环境等多方面要素,我们选用温度保险丝作为其中的脱扣装置。在温度保险丝的选型过程中,不宜选用有机物型温度保险丝(在浪涌电流冲击后,有机物型温度保险丝星状簧片与金属外壳间存在发生电流焊接导致保险丝永久短路的风险),因此我们应选用合金型温度保险丝[5]。在参数选定过程中,我们主要需要确定温度保险丝的通流容量、熔断温度、额定电流。考虑到温度保险丝与SPD浪涌吸收元器件之间的串联连接关系,温度保险丝的标称通流容量应稍大于SPD最大通流容量(温度保险丝的通流容量过低会导致提前短路,而其通流容量过高不仅会增加产品成本,还会导致VDR失效时温度保险丝还未及时动作);在温度保险丝熔断温度的选定过程中,考虑到温度保险丝在波峰焊制程中存在熔断损坏的风险,同时根据SPD在测试过程中表面温度低于120 ℃的规范要求,通常情况下,我们可选用115 ℃标称熔断温度的合金型温度保险丝作为SPD中的脱扣装置;对于温度保险丝额定温度的选定,我们应根据SPD设计需求与温度保险丝性能参数进行对比选定,例如表1所示,为115 ℃熔断温度的合金型温度保险丝的脉冲通流(8/20 us)能力Imax与其额定电流Ir间的关系。对于压敏电阻与温度保险丝之间的热传递方式,由于压敏电阻表面不平,往往会导致两者之间热耦合不尽人意,因此我们需使用压敏胶带或热缩套管将二者捆绑在一起,假若两者之间热耦合依然不如意,我们可在两者之间添加导热介质(例如导热硅胶等)。

表1 115 ℃合金型温度保险丝通流能力

当然,在成本预算充足的条件下,可以选择使用将合金型温度保险丝与压敏电阻集成为一体的热保护型压敏电阻(如图3所示),选用TMOV,不仅能够解决压敏电阻与温度保险丝之间热耦合不理想的问题,还能使得设计更为便捷。

图3 TMOV构造示意图

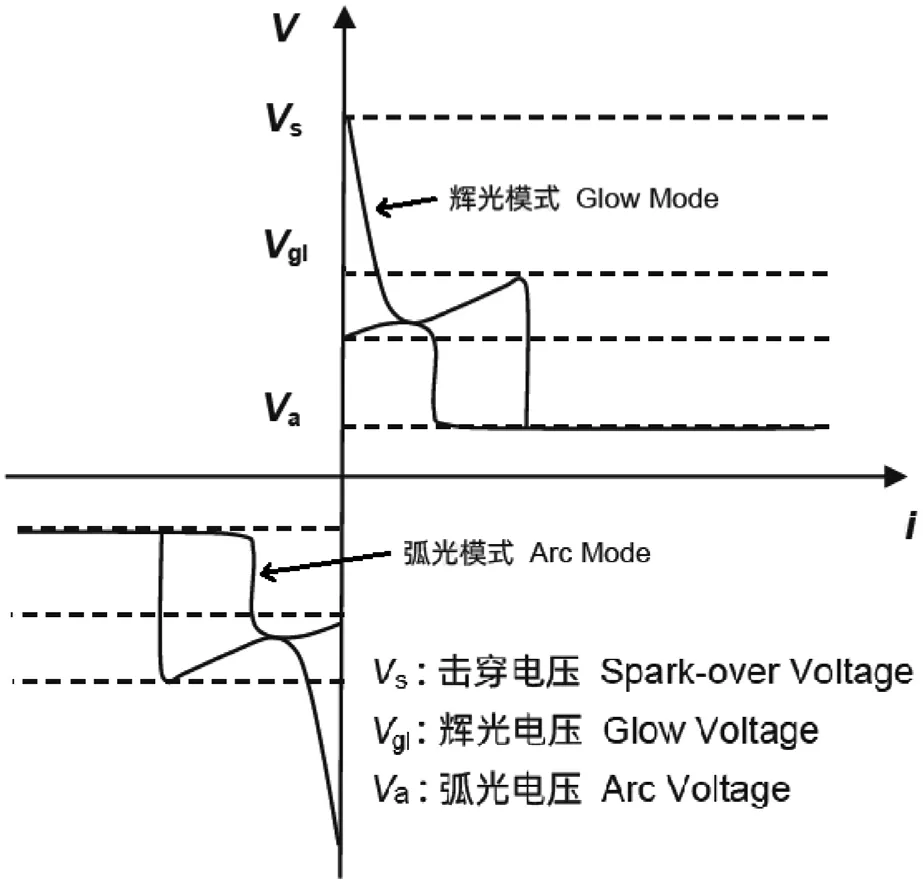

3)放电管选型

电压限制型SPD通常由压敏电阻与温度保险丝组合或由TMOV进行设计完成,而压敏电阻存在漏电流不稳定的缺陷,因此复合型SPD在电路中压敏电阻所在支路上串联气体放电管能够有效解决该问题。如图4所示,为气体放电管的电气特性图,因此插座SPD设计在GDT选型过程中,其最小直流击穿电压Vs必须高于电路工作时的最大电压,因此GDT直流击穿电压Vs与产品额定电压Uac之间的关系为Vs>2.1·Uac,因此插座SPD设计可选用470 V或600 V直流击穿电压的GDT;此外我们还应注意GDT标称放电容量不得小于产品通流容量。在此基础上,我们即可根据自己的需求选择合适的GDT。

图4 GDT电气特性图

2.3 电路设计要点

对于插座中SPD的设计,我们通常选用电压限制型SPD或复合型SPD的方案。

对于插座中的电压限制型SPD,其主体由压敏电阻和温度保险丝组合而成,基本电路如图5所示。在该电路中,压敏电阻和温度保险丝根据上文2.2所述,对元器件进行合理选择即可。当单个VDR无法达到所需通流容量时,我们可采取并联多个VDR,如此不仅可增加SPD通流容量,还能降低SPD残压以及延长器件使用寿命。

图5 电压限制型SPD基本电路设计图

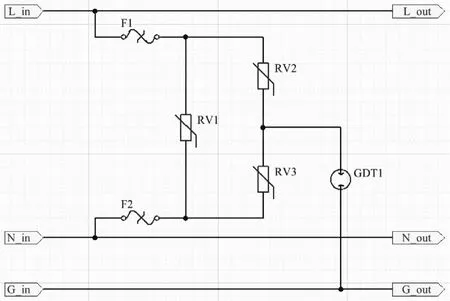

对于插座中的复合型SPD,我们可以理解为在电压限制型SPD基本电路上加入GDT构成,其基本电路如图6所示,其中,在脉冲过电压冲击下,GDT气体电离需要一定的时间(RV2、RV3和GDT1反应时间为各自反应时间之和),电路中的压敏电阻RV1可有效避免幅度较高的尖脉冲泄漏到输出端。

图6 复合型SPD基本电路设计图

对于插座中SPD的PCB Layout,在设计过程中,应根据安规标准确认各铜箔走线之间爬电距离和电气间隙,画板过程可使用丝印标记确保各铜箔走线之间距离符合安规。在画板过程中应确保放电路径尽可能短,载流路径则尽可能宽。此外,我们能以载流路径上开窗的方式,让PCB板过锡炉时载流路径焊上足够的锡,以此增加放电路径通流能力。

根据以上PCB Layout要点,我们可以将图6电路图绘制成对应PCB图(如图7所示)。

图7 复合型SPD PCB绘制图

3 结束语

本文从插座中浪涌保护器设计的常见问题出发,对问题原因及解决方案进行分析与探讨,结合笔者对元器件选型及对SPD电路设计要点的理解,综合阐述了插座中SPD的设计技巧,希望能帮助更多插座行业设计人员及业余爱好者理解并掌握插座中SPD的设计要点。