基于国产芯片与国产操作系统的轨道车辆车载安全计算机设计

2021-11-28张小松张长春李博健

张小松,张长春,李博健

(中车青岛四方车辆研究所有限公司,山东青岛,266031)

0 引言

目前轨道车辆核心控制系统主要包括:牵引辅助控制系统,网络控制系统、制动控制系统等。这些系统是车辆控制的核心,随着信息技术的发展,对这些系统的功能安全性、信息安全性、运算性能、实时性等都提出了更高的要求。功能安全需要满足欧洲电工标准化委员会(GENELEC)制定的相关标准[1],信息安全必须基于国产自主可控的软硬件产品,而运算性能与实时性需要软硬件自身性能的支撑。本文基于飞腾等国产芯片和国产翼辉操作系统,遵循EN50126《铁路应用:可靠性、可用性、可维护性与安全性(RAMS)规范和说明》[2]定义的要求,设计了一款列车专用安全计算机,满足了轨道车辆核心控制系统控制器软硬件自主可控及功能安全的需求,实现了列车牵引、网络、制动等核心系统的控制功能。

1 系统方案

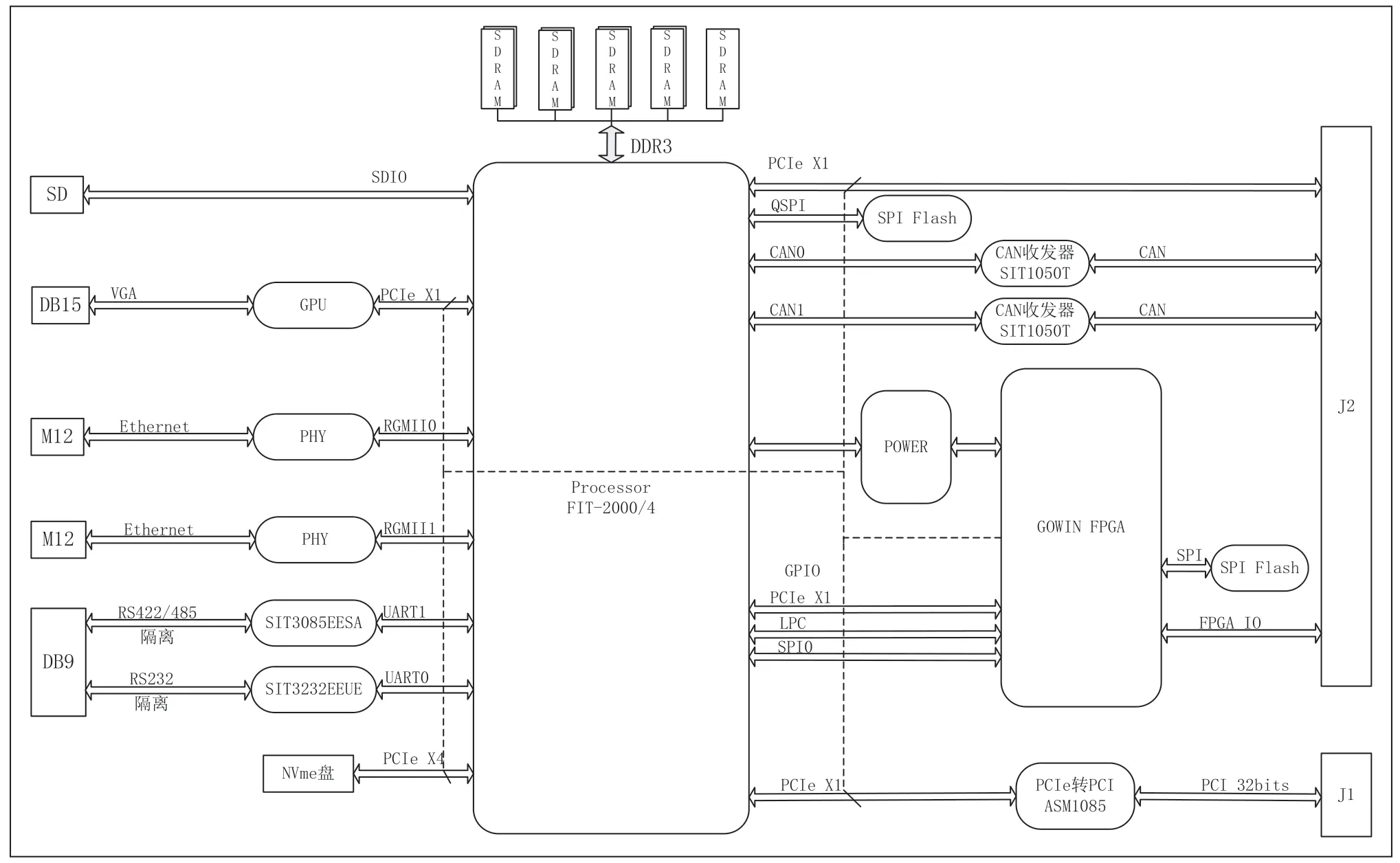

车载安全计算机采用国产芯片与国产操作系统设计,按照EN50129《铁路应用:铁路控制系统领域的安全相关电子系统》[3]标准定义的SIL2安全等级要求进行架构设计。其系统框图如图1所示,主要包括主CPU与监控CPU(FPGA)及系统外设三部分。电源、CPU、FPGA、存储、通信等核心芯片均采用国产芯片,芯片国产化率达到90%以上,软件采用国产翼辉实时操作系统保证系统的实时性与稳定性。

图1 车载安全计算机系统框图

■1.1 CPU方案

车载安全计算机主CPU采用天津飞腾公司自主知识产权的FT-2000/4芯片,该芯片集成4个飞腾自主的新一代高性能处理器内核FTC663,采用乱序四发射超标量流水线,兼容64位ARMV8指令集并支持ARM64和ARM32两种执行模式。FT-2000/4从硬件层面增强了芯片的安全性,支持飞腾自主定义的处理器安全架构标准PSPA,满足更复杂应用场景下对性能和安全可信的需求。FT-2000/4所有安全相关模块均为飞腾公司自主设计,可在CPU层面有效支撑可信计算3.0标准。

该CPU具有丰富的外设接口,具有4组PCIe接口:两路PCIeX16,两路PCIeX1。其中PCIeX16可以拆分成两路PCIeX8,因此可以最多挂载6个PCIe设备。本设计中CPU共挂有4个PCIe设备,分别是通过PCIeX4挂载NVME的硬盘;通过PCIeX1挂载GPU;通过PCIeX1挂载PCIe转PCI桥片;通过PCIeX1挂载FPGA,并在背板连接器预留PCIe X4用于外设的扩展。FT-2000/4集成两路RGMII接口的MAC控制器,支持两路千兆以太网通信。

■1.2 操作系统方案

车载安全计算机采用国产翼辉实时操作系统,该操作系统是翼辉信息公司设计的开源操作系统。该系统内核自主化率达到 100% (依据工信部评估报告),拥有完全自主可控的技术能力,满足国产化需求;支持 ARM、MIPS、PowerPC、x86、SPARC、DSP、RISC-V、C-SKY 等架构处理器,支持主流国产通用处理器,如飞腾全系列、龙芯全系列。该系统具备硬实时内核,调度算法先进高效,性能强劲;SylixOS 支持对称多处理器(SMP)平台,并且具有实时进程及动态加载机制,满足安全功能。本设计在飞腾CPU上移植了SylixOS,并基于相应外设开发了驱动程序,满足了铁路系统车载CPU的软件要求。

■1.3 安全完整性方案

安全完整性等级,又称SIL (Safety Integrity Level),是对系统所要求的安全完整性水平的一种定量指标,是将安全完整性根据安全功能失效的频率和产生的危险严重程度划分成的等级。系统的安全完整性等级越高,则其安全功能失效的可能性就越小,安全完整性一般分为4个等级[4]。目前,城市轨道交通安全可靠性技术主要的参考标准是欧洲电工标准化委员会(CENELEC)制定的铁路安全相关标准[1]。

EN50129[3]标准附录E.4定义了实现功能安全需要的系统结构。如果实现SIL2功能安全等级可以选择“1OO1D”架构,也即带自检和检测的单电子结构。该结构能够通过通过诊断电路进行功能的诊断,并在发生问题时采取安全措施进行导向安全的操作,这种“1OO1D”结构由一个单一的电子结构和与之独立的监视诊断电路组成,诊断电路对主处理电路的输入采集、运算、输出进行诊断,并能够通过与主电路串联的输出结构切断主电路的输出,保证整个功能电路的安全。

图2 1OO1D结构

如图1所示,整个系统包括主CPU与监控FPGA,主CPU是安全计算机的核心,是逻辑运算的执行主体,监控FPGA实现对CPU各功能的监视、诊断及安全措施的实施。FPGA与CPU间具有LBC总线、SPI总线、PCIe总线和GPIO。其中SPI用于CPU与FPGA间的生命信号传输。PCIe用于CPU逻辑数据与自身状态寄存器的状态的数据传输,以便FPGA对CPU内部状态进行实时诊断。LBC总线用于FPGA对CPU相关配置功能参数传输。FPGA通过GPIO实现对CPU上电、断电控制,在CPU发生异常时切断CPU供电,保证安全。与此同时,各个PCIe设备的时钟源来源于FPGA,当发生异常时FPGA切断PCIe总线通信,保证各个接口的通信安全。

2 硬件设计

车载安全计算机应用于轨道车辆控制系统中,对于稳定性与通用性具有较高要求,因此本CPU采用安全加固结构,所有芯片采用焊接方式。该系统具有丰富的外设接口,保证了系统的扩展性和通用性,尺寸为标准的3U结构的CPCI板卡。

■2.1 电源设计

飞腾CPU与众多CPU一致,具有多路电源轨,且每一路电源轨之间具有严格的时序要求。不同于传统的工控机需要一片专用的电源芯片或CPLD控制电源时序,本板卡电源系统采用多片矽力杰的DC/DC芯片,监控FPGA控制每一电源芯片的使能引脚,并根据每一电源芯片的PowerGood信号进行各个电源轨的时间延时,从而完成CPU的上电时序。这样既节省了CPLD又能通过FPGA实现对CPU的电源诊断功能,当每一电源出现异常时,FPGA通过PowerGood信号诊断,并通过IO切断所有电源的输出,保证CPU导向安全侧,通过其上电流程图如图3所示。

图3 安全计算机上电流程图

■2.2 DDR设计

飞腾CPU支持两个DDR的访问通道,每个通道包含64个数据位和8个ECC校验位,本设计采用9片紫光国芯的512MB的DDR3芯片,其中8片用作数据存储,1片用作ECC校验。这样整个CPU可用内存达到4GB,并且具有ECC校验。ECC(Error Checking and Correcting)是在数据位上额外的位存储一个用数据加密的代码。当数据被写入内存,相应的ECC代码与此同时也被保存下来。当重新读回刚才存储的数据时,保存下来的ECC代码就会和读数据时产生的ECC代码做比较。如果代码不一致,他们则会被解码,以确定数据中的哪一位是不正确的。然后这一错误位会被抛弃,内存控制器则会释放出正确的数据。

这样的采用ECC的DDR可以充分保障数据操作的准确性和安全性,能够达到SIL2安全等级中对数据存储的安全需求。

■2.3 CPU存储设计

传统的工控机一般采用SATA接口的机械硬盘或电子盘,其中机械硬盘不适合轨道交通多振动冲击的应用场景,而SATA接口的电子盘接口尺寸不满足轨道交通控制器结构紧凑的要求,因此采用国产M.2接口的固态盘,通过CPU的PCIE接口直接与其通信,这样既保证了集成度又保证了数据存储的读写速度。

■2.4 CPU外部接口设计

该安全计算机具有丰富的外部接口设计,能够满足轨道车辆控制系统的多种应用场景。具有两路千兆以太网,通过前面板M12连接器引出,两路以太网采用CPU内置MAC,并采用国产裕太车通千兆PHY芯片。该系统具有VGA接口,飞腾CPU通过PCIe挂载国产GPU,并将GPU的VGA接口引出至前面板DB15连接器。安全计算机具有一路RS232和一路RS485,两路均通过前面板的DB9引出。背板具有标准的PCI总线,通过PCI总线CPU可以扩展外部设备,该PCI总线通过PCIe转PCI桥片实现。背板还具有两路CAN总线,CAN总线利用FT2000/4自带的控制器,并采用国产芯力特CAN收发器实现。

表1 安全计算机外设接口表

3 CPU软件设计

整个CPU软件采用翼辉实时操作系统,该系统在启动及运行中通过调用系统级的寄存器进行状态的实时自检,并且将状态位通过PCIe传输给FPGA进行诊断,如果一旦发生诊断错误FPGA会进行系统级的安全导向。

按照EN50128[5]附表A.3之要求,安全通信协议需要增加检错误码,以此来防范数据传输错误带来的风险。各个有安全需求的外设,以太网、CAN总线、RS485等,采用安全通信协议,在应用层增加数据序列号,时间戳,CRC校验,保证数据传输的安全,达到SIL2通信安全要求。下表为数据传输风险与对应防范措施的对照表2。所有的安全通信协议发生表2的错误后,CPU通过PCIe把对应的状态寄存器置位,FPGA检测相应的错误寄存器,在发生数据通信异常时,FPGA通过切断对应芯片接口芯片电源或切断时钟的方式保证安全通信。

表2 数据传输风险与对应防范措施

4 总结

本文设计的基于国产芯片与国产实时操作系统的安全计算机实现了轨道车辆核心控制系统的自主可控,并填补了国内基于国产芯片与系统的安全计算机的空白,该CPU已经应用于轨道车辆牵引、网络、制动等核心控制器,实践证明该控制器具有优良的性能,较好的扩展能力,在实时性要求高、可靠性要求高的场合具有优异的表现。基于SIL2的安全构架,具有良好的安全性能,能够大幅提高系统的安全性,保证核心系统的安全可用。