基于FPGA的多通道数据采集系统设计应用

2021-11-19中国人民解放军92236部队王旭东陈涛郑磊

中国人民解放军92236部队 王旭东 陈涛 郑磊

随着当今科学技术的不断发展,各种信号采集技术的研究也得到了不断深入。其中,以FPGA为基础的多通道数据采集系统更是备受关注。为实现该系统的良好应用与发展,本文特以某数据多通道采集系统为例,对其FPGA设计进行了研究。希望通过本次的研究,可以为该FPGA技术的应用与多通道数据采集技术的发展提供相应参考。

0 引言

在进行数据采集系统的设计和研究中,FPGA技术所发挥的优势十分显著。将该技术合理应用到多通道数据采集系统中,并将其作为系统的核心,便可有效解决传统数据采集系统中的接口复杂难题,为系统的应用和扩展提供足够便利。因此,在对此类系统进行研究的过程中,技术人员一定要加强FPGA的应用研究,使其在该系统中发挥出充分的技术优势。

1 以FPGA为基础的多通道数据采集系统概述

在传统形式的数据多路采集系统中,其数据采集系统通常是将MCU作为核心,以此来实现多路信号采集与处理的控制。但是因为单片机处理速度和指令周期的影响,普通形式的MCU在数据处理以及A/D转换方面都很难达到系统的实际应用需求。但是如果可以将FPGA作为该系统的核心部分,凭借着其集成度非常高的器件以及十分丰富的内部资源,便可对多路形式的并行数据进行有效处理,让系统对于相应数据的实时采集与实时同步需求得以良好满足。

2 总体结构设计

本次某数据多通道采集系统的设计中,将FPGA和ARM进行结合,通过FPGA来实现采集主控制逻辑;通过ARM对控制数据的储存与传输。其中,A/D形式的转换器为TI公司所生产的ADS1255高精度模数24位转换器;FPGA应用的是Altera公司所生产的EP2C35型FPGA;ARM应用的是ARM9内核形式的S3C2410处理器。通过EP2C35型内存处理器块来进行双口形式的RAM配置,这个双口形式的RAM连接着ARM系统中的总线,并映射成为ARM中的一个内存区域。以下是该系统中的主要组成及其功能简述。

(1)AD前端处理电路:其主要功能是对信号进行衰减、放大和阻抗匹配,让系统对于输入信号的实际要求得以良好满足。

(2)滤波网络:其主要功能是将工频信号以及高频噪声干扰滤除,对ARM中的控制信号进行增益放大,让模拟信号得到不同程度的增益放大处理。

(3)ADS1255:其主要功能是实现模拟电信号到数字信号的转换,具体应用中 可通过相应的设置使其在各种工作模式中发挥出有效作用。

(4)FPGA:其主要功能是为ADS1255进行工作时钟提供,通过其输出时钟频率的改变便可改变AD采样频率。FPGA可以对5路AD数据采集实现并行控制,同时也可以将采集到的每一路数据按照相应顺序,在双口形式的RAM中进行字节写入与缓存。对于双口形式的RAM数据,FPGA主要借助于乒乓传输结构来进行读取,在将双口形式的RAM上半区写满之后,FPGA便会将中断申请发送给ARM,在ARM接收到这个申请并响应中断之后,便会将上半区的数据读出,并将其储存到内存中[1]。在此过程中,FPGA会继续将相应的数据写入到ARM下半区,然后以同样的方式发出中断申请。在此过程中,借助于乒乓传输的形式,可以让系统采样以及数据传输的进行保持连续。

3 系统中的FPGA逻辑模块设计

在本次所涉及的以FPGA为基础的某数据采集系统中,其数据采集的基本流程如下:首先是系统的初始化,在完成了系统的初始化之后,ARM会借助于控制信号向FPGA发送通道选择以及采集频率等参数情况的通知,在FPGA接到了相应的通知之后,便会将一个统一形式的时钟提供出来,这一步骤主要借助于同步采样通道中相应的AD芯片来完成。然后便是进行相应通道的选择,并对数据进行同步采样与转换,采样和转换的结果会通过FPGA进行接收,通过RAM中与之对应的空间进行储存。接下来再通过ARM在相应双口形式的RAM空间中进行数据读取,并根据实际需求将其储存在本地,或者是通过网络上传到上位机中对其进行进一步的处理。

3.1 通道与采样率选择模块设计

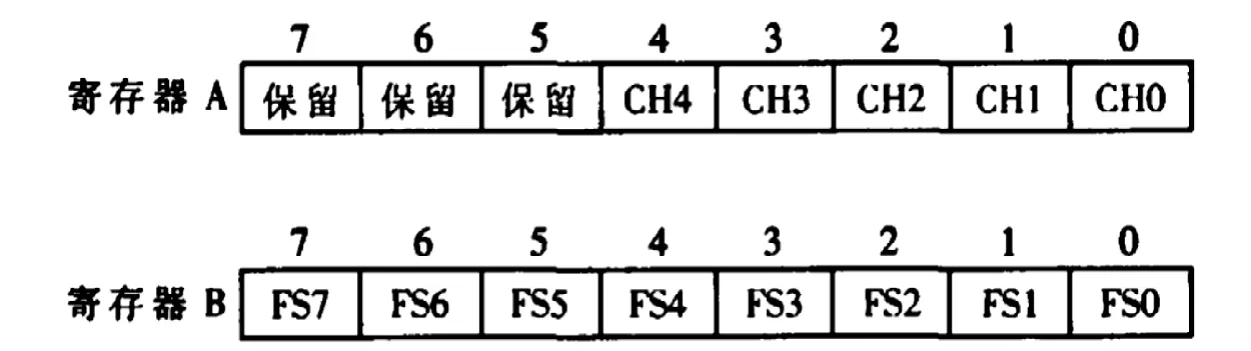

在该系统的具体应用中,并不是所有的通道都会参与到工作中,而AD也不仅仅有一种采样率,基于此,在对通道控制以及采样率进行设置的过程中,应使其具备良好的可选择性特征。在本次所研究的以FPGA为基础的多通道数据采集系统中,通道以及采样率选择模块中包含两个控制寄存器,分别为寄存器A和寄存器B,其规格均为8Bit。具体情况如图1所示:

图1 寄存器A和寄存器BFig.1 Register A and Register B

在储存器A中,0-4Bit分别和ADC这一通道中的CH0-CH4相对应,而5-7Bit则需要保留;在寄存器B中,8Bit分别和采集率中的FS0-FS7相对应。若需要对某几个通道进行选择,仅仅将寄存器A内的相应位置设置为1,其他位置设置为0,AD采样控制模块便会按照这个寄存器里的具体内容来形成相应通道。如果需要对某采样频率进行选择,仅仅需要将寄存器B内与之对应的位置设置为1,将其他位置设置为0,便会在时钟模块中产生一个与之对应的AD采样率控制时钟[2]。在数据采集系统开启之前,ARM将会按照实际需求将通道以及采样频率命令字写入到储存器A与储存器B中。

3.2 时钟模块设计

在本次设计中,外部输入形式的时钟是16.384MHz,因每一个模块都具有不同的工作时钟,AD采样率也具有不同的变化形式,所以就需要很多不同形式的时钟信号。而在该系统设计中,时钟模块便可按照采样率的不同来将不同的时钟信号提供给与之对应的模块。因本次设计所应用的电路为同步时序形式,它是时钟终触发沿作为基础来进行设计的电路形式,对于时钟的抖动、延时、占空比以及周期都有着非常高的设计要求。基于此,在被测设计中,主要是通过FPGA中带有的PLL时钟资源来进行主时钟的驱动设计,使其抖动和延迟都降到最低。

3.3 双口形式RAM模块设计

在本次系统设计中,双口形式的RAM模块主要用来进行时护具储存,首先是AD芯片转换之后的数据进行储存,其次是对为ARM数据读取所做的进一步数据储存和处理。该模块中的两个端口控制线、数据线以及地址线都相互独立,可同时存取数据。具体设计中,这个双端口形式的RAM模块主要是通过对Altera中带有的参数化模型库调动来实现。

3.4 A/D形式采样控制模块设计

在该系统中,A/D形式的采样模块主要是按照ADS 1255中具体的转换时序图,让时序控制信号从芯片引脚发出,以此来完成ADS1255的启动、配置以及数据读取等的各项操作。在对ADS1255进行控制的过程中,首先需要对其参数配置进行设置,并进行数据模读取,然后才可以启动转换,通过对ADS1255中DRDY信号的查询,便可对是否完成了转换进行判断,在转换完成之后,系统便会按照Bit大小顺序将数据读出,并将数据输出到串并转换模块中,对其进行A/D转换[3]。在每一次的采样操作完成之后,采样控制模块都会停止下来,并等待下一次的触发脉冲。

3.5 串并转换模块设计

因为ADS1255的转换结果输出形式为串行输出,所以在具体设计中,这一模块需要再一次对串行输出数据进行转换,使其变成并行输出数据。本次设计中,主要借助于移位寄存器来满足这一功能需求,而其移位信号则是通过AD采样控制模块来进行提供。

3.6 数据储存和控制模块设计

在本次所设计的系统中,数据储存控制模块的主要功能是将五个通道中的24Bit数据通过串并转换之后,再按照通道顺序,以字节从低到高的次序中逐一将各个字节写入到双口形式的RAM中,所以就实际而言,这一模块类似于字节并串转换装置。在这一模块中,reg24Data-0-4这五路采样数据是其输入数据;dataF字节数据是其输出数据,wernF是双口形式的RAM写控信号数据。为确保该模块的应用效果,本次设计中特对其进行了仿真,具体仿真中,其输入数据为0x030103、0x060504、0x090807、0x121110以及0x151413,在将这五路采样数据输入之后,其输出的字节数据是10-15,同时可以写入到RAM中[4]。由此可见,本次的数据储存和控制模块设计满足该系统的实际设计需求。

3.7 ARM接口控制模块设计

在本次所研究的系统中,ARM模块的主要作用是给ARM和FPGA与双口形式的RAM提供出一个交互的桥梁。在通过RAM将采集参数信息写入到控制储存器的过程中,接口模块便会向采集选择以及通道模块进行相应信息的通知。在通过ARM对双口形式RAM内的数据进行读取的过程中,接口模块便会进行ARM访问地址的译码操作,在选中了相应储存空间之后,便可将数据取出。

4 结语

综上所述,在数据多通道采集系统的设计中,通过FPGA以及ARM这两者的结合应用,可有效实现多通道条件下的高精度数据采集和数据处理。基于此,在该系统的具体设计中,设计者应该将FPGA作为系统核心,以此来实现数据采集、转换、处理以及传输等的各项操作控制;然后通过ARM来进行采样数据的储存和相应处理。在此过程中,设计者应格外重视FPGA中的各个逻辑模块设计。通过这样的方式,才可以让FPGA在数据多通道采集系统中发挥出充分的技术优势,解决传统数据多通道采集系统中的技术弊端,实现相应数据的全面、精确获取,为各方面工作提供足具科学性的技术与数据支撑,以此来有效促进相关领域的良好发展。

引用

[1] 贾亮,丛龙杰.基于FPGA的高速数据采集系统研究[J].电脑与信息技术,2021(3):69-71.

[2] 钱素琴,孙悦.基于AD9226的FPGA高速数据采集电路设计[J].电子测试,2021(11):5-8.

[3] 孙嘉霖,李艳辉,霍琦,等.基于FPGA的六维并联机构的数据采集系统设计[J].机电工程技术,2021(5):121-124.

[4] 李茂林.多路数据采集传输系统的FPGA设计与实现[J].计算机时代,2021(4):49-53.