基于STM32的嵌入式存储系统的设计与实现

2021-11-04段素平

段素平

(中国船舶重工集团有限公司第七一〇研究所,湖北 宜昌 443003)

0 引言

当前,嵌入式技术发展越来越快,对大容量数据存储的需求也越来越迫切。传统的嵌入式系统或产品一般只带有Flash、ROM等存储器,只能存储少量数据,若嵌入式系统需要存储大容量数据,目前常用的存储设备有 SD存储卡、U盘、Flash芯片等。Flash芯片存储容量小、价格高,且需要集成在PCB印制电路板上使用;U盘虽然存储容量高,但设计相对比较复杂,占用空间比较大,连接可靠性不高[1];而SD存储卡体积小、存储容量高,支持SPI/SDMMC驱动,多种尺寸可供选择满足不同应用需求,优势明显[2-3]。基于此,设计了一种以SD存储卡作为存储设备的嵌入式存储系统。

1 硬件设计

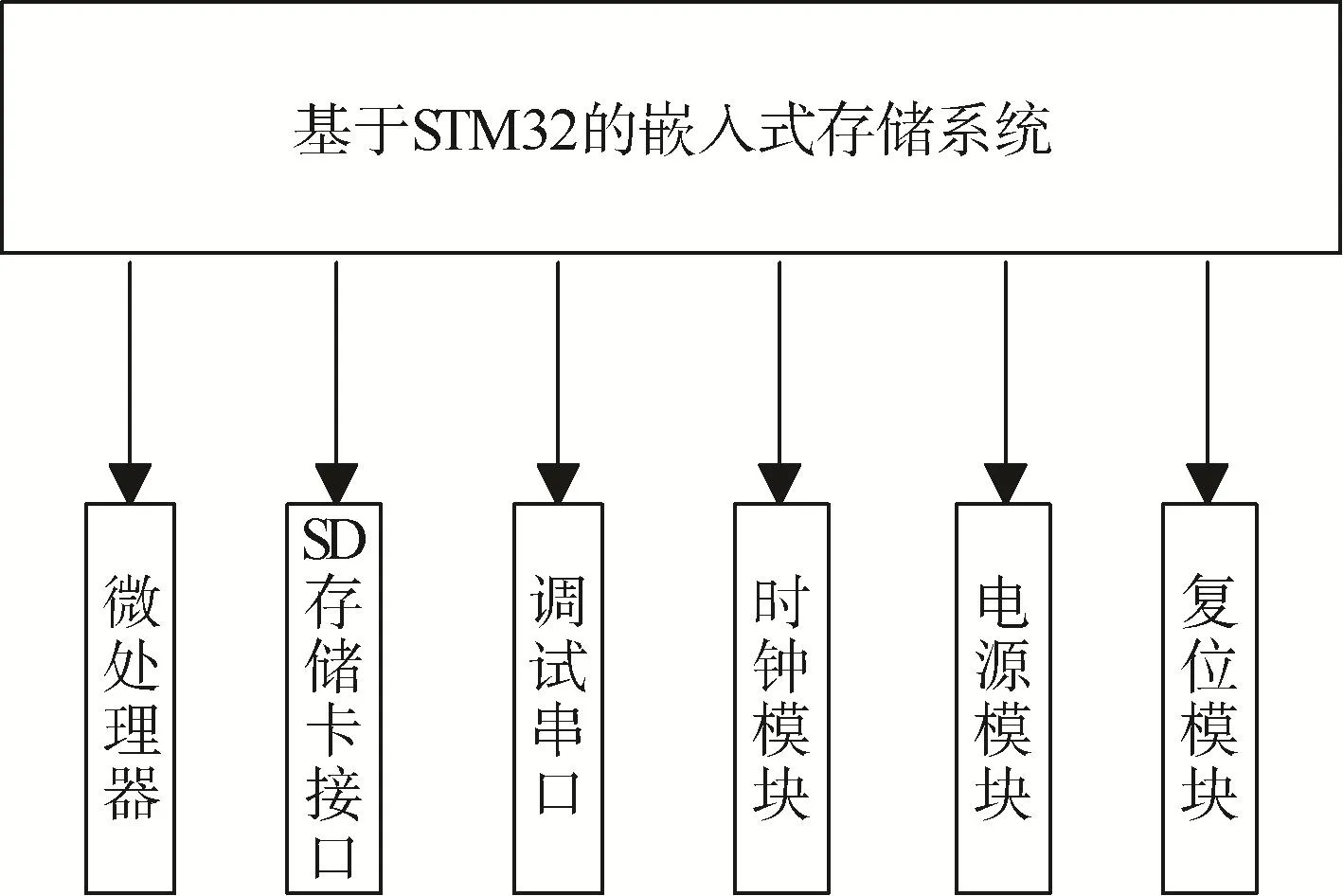

本系统主要由微处理器、SD存储卡接口电路、复位模块、电源模块以及时钟模块等组成,如图1所示。其中复位模块、电源模块以及时钟模块设计比较简单,也不是本系统设计重点,所以本文不作介绍。

图1 系统组成示意图Fig.1 Diagram of system composition

1.1 硬件电路设计

1)微处理器。

微处理器主要负责控制整个系统的处理操作、状态监测以及任务管理等功能,最重要的是实现大容量数据快速可靠的存储和读取。选择STM32H743作为本系统的微处理器,该处理器是 ST 推出的基于 ARM Cortex M7 内核的处理器,拥有高达1 060 KB 的片内 SRAM,并且支持 SDRAM内存扩展。STM32H743工作频率达到400 MHz,具有6级流水线,带有指令和数据Cache,大大提高了性能。此外,STM32H743自带丰富的外围接口,其中就包括SDMMC接口控制器[4],利用该接口控制器可以很高效地实现SD存储卡接口电路设计。

2)SD存储卡接口电路。

STM32H743自带SDMMC控制器,最高通信速度可达48 MHz[5],如图2所示。本系统利用该控制器实现SD存储卡接口电路设计。

图2 SDMMC控制器示意图Fig.2 Diagram of SDMMC controller

在 SDIO 模式下,只需要用到:SDMMC_CK、SDMMC_D[3︰0]、SDMMC_CMD 这几根线即可正常驱动 SD 卡,电路设计原理图如图3所示。

图3中,SDIO_D0-SDIO_D3为数据线,实现数据传输,所有的数据线都工作在推挽模式。SDIO_CLK为时钟线,对应 SDMMC控制器的卡时钟SDMMC_CK(每个时钟周期在命令和数据线上传输1位命令或数据),在3.3 V信号电平下,该时钟频率最大可以达到50 MHz。需要注意的一点是,在 SD 卡刚刚初始化的时候, SDMMC_CK时钟是不能超过 400 kHz 的,否则可能无法完成初始化,在初始化以后,就可以设置时钟频率到最大了[6]。SD_CD为SDMMC控制器通用命令信号线,对应SDMMC控制器的SDMMC_CMD,SDMMC的所有命令和响应都是通过 SDMMC_CMD 引脚传输的,任何命令的长度都是固定为48 位[7]。

图3 SD卡接口电路原理图Fig.3 Schematic of SD card interface circuit

3)调试串口。

串口(串行通信接口)是指数据一位一位地顺序传送,其特点是通信线路简单,只要一对传输线就可以实现双向通信,从而大大降低了成本。RS232是最常用的一种串行通信接口,也称标准串口[8],本系统使用RS232用作调试接口,实现系统状态信息的打印输出。

由于STM32H743输出的都是TTL电平,即逻辑“平,对应2~3.3 V,逻辑“逻辑对应0~0.4 V,而 RS232标准采用负逻辑,即逻辑“1”对应-5~-15 V,逻辑“0”对应+5~+15 V[9]。为了实现两者之间的串口通信,利用ADM3251芯片进行电平的转换,电路设计如图4所示。

图4 调试串口电路原理图Fig.4 Schematic of debugging serial circuit

1.2 PCB抗干扰设计

为了提高系统的可靠性和抗干扰能力,在设计硬件平台时完成了以下工作:

1)将数字地和模拟地分开设计,电源线、地线的走向和数据线的走向平行设计,以提高抗干扰能力。

2)电源线设计得尽可能宽,减少环路电阻。

3)分布在电路板正反两面的信号线进行垂直处理,在需要拐弯的地方设计成135°角。

4)PCB板上的过孔会带来一定的电容效应,设计的时候尽量减少过孔数量。

2 软件设计

本系统软件设计用到的工具主要是 MDK,MDK源自德国的KEIL公司,它使用 uVision5 IDE集成开发环境,是目前针对 ARM 处理器,尤其是 Cortex M 内核处理器的最佳开发工具[10]。

2.1 FatFS文件系统移植

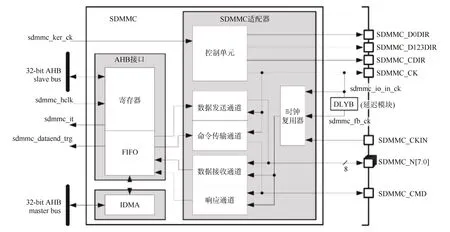

对于存储设备的管理,若采用传统读写扇区的方式,不但会影响系统的性能,也无法发挥SD存储卡的优势,因此本系统移植FatFS文件系统对存储设备进行数据管理。FatFS文件系统是一个完全免费开源的 FAT文件系统模块,该系统为应用程序开发提供统一的、标准的API函数,具有良好的可维护性和移植性[11]。FatFS 文件系统的层次结构如图5所示。

图5 FatFS文件系统的层次结构图Fig.5 Hierarchy diagram of FatFS file system

最顶层是应用层,使用者无需理会 FatFS 的内部结构和复杂的 FAT 协议,只需要调用FATFS模块提供给用户的应用接口函数,如 f_open,f_read,f_write 和 f_close 等,就可以像在 PC 上读写文件那样简单[12]。中间层 FATFS 模块,实现了 FAT 文件读写协议,使用时只要将需要的头文件包含进去即可。需要编写移植代码的是FatFS模块提供的底层接口,它包括存储媒介读写接口(diskI/O)和供给文件创建修改时间的实时时钟。

FATFS 模块在移植的时候,一般只需要修改源码中ffconf.h 和 diskio.c 两个文件。FATFS模块的所有配置项都是存放在 ffconf.h 里面,通过配置里面的一些选项,来满足系统的需求;diskio.c实现底层驱动,需要编写如图6所示的6个接口函数[13]。

图6 FatFS底层驱动接口函数Fig.6 Interface function of FatFS underlying driver

disk_initialize( )函数实现磁盘驱动器的初始化;disk_status( )函数的功能是返回当前磁盘驱动器的状态;disk_read( )函数读取磁盘驱动器上的数据;disk_write( )函数是往磁盘驱动器上写入数据;disk_ioctl( )函数用来控制设备指定特性和除了读/写外的杂项功能;get_fattime( )函数用来获取当前时间。

2.2 应用程序设计

在成功移植FatFS文件系统基础上,需要完成应用程序的编写,应用程序完成的工作如下:

1)系统硬件初始化,包括配置系统时钟、HAL库初始化、使能Cache以及配置系统中断等。

2)SD 存储卡接口初始化,主要利用STM32H743自带的SDMMC控制器对SD存储卡接口进行初始化操作。

3)FatFS文件系统初始化,将SD存储卡在磁盘的编号设置为0,并通过f_mount( )函数为SD存储卡注册一个工作区。

4)完成 SD卡存储功能,先调用 f_open( )函数创建一个新文件或打开已存在的文件,然后调用f_write( )函数将缓冲区的内容写入到刚打开的文件中,最后调用f_close( )函数关闭已打开的文件。以上步骤即可完成SD卡的数据存储。

5) 完成SD卡读取功能,先调用f_open( )函数打开数据存储文件,然后调用f_read( )函数将文件内容写入到缓冲区,并作出相应处理,最后调用f_close( )函数关闭已打开的文件。以上步骤即可完成SD卡的数据读取。

2.3 软件可靠性设计

SD存储卡的较高读写速率可能会导致读写错误的发生,为了降低错误发生的概率,提高系统的可靠性,本系统软件设计时采取以下措施:

1)读写数据采用校验方式来检验数据的正确性,同时为了避免校验和正确而数据错误的极其偶然情况发生,对数据层面进行再次检验,比如给加入数据帧头,在读写数据时均对数据的帧头加以判断。只有当数据帧头以及数据校验和均正确,才会认为本次数据有效。

2)读写错误发生后,对数据进行循环读写,直到正确读写数据才跳出循环。

3 系统验证

为了验证系统的功能,设计了2组测试。第1组为基本功能测试。测试在 SD存储卡中新建目录或文件、在文件中读写数据等功能。在SD卡根目录下新建根 SD_BasicFuctionsTest”目录和“sd_test.txte文件,并在“sd_test.txte文件中写入测试数据。之后读取SD卡中所有信息,观察是否含有“SD_BasicFuctionsTest”目录和“sd_test.txtes文件。若存在该文件,读取该文件数据,观察是否和之前写入的数据一致。

第2组为系统性能测试。测试系统读写SD卡速度(大容量数据存储系统中,数据读写速度是一个很重要的设计指标)以及读写可靠性。在 SD卡根目录下新建“Speed.txt”文件,往该文件全速写入2 048 kB数据,计算其写入速度;之后全速读取“Speed.txt”文件中的数据,计算文件读取速度。同时将读取的数据与之前写入的数据进行比较,统计匹配度。

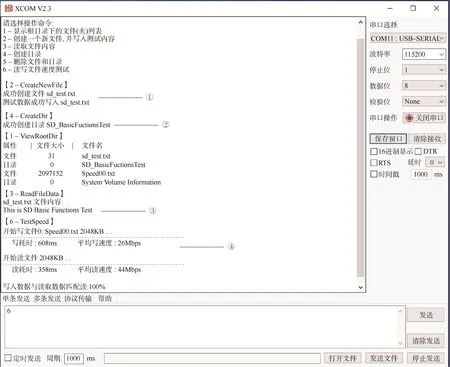

上述的测试步骤,本系统都通过调试串口打印相应信息,如图7所示。

图7 调试串口打印的测试信息Fig.7 Test information printed by the serial port

图7中的①表明系统成功创建了文件“sd_test.txt”,并成功写入测试数据;②说明系统成功创建了“SD_BasicFuctionsTest”目录。之后读取“sd_test.txt”文件数据,该数据与之前写入的数据一致,如图中③所示。图7中的④是系统性能测试时打印信息情况,可知SD存储卡读写速度分别达到了44 Mbps和26 Mbps,可满足大部分应用需求。读写数据匹配度达到了100%,说明系统可靠性符合要求。

4 结束语

本文主要对嵌入式存储系统进行了讨论和研究,成功完成了系统的硬件设计和软件设计。最后,通过2组试验对系统的基本功能、读写速度以及可靠性进行了测试,测试结果充分验证了本系统设计的正确性。