密码SoC中算法IP核通用接口模型

2021-11-02南龙梅

王 凯,李 伟,陈 韬,南龙梅

(1.信息工程大学 信息安全重点实验室,河南 郑州 450001; 2.复旦大学 微电子学院,上海 200433)

0 引 言

密码算法的实现方式主要包括:通用处理器、专用指令处理器、FPGA(field programmable gate array)、密码逻辑阵列和密码算法IP核(intellectual property core)等[1]。其中,密码算法IP核是运算性能最高、功耗和面积最小的方式,长期以来受到广泛应用。

密码SoC(system on chip)通过将通用处理器、密码算法IP核、存储和接口模块等单元集成到单颗芯片上,能够实现数据加解密、消息签名/验证和数据完整性验证等密码应用,已经成为保障信息安全的核心部件。半导体与集成电路技术的迅速发展,使得密码SoC的功能越来越强,规模越来越大,基于密码算法IP核集成的设计方法,在密码SoC设计中得到了广泛应用。如何实现不同类型密码算法IP核的统一管理和高效调度,对于增强密码SoC整体灵活性和高效性具有重要意义。

AMBA(advanced microcontroller bus architecture bus)总线是ARM公司研发的一种片上总线系统,支持多个主/从设备的快速连接和芯片级测试,在密码SoC设计中得到了广泛应用。其中AHB(advanced high performance bus)总线作为AMBA的高级高性能总线,广泛应用于密码SoC中处理器与算法IP核的高速连接。

针对密码SoC中算法IP核的调度控制的研究主要有几种。文献[2]实现了基于FPGA的SDIO通信接口,但无法适用于多种密码算法IP核运算需求。文献[3]实现了一种FPGA通用串行接口设计,但数据传输速率慢,严重限制了密码算法IP核运算性能。文献[4]完成了一种基于FPGA的动态部分可重构智能I/O接口设计与实现,但需要通过TCP/IP网络数据包切换总线接口配置指令,配置信息量很大。文献[5]完成了一种面向通用可重构计算的外存访问接口设计,但是硬件开销较大,且不能主动进行数据传输。

针对以上问题,本文紧密结合密码SoC和不同密码算法IP核的实际应用需求,深入分析不同的分组、序列、杂凑和公钥密码算法的编码原理及硬件实现差异,从数据传输过程和运算控制信号等方面提取出大量共性逻辑,提出了一种通用数据包格式和数据通信协议,能够在进行数据传输的同时,根据各种算法的运算需求,快速完成接口适配,使其满足不同算法、工作模式和运算阶段的运算控制需求。同时提出了一种可编程逻辑电路,高效完成数据包解析和通信协议转换,能够实现与不同密码算法IP核间的数据通信与运算控制。最后又针对密码算法IP核的数据传输设计了一种专用DMA(direct memory access)控制器,能够独立快速完成密码算法IP核与片上存储间的数据传输。

1 密码SoC概述与密码算法实现

1.1 密码SoC结构概述

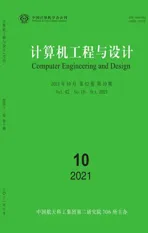

密码SoC作为当前满足用户信息安全需求的主要方式,其内部除了通用处理器、片上总线、存储和接口模块之外,还必须包含多种密码算法IP核。典型的基于AMBA总线的密码SoC基本结构如图1所示。

图1 基于AMBA总线的密码SoC基本结构

面对日益突出的信息安全问题,单一种类的密码算法已经无法满足用户多样化的密码应用需求。尤其是近几年研究的研究热点问题,如零知识证明和可信计算等,要求密码SoC必须能够灵活高效调用多种密码算法IP核,以此满足用户越来越高的信息安全需求。

一般来说,密码算法IP核通常只针对密码算法的运算实现,必须通过接口模块挂载到AHB总线上,才能与系统其它模块实现数据通信。接口的设计,直接影响密码算法IP核管理调度的灵活性和密码处理的高效性[6]。

1.2 基本密码算法实现与分析

1.2.1 管理调度需求分析

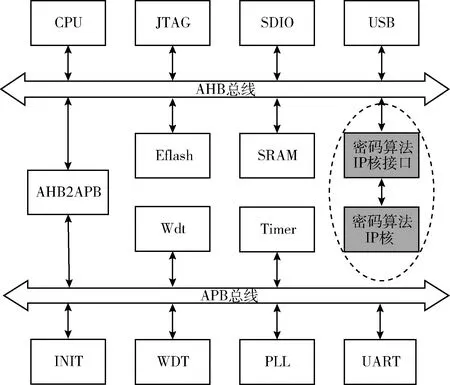

常用的密码算法可分为序列、分组、杂凑和公钥密码算法4种类型[7]。不同类型密码算法由于其编码原理不同,其硬件实现过程有很大差别,如图2所示,非常不利于密码SoC的统一管理和调度控制[8]。

图2 不同体制密码算法的硬件实现过程

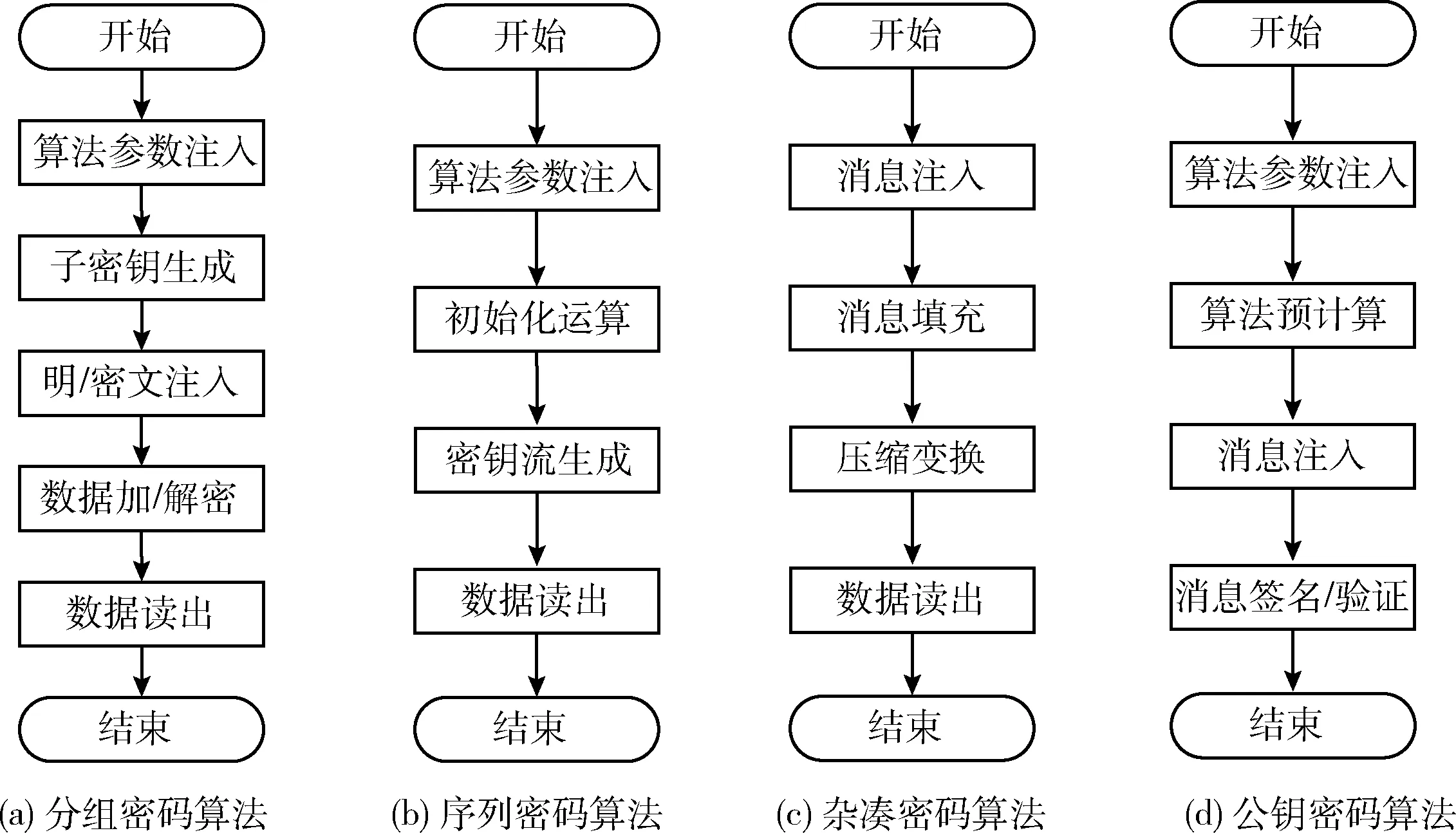

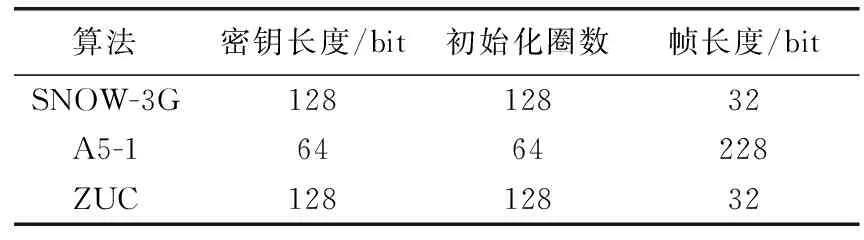

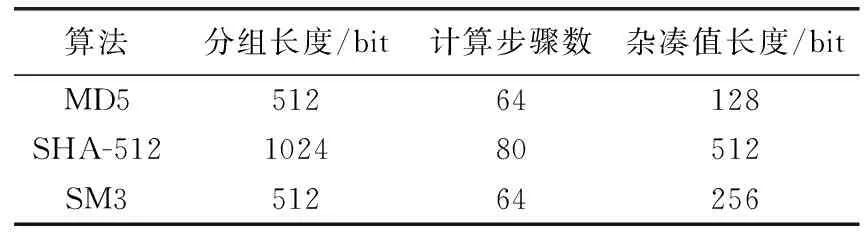

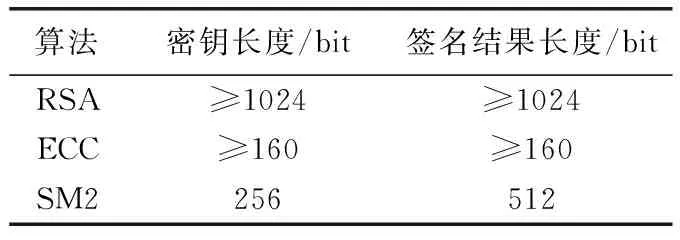

表1至表4分别统计了几种典型的分组、序列、杂凑和公钥密码算法的基本参数信息。

表1 典型分组密码算法参数比较

表2 典型序列密码算法参数比较

表3 典型杂凑密码算法参数比较

表4 典型公钥密码算法参数比较

通过分析,密码SoC要实现多种算法IP核的统一管理调度,必须要解决3个问题[9]:数据传输、运算控制和状态反馈。

1.2.2 数据传输需求分析

密码算法IP核的数据吞吐率β是衡量密码SoC整体运算性能的重要标志,其值可表示为

(1)

其中,算法IP核的时钟频率fIP、分组长度Lgroup和完成一次密码运算的时钟周期数Ps,针对特定密码算法IP核均为固定值。而数据写入时钟周期数Pin、数据读出时钟周期数Pout和传输等待时钟周期数Pwait,受总线宽度和传输方式影响,在不同的应用环境中差别较大。

实验发现,密码算法IP核在硬件设计时的理论数据吞吐率通常较高,而集成到SoC内部后的实际吞吐率却很低,而究其根本原因在于总线数据传输效率较低,无法满足算法IP核运算需求[10]。

限制算法IP核数据吞吐率的原因主要有两种[11]:

(1)数据输入过程较慢,造成数据断流,算法IP核必须等下一组明文数据注入完成以后,才能启动运算;

(2)数据读出过程较慢,造成数据阻塞,算法IP核必须等上一组加密结果读出完成以后,才能启动运算。

而影响数据传输效率的原因主要有两点,也是本文中通用接口模型优化的重点:

(1)输入/输出FIFO(first input first output)深度;

(2)总线带宽利用率;

当输入/输出FIFO深度Din和Dout设置为不同大小时,一组数据的密码运算过程如图3所示。

图3 不同FIFO深度下的一次密码运算过程

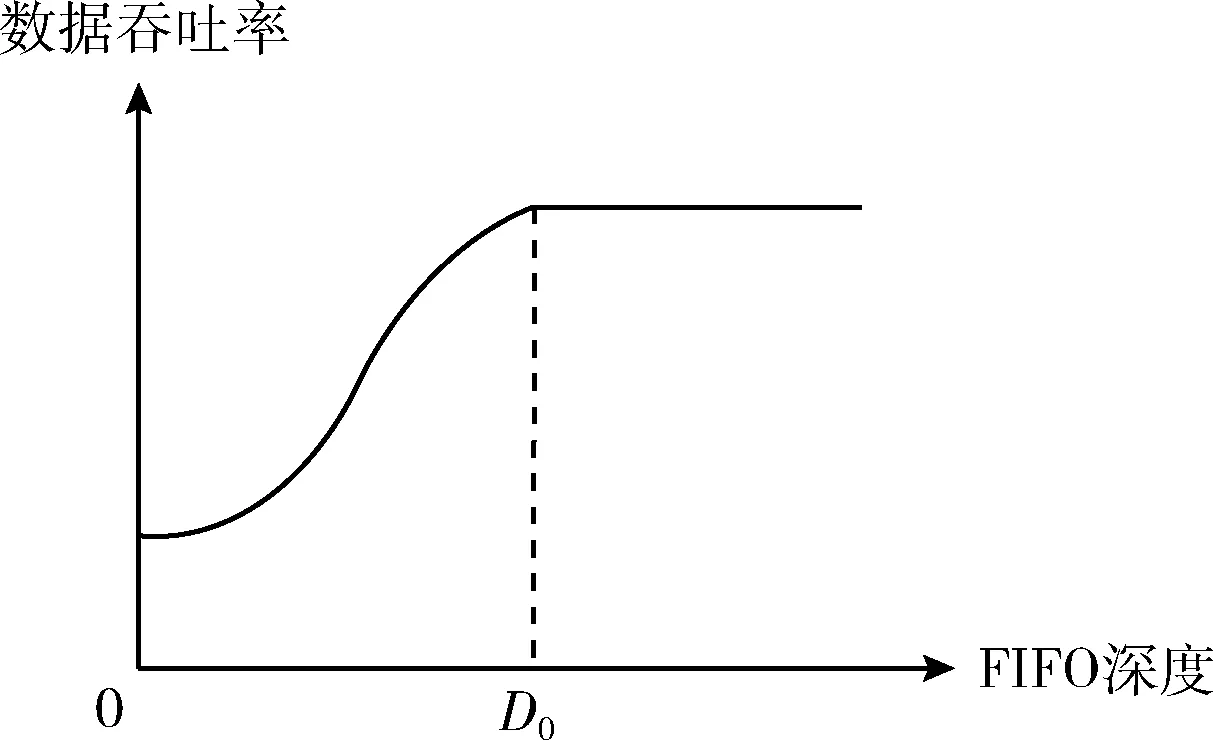

密码算法的数据吞吐率随输入/输出FIFO深度变化的曲线如图4所示。

图4 不同FIFO深度下的算法数据吞吐率

若输入FIFO能够存储的数据量小于运算所需的一个分组长度Lin,很容易造成数据断流,因此,输入FIFO的深度Din必须满足

(2)

同理可得,在不造成输出数据阻塞的情况下,输出FIFO的深度Dout也必须满足

(3)

在保证密码算法IP核性能不受限的情况下,要使得接口电路面积最小,则输入/输出FIFO深度Din和Dout应当设置为相应的最小值。

假设总线数据传输的带宽利用率为η,其值可表示为

(4)

其中,Pd表示在一次数据传输过程中,数据传输所占用的时钟周期数,而N则为总线空等待的时钟周期数。通常来说,总线带宽利用率为η无法达到100%。

要实现极限数据吞吐率,数据传输必须满足的条件是:Pwait=0,即:在算法IP核的一次运算过程中,其接口必须将上一次的运算结果全部读出,且将下一次运算所需的消息全部写入,亦即:完成一个分组读写的总时间不能大于一次密码运算的时间,用公式可表示为

(5)

其中,输入/输出数据长度Lin和Lout、总线宽度Lbus、总线时钟频率fbus受到具体算法和密码SoC系统影响,通常难以改变。在最大限度保证密码算法IP核的快速运算的情况下,接口与总线进行数据传输时,总线带宽利用率η应当满足的条件为

(6)

此时,数据传输所占的时钟周期数Pd应满足

(7)

因此,接口在进行数据传输时,可按照不同算法、工作模式和运算阶段的运算需求,配置专用DMA数据传输方式,确定每次连续数据传输的字数,进而确定数据传输所占的时钟周期数Pd,使接口数据传输过程能够满足密码运算需求,充分发挥算法IP核运算性能。

2 通用数据包与数据通信协议

密码SoC调度多种算法IP核的传统方式,主要有两种:

(1)接口定制[12],即针对特定算法IP核定制接口电路,使其能够正确挂载到片上总线。这样每调用一种算法都必须重新设计接口,较大增加了密码SoC设计复杂度和工作量;

(2)算法可重构[13],即采用可重构技术,使设计出的电路结构能够通过配置实现不同的密码算法。这种方式主要有两个不足之处:一是对于同一算法,可重构电路会增加芯片面积,降低算法性能;二是可重构技术只能用于编码原理相近的算法,而无法适用于所有算法,更无法满足密码SoC同时调度多种算法的实际需求。

本文通过分析不同类型密码算法IP核的数据传输过程,及运算控制需求,从中提取出大量共性特征,并提出了一种通用数据包和数据通信协议,能够在实现算法IP核数据输入的同时,完成对接口的配置,使其能够适配不同类型的密码算法、工作模式和运算阶段,进而实现多种应用场景下,对多种算法IP核的统一管理调度。

2.1 通用数据包设计

密码算法IP核在运算过程中所需的外部信号主要可分为两类:运算控制类和待处理数据。根据算法编码原理和运算需求,不同类型算法运算过程差异较大,而同一密码算法通常也存在多种不同的工作模式,难以实现统一控制。此外,算法IP核在运算过程中也需要密钥、初始向量IV、命令控制和消息数据等多种类型的外部数据,难以进行统一管理。

因此,密码SoC要实现对算法IP核的统一管理和调度控制,必须通过统一的数据传输机制,在完成基本参数和数据注入的同时,实现对接口的配置,使其能够根据实际需求适配不同类型的算法IP核,并在不同工作模式下完成相应的调度控制。

本文充分考虑不同类型密码算法的运算差异的同时,提取出大量共性逻辑,设计了一种通用的数据包格式,在数据传输过程中,总线按照“包头+数据”的格式[14],首先通过包头发送与数据传输和运算控制相关的关键信息,然后将算法参数和消息数据依次注入接口。而接口则通过数据包解析,完成数据传输任务,并产生算法IP核的运算控制信号。每次数据传输的格式如图5所示。

图5 通用数据包传输格式

包头内存储与密码算法IP核运算相关的关键信息,直接决定本次数据传输的实现过程。在本设计中,包头共分两组,每组各32 bit。其中Mater_sel表示主机选择信号,决定数据传输是被动还是主动传输方式;W_R为读写控制信号;Data_type为数据类型;Mode为数据读取模式,可配置为“查询读”或“中断读”的方式,Length为数据长度。第二组包头中Addr_bus为片上存储地址。

2.2 数据通信协议设计

密码SoC实现完整的密码应用包含多个层次:应用层、算法层、运算层和传输层,如图6所示。

图6 密码应用实现的层次关系

在本设计的数据通信协议中,密码SoC调用单个算法IP核,主要可分为3个阶段:初始化运算阶段、算法运算阶段和运算结果读取阶段。

每次需要启动密码运算时,CPU根据实际运算需求,按照“包头+数据”的格式,首先对接口进行配置,并向密码算法IP核注入参数、命令或数据,接口再将数据根据需要注入算法IP核,同时发出相应的运算控制信号,算法IP核随即启动相应的运算操作。

运算完成后,若为“中断读”模式,则接口直接向CPU发出中断信号,随后将数据读出。若为“查询读”模式,则CPU可在需要读取数据时,先查询算法IP核运算状态,再将数据读出。

3 可编程电路结构研究与设计

不同类型的密码算法IP核,由于编码原理和硬件实现方式的不同,所需的外部控制信号和状态反馈信号存在较大差异。传统的接口电路,在实现对算法IP核的运算控制和状态读取时,大多采用状态机的方式,虽然实现简单,但灵活性较差,无法满足多种算法、多种工作模式和多个运算阶段的实际需求。

本文在通用数据通信协议的基础上,采用可编程技术,设计了一种通用电路结构[15],能够灵活实现AHB总线对不同类型算法IP核的运算控制和状态读取。

3.1 通用接口整体架构设计

密码算法IP核通用接口主要完成AHB总线与不同算法IP核间的数据传输、运算控制和状态反馈,实现系统统一管理和调度控制。另一方面,为了减少通用处理器的性能浪费,实现快速数据传输,该接口还需要具备独立完成数据传输的功能。

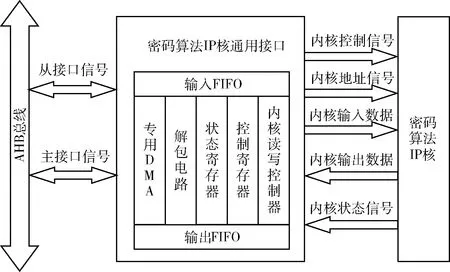

本文通过分析不同类型密码算法IP核的硬件实现方式和实际运算需求,通过可编程技术,设计了一种通用接口电路,使其能够适配不同类型密码算法IP核,其整体结构如图7所示。

图7 密码算法IP核接口整体结构

整个接口左侧为AHB总线协议标准的主接口和从接口信号,右侧为密码算法IP核的控制信号、地址信号、输入/输出数据和状态反馈信号。接口内部则主要由输入/输出FIFO、专用DMA、解包电路、状态寄存器、控制寄存器和内核读写控制器组成。

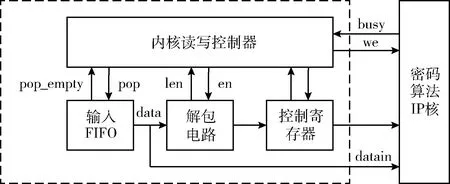

密码运算过程中,总线写入的所有的包头和数据都先缓存在输入FIFO。输入FIFO与算法IP核间的数据通信模块如图8所示,是确保整个接口功能正确性的关键。

图8 输入FIFO与算法IP核的数据通信模块

此外,不同密码算法IP核硬件实现差异导致运算性能也不同,且大都难以与总线时钟频率匹配。因此,本设计的输入/输出路径均采用异步双端口FIFO实现。系统运行时,专用DMA采用与AHB总线相同的低频时钟,其余部分的时钟频率则设为密码算法IP核的最大时钟频率,两部分独立运行,在保证系统正常运行的同时,最大限度发挥密码算法IP核的运算性能。

3.2 通用信号转换机制

AHB总线与算法IP核之间的协议转换核心主要在于运算控制和状态反馈,而不同的算法IP核由于运算过程的不同,在这两个方面存在较大差异。针对这些差异,本文设计了一种通用信号转换机制,其核心就在于控制和状态寄存器,二者可直接与算法IP核通信,共同存储与整个运算过程相关的关键信号。

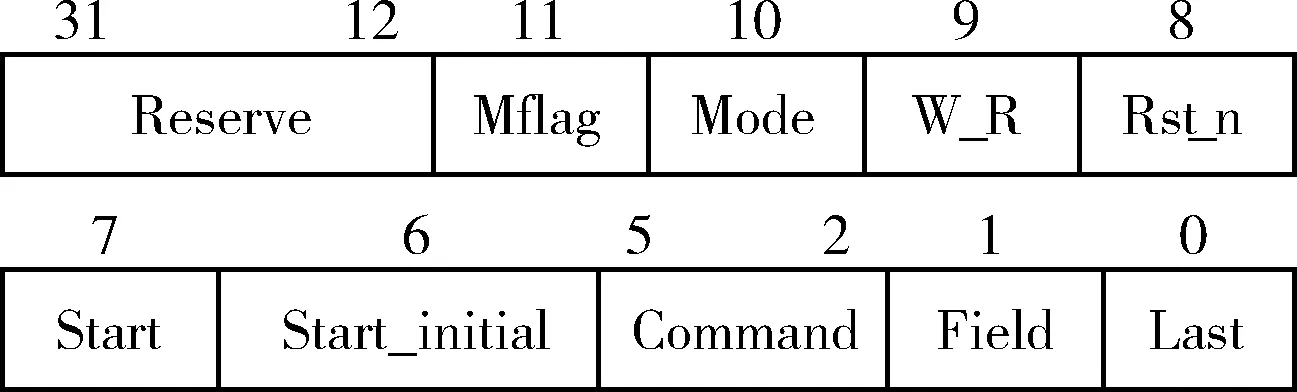

控制寄存器针对不同类型密码算法和多种工作模式的运算需求,设置了多种运算控制信号,实现对算法IP核数据传输与运算的直接控制,如图9所示。其中Last信号为最后一组分组信号的标志;Field为椭圆曲线密码算法域选择信号;Command为运算控制命令;Start_initial为初始运算启动信号;Start为密码运算启动信号;Rst_n为系统复位信号;W_R为读写控制信号;Mflag为主机选择信号;Mode为接口工作模式。

图9 控制寄存器结构

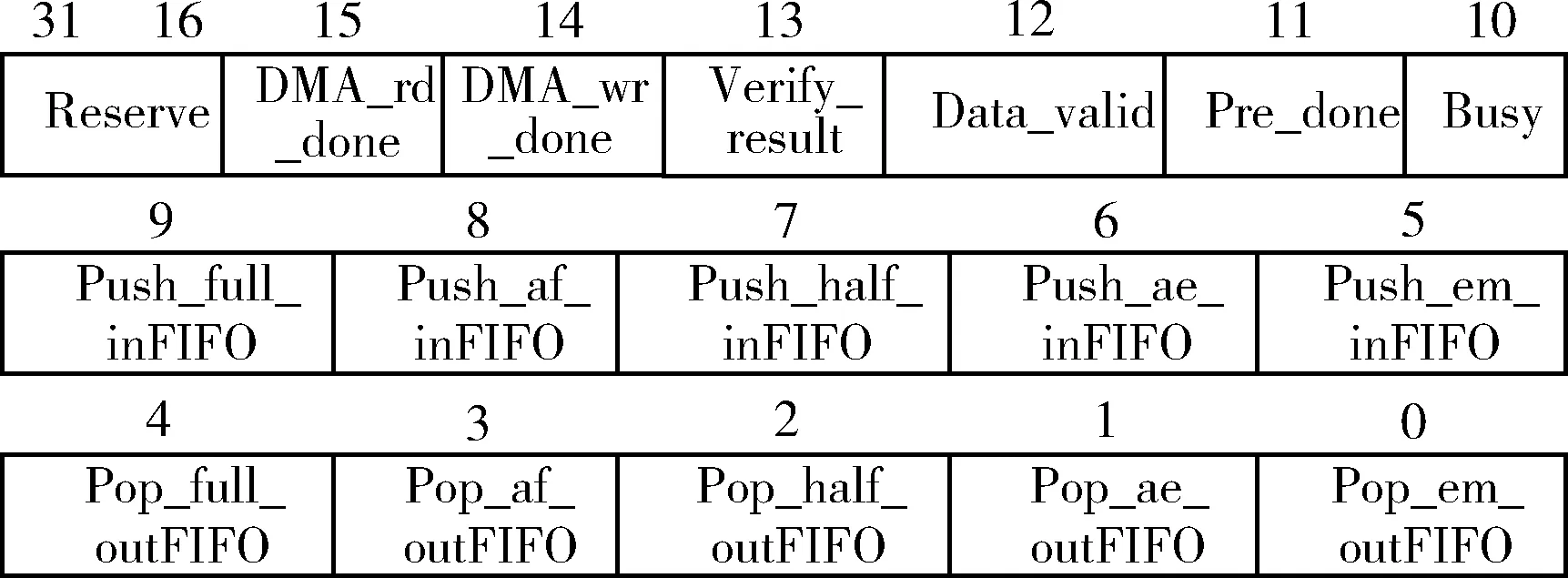

状态寄存器负责收集算法IP核的运算状态信号,以及接口数据存储和传输的状态信号,并反馈给总线,便于CPU判断进行下一步操作,其结构如图10所示。其中低10位分别为输入/输出FIFO的存储状态信号;Busy信号为内核运算忙信号;Pre_done为内核初始运算完成信号;Data_valid为内核运算完成信号;Verify_result为公钥密码算法的消息验证结果标志信号;DMA_rd_done和DMA_wr_done为专用DMA读/写完成信号。

图10 状态寄存器结构

密码SoC需要调用不同类型密码算法进行密码处理时,只需将接口内控制寄存器和状态寄存器的不同信号与对应IP核的相关信号进行连接,然后再挂载到AHB总线即可。

3.3 专用DMA设计

3.3.1 专用DMA数据传输方式

密码SoC中的数据传输一般可采用通用处理器和DMA两种方式[16]。当进行大量数据的密码处理时,通过通用处理器进行数据传输速率极慢,且会浪费其运算性能,而通用DMA面积较大,硬件成本较高。本文针对密码算法IP核的数据传输,在接口内部设计了一种专用DMA控制器[17],专门负责密码算法IP核与片上存储之间的数据搬运工作,极大提高了数据传输性能。

DMA的工作方式主要包括3种:CPU暂停访问、交替访问和周期挪用[18,19]。按照式(6)中的要求,专用DMA必须要有尽量大的总线带宽利用率,才能充分发挥密码算法IP核运算性能。因此本文采用CPU暂停访问的方式,能够最大限度提升DMA的数据传输速率[20]。

此外,密码算法IP核在工作过程中,通常不会进行同时读写操作,本设计中的专用DMA取消全双工设计[21]和多通道设计[22,23],尽可能地缩减硬件开销,提高电路最大工作频率。

3.3.2 专用DMA硬件设计

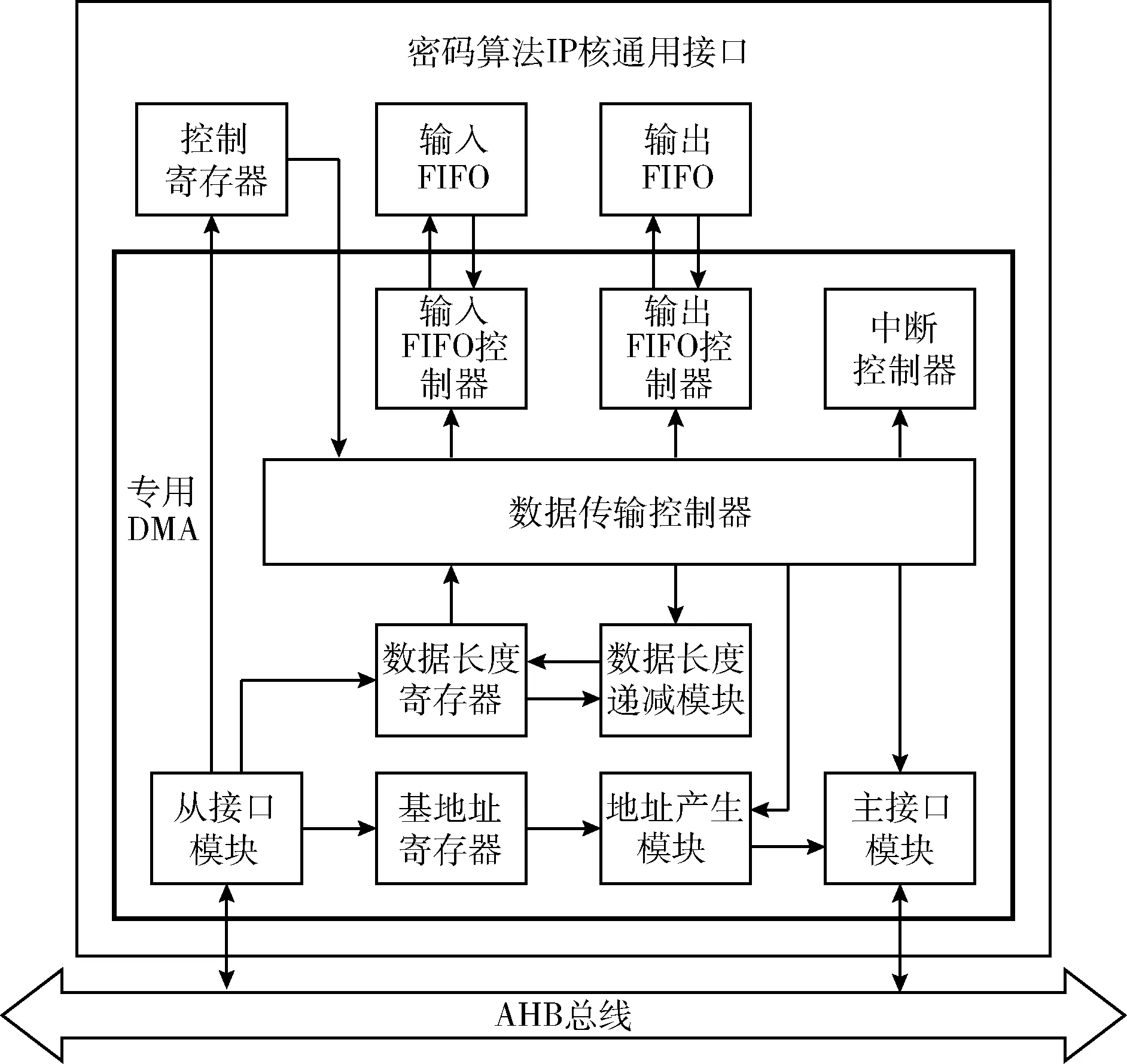

专用DMA作为直接决定通用接口模型数据传输性能的模块,其电路结构如图11所示。

图11 专用DMA整体结构

整个专用DMA按照其功能特点,可划分为3个层次10个部分。

第一层包括专用DMA与AHB总线实现信息交互的主接口模块和从接口模块,负责协议转换,主要通过状态机电路,实现专用DMA与AHB总线之间的运算控制和数据传输。

第二层为专用DMA的核心部分,共包括数据传输控制器、基地址寄存器、地址产生模块、数据长度寄存器、数据长度递减模块以及中断控制器。这一部分主要完成整个专用DMA的状态运行和数据传输控制。

第三层则包括输入/输出FIFO控制器,在读写控制状态机的控制下,能够建立FIFO与片上存储直接进行数据传输的通道,将来自片上存储的数据注入输入FIFO,或将运算结果由输出FIFO搬运到片上存储单元。

数据传输控制器作为专用DMA最核心的部分,直接影响整个DMA的数据传输效率。为最大限度提高专用DMA的数据传输性能,本文中的数据传输控制器采用“状态机+计数器”方式进行设计,状态转换图如图12所示。这种设计的优点是:

图12 专用DMA数据传输控制器状态转换

(1)状态数量少,能够简化状态跳转过程,提高系统可靠性,同时减少状态存储和状态译码的面积消耗;

(2)状态跳转可配置,能够按照式(7)和算法输入/输出数据长度Lin和Lout、总线宽度Lbus、总线时钟频率fbus和算法IP核的时钟频率fIP,计算得出数据传输所需的最小时钟周期数Pd,即状态跳转时的计数器值,由此使得专用DMA能够在不同算法、工作模式和运算阶段,实现对应的最佳数据传输方式。

当需要进行密码运算时,CPU首先按照不同算法的运算需求,对接口进行配置,包括目标地址、数据传输方式、传输方向和数据长度等。数据传输控制器再根据传输模式,决定通过CPU进行数据传输,还是采用专用DMA主动完成数据传输,以及专用DMA的最佳数据传输方式。

4 设计验证与评估

为了验证可编程高性能接口的正确性、灵活性和高效性,本文构建了一套基于AMBA总线的密码SoC测试平台,其内部不仅包含通用SoC的基本单元,如RISCV处理器、通用DMA、片上存储模块(SRAM、Eflash)、多种接口单元(UART、USB和SDIO等)和其它功能模块(JTAG、INIT、Timer、Wdt、PLL等),能够执行常用的用户程序,还集成了密码算法IP核接口和多种密码算法IP核,便于灵活高效实现多样化密码应用。

为了充分发挥密码SoC各个模块的运算性能,保证整个系统的高速运行,本文采用多时钟域设计,其中将AHB总线时钟频率设置为200 MHz,而密码算法IP核则设置为与之对应的最大时钟频率,使得密码运算性能最大化。而为了使整个接口的性能和面积达到最优,接口中的输入/输出FIFO按照算法的分组长度进行设置。

密码算法IP核的数据读写,可通过通用处理器、通用DMA或接口内专用DMA实现。其中采用通用处理器进行数据传输的方式速度最慢,且会影响处理器执行系统程序,浪费其运算性能,进行大量数据的密码运算时一般不采用。

专用DMA作为通用接口模型中的重要模块,其设计的合理性及数据传输效率,直接影响整个接口的数据传输性能。为验证专用DMA的设计合理性,本文首先将其与DesignWare软件生成的通用DMA及文献[17-21]中的通用DMA进行对比。

为验证专用DMA模块数据传输的高效性,本文将专用DMA放在SoC验证平台下进行峰值传输速率测试,并进行对比,结果见表5。

表5 DMA测试结果对比

测试结果表明,本设计中的专用DMA,专门针对密码算法IP核的数据传输进行设计,能够建立接口内FIFO与片上存储直接进行数据传输的通道,独立快速完成接口与片上存储间的数据传输,且能够按照不同算法、工作模式和运算阶段的数据传输需求进行适配,实现最佳的数据传输方式。

相比其它文献中的通用DMA,本设计中的专用DMA资源占用更小,而时钟频率和峰值传输速率更高,能够以较小的面积开销,更快速地实现密码算法IP核与SoC片上存储之间的数据传输。

而为了验证整个接口的灵活性和高效性,本文基于Xilinx Virtex-7 FPGA,搭建了一个SoC验证平台,如图13所示。

图13 FPGA验证平台

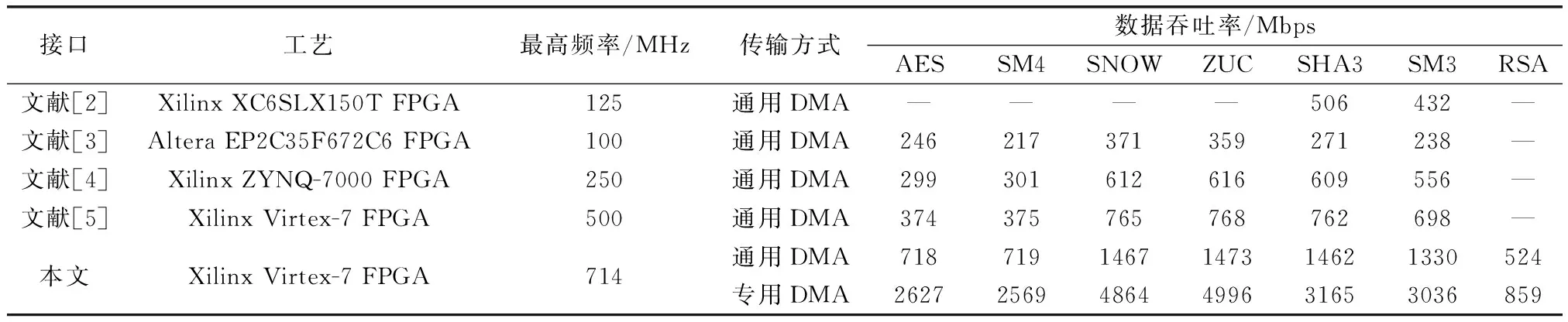

在验证平台上,本文先后选取了几种典型的密码算法IP核,在搭建好的SoC验证平台中,采用通用接口将多种密码算法IP核集成到SoC中,并进行了数据吞吐率测试对比,结果见表6。

表6 算法IP核数据吞吐率测试对比

实验结果表明,在功能方面,相比文献[2-5],本文中的通用接口模型,由于采用了通用数据通信协议和可编程电路结构,功能更加完善,能够根据实际需求适配不同算法IP核,实现分组、序列、杂凑和公钥密码算法IP核到AHB总线的挂载和数据通信,进而完成密码SoC对不同类型密码算法IP核的统一管理和调度控制。

在性能方面,相比文献[2-5],本文中的通用接口模型,主要有三方面优势:一是提取了大量共性逻辑,接口配置信息量少;二是通过电路优化,实现了更高的时钟频率;三是内部集成了针对密码运算数据传输设计的专用DMA,能够独立高效完成密码算法IP核与片上存储间的数据传输,进而大幅度提升了密码算法IP核的数据吞吐率。

相比采用通用DMA进行数据传输,本文中的通用接口在内部专用DMA主动进行数据传输,可将AES、SM4、SNOW、ZUC、SHA3、SM3和RSA算法的数据吞吐率分别提高266%、258%、232%、239%、116%、117%和64%。

5 结束语

本文通过分析密码SoC中的密码应用需求,在充分考虑不同类型密码算法IP核硬件实现差异性的同时,提取出大量共性逻辑,完成了一种统一的算法IP核通用接口模型和可编程电路结构设计。测试结果表明,该接口模型和可编程逻辑电路,能够快速适配不同类型算法IP核,实现算法IP核与AHB总线的高速数据通信,大幅度提高密码SoC实现分组、序列、杂凑密码算法和公钥数据加密的数据吞吐率,在密码SoC设计中,对提高系统灵活性、高效性,缩短设计周期,具有重要意义。下一步,可在此模型和可编程电路的基础上,进一步扩展功能,使其能够支持密码算法IP核以外的其它功能模块。