星载同步NAND FLASH存储控制器设计

2021-11-02张贤玉周昌义安军社

张贤玉,周昌义,安军社

(1.中国科学院国家空间科学中心 复杂航天系统电子信息技术重点实验室,北京 100190; 2.中国科学院大学 计算机科学与技术学院,北京 100190)

0 引 言

星载存储系统是空间科学研究中的关键设备,用来存储及传输宝贵的空间科学实验数据[1]。由于探测任务的种类不断丰富,实验产生的数据量越来越庞大,需要对星载存储系统的容量及吞吐率进行提升。从90年代初到现在,星载存储系统的容量由Mb提升至现在的Tb级别,尽管吞吐率也由最初的Mbps提升至现在的Gbps级别[2],但显然吞吐率的提升速度远远不及容量的提升速度,为了满足海量空间科学数据对及时有效存储的需求,需进一步提升星载存储系统的吞吐率。

随着半导体技术的进步,开始有研究者在一些场景中使用支持更高工作频率的同步NAND FLASH提升存储系统的吞吐率[3,4],目前在嫦娥二号、暗物质粒子探测卫星、实践10号、创新3A等卫星系统中仍采用的是仅支持异步数据接口的NAND FLASH[2,5],系统存储速率受限。因此本文将支持同步数据接口的SLC型NAND FLASH应用于星载存储系统,通过对星载存储系统吞吐率影响因素的分析,进一步提出了在存储阵列中引入八级流水及并行扩展技术的方案,并结合星载任务的特点对该高速同步NAND FLASH存储控制器的软硬件进行了功能模块化、接口标准化的设计,同时考虑了系统的灵活性及高速设计的可靠性问题。

1 星载存储系统吞吐率

1.1 影响因素

设f为NAND FLASH数据总线上的传输频率,W为可同时操作的NAND FLASH数据总线的位宽,那么该星载固态存储系统的理论吞吐率R可表示为

R=f×W

(1)

显然星载存储系统的吞吐率将受到f及W的制约。

由NAND FLASH芯片的存储结构[6]及存储原理可知,在存储操作中存在一些等待时间,这将导致存储的效率不能达到100%,即实际的系统吞吐率并不能达到理论值,因此星载固态存储系统的吞吐率还将受到存储操作等待时间的制约。

1.2 提升吞吐率的方法

针对以上星载存储系统吞吐率的影响因素,本设计将从提高NAND FLASH数据总线上的传输频率、增加可同时操作的NAND FLASH数据总线位宽、充分利用操作等待时间3个方面对星载存储系统的吞吐率进行提升。

1.2.1 同步数据接口

传统星载存储系统使用的NAND FLASH仅支持异步数据接口时序模式[5],最高工作频率50 MHz,考虑可靠性和降额等因素,实际频率一般设计为32 MHz,此时NAND FLASH数据总线上的传输频率为32 MHz,数据总线位宽为8 bits时的理论吞吐率为256 Mbps。

本设计采用Micron公司SLC型NAND FLASH存储芯片MT29F256G08AUCABH3-10ITZ,该芯片既支持异步数据接口模式,也支持同步数据接口模式,同步数据接口时序模式5工作频率可达100 MHz[7],考虑可靠性和降额,将实际频率设计为64 MHz,又由于数据在时钟双沿传输,NAND FLASH数据总线上的传输频率可达128 MHz,数据总线位宽为8 bits时的理论吞吐率可达1 Gbps,为传统星载存储的4倍。

1.2.2 并行扩展

在单板上对多片NAND FLASH的数据总线进行并行扩展,能够增加可同时操作的数据总线位宽,使系统吞吐率得到成倍的提升。在本设计中,将N片数据总线位宽为8 bits的NAND FLASH控制总线、状态总线互联,数据总线并行扩展为N×8 bits后,理论吞吐率可达N×1 Gbps。

由于FPGA引脚资源及PCB板面积有限,单板上的I/O并行位数不可能无限扩展,且一经制板不方便再进行容量及吞吐率的提升;同时由于传统存储架构中合路复接模块与载荷之间耦合程度较高,而不同任务的载荷接口种类及数量不同,需求更改时常常导致大量重复性工作,浪费人力物力。

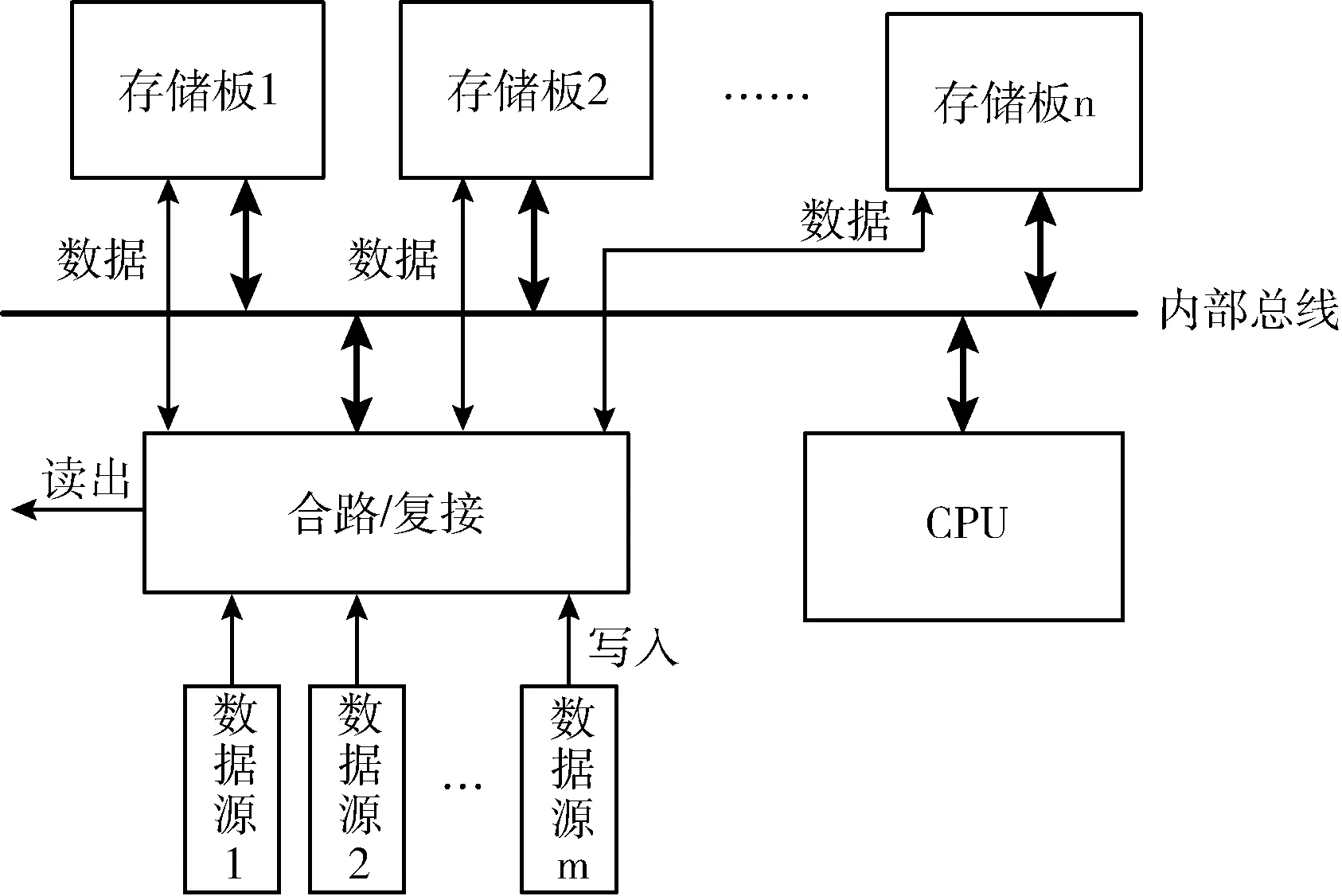

因此可将与载荷直接交互的合路复接模块从存储板中独立出来,并将存储板的接口和功能进行标准化设计,形成一种通用的存储单板。在未来单机内部,结合背板及总线即插即用相关技术[8,9],根据不同任务需求,可进行多存储板间的I/O总线并行扩展,进一步提升系统吞吐率,同时还将有利于系统容量的灵活扩展,其架构如图1所示。

图1 多板并行扩展存储系统架构

1.2.3 八级流水

由于擦除操作可在无存储任务时进行,所以本节将通过计算分析同步NAND FLASH读、写过程中等待时间对吞吐率的影响,并寻找解决方法。

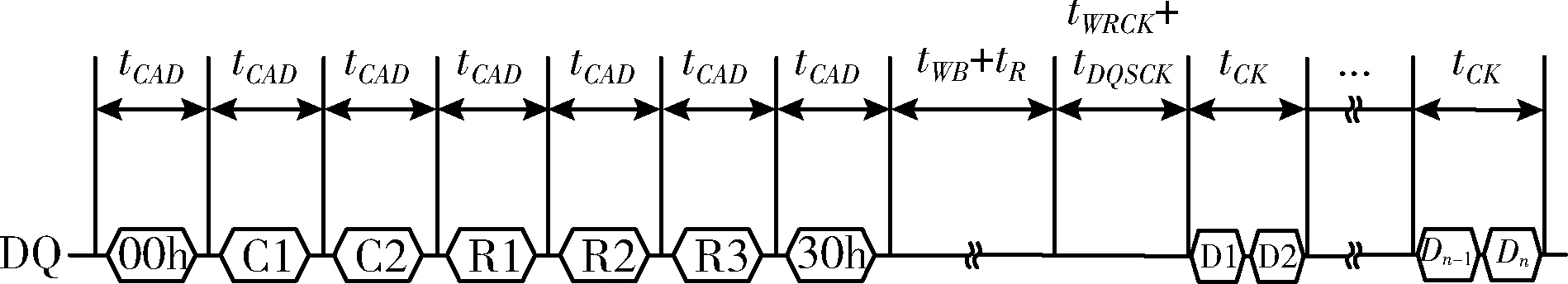

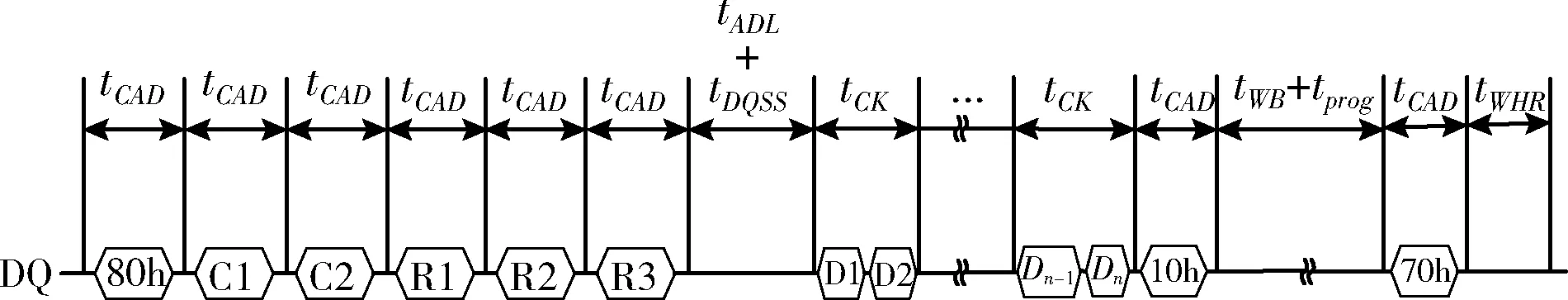

图2为采用同步数据接口的NAND FLASH读操作时序,图中各时序参数见表1,读一页n(Byte)的数据所需时间约为

图2 同步NAND FLASH读操作时序

tread=tr_load+tr_wait

(2)

tr_load为读操作中命令、地址及数据的加载时间

tr_load=tr_command+tr_address+tWRCK+tDQSCK+tr_data

(3)

tr_wait为读操作中的等待时间

tr_wait=tWB+tR

(4)

读操作的效率约为

(5)

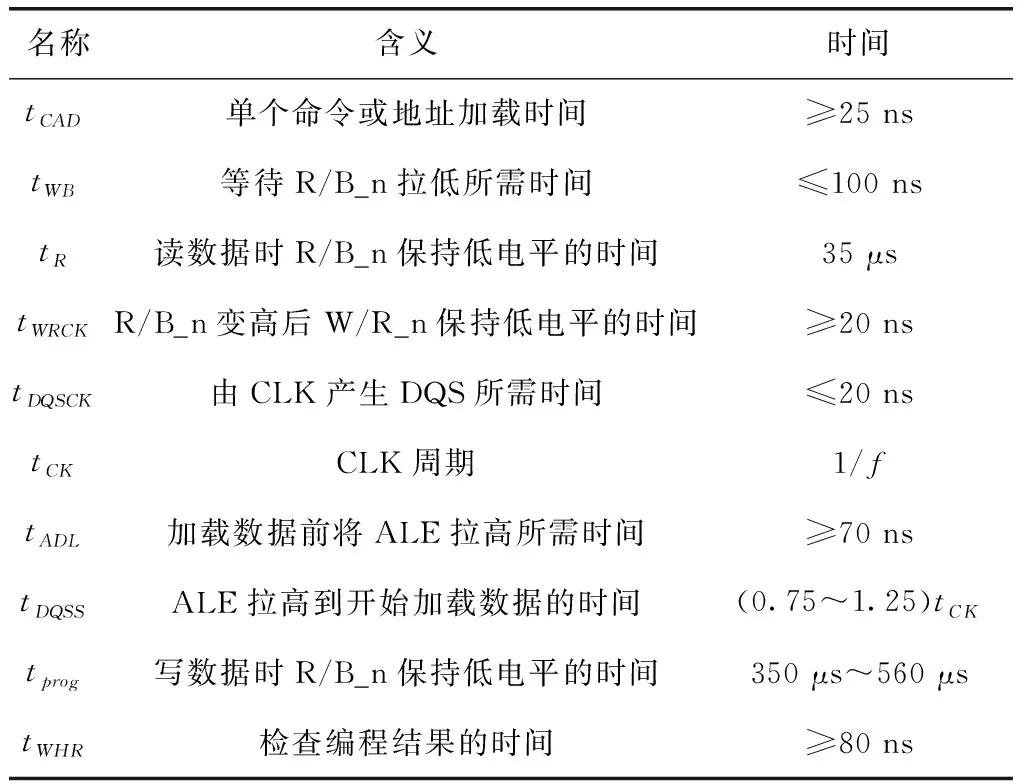

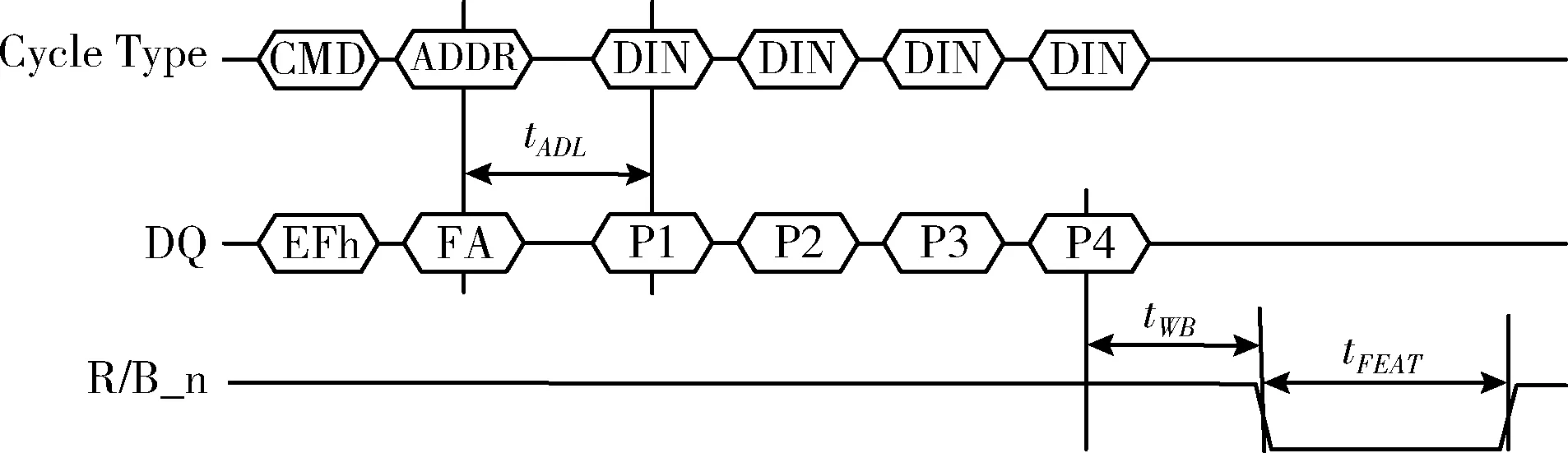

图3为采用同步数据接口的NAND FLASH写操作时序,图中各时序参数见表1,写入一页n(Byte)数据,需要的总时间为

表1 同步NAND FLASH读、写操作时序参数

图3 同步NAND FLASH写操作时序

twrite=tw_load+tw_wait+tw_check

(6)

tw_load为写操作的命令、地址及数据的加载时间

tw_load=tw_command+tw_address+tw_data+tADL+tDQSS

(7)

tw_wait为内部编程等待时间

tw_wait=tWB+tprog

(8)

tw_check为编程结果检查时间

tw_check=tCAD+tWHR

(9)

写操作效率最高约为

(10)

在工作频率为64 MHz时,由式(2)~式(5)可得:读一页数据(8K Bytes)的总时间约为99.32 μs,其中等待时间约为35.10 μs,加载时间约为64.22 μs,此时读操作效率约为64.44%,在读操作中等待时间小于加载时间;由式(6)~式(10)可得:写入一页数据(8K Bytes)的总时间约为420 μs~640 μs,其中内部编程等待时间约为350 μs~560 μs,加载时间约为64.27 μs,此时写操作效率最高仅约为15.24%,在写操作中等待时间远远大于加载时间。

NAND FLASH在等待状态时不响应任何指令,此时其与FPGA之间的数据总线空闲,若等待时间大于加载时间,可通过软硬件的协同合作,利用该等待时间对另外的NAND FLASH进行加载操作,即对存储阵列进行流水操作。

因此,可以在写操作中引入流水操作,又由于写操作中等待时间约为加载时间的6~8倍,那么将流水级数设计为八级,即可充分利用总线空闲时间,使存储系统整体吞吐率接近理论值。

2 星载高速同步存储控制器FPGA逻辑设计

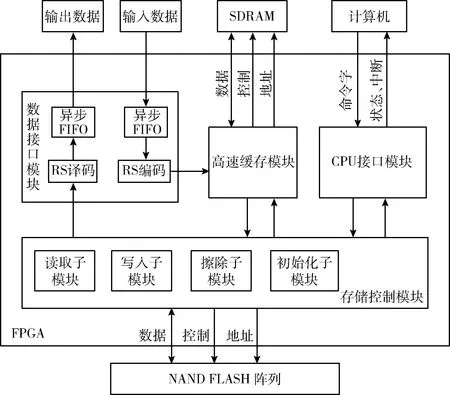

本设计中主控芯片选择了Microsemi公司的SmartFusion2 M2S150TS-1FCG1152,该SOC型FPGA集成了Flash工艺的FPGA及Cortex-M3 ARM硬核,特点是无需外部配置芯片、安全、可靠、低功耗。使用VHDL语言在开发软件Libero SOC中完成对该存储控制器FPGA逻辑功能代码的设计,FPGA逻辑架构如图4所示,对功能进行了模块化的设计,主要包括数据接口模块、高速缓存模块、CPU接口模块、存储控制模块。

图4 FPGA逻辑架构

2.1 数据接口模块

数据接口模块主要实现输入数据的缓存、纠错编码及输出数据的译码、缓存。为了增加系统的可靠性,本设计采用RS编码来防止空间单粒子效应可能对存储数据产生的影响[10],将来自载荷的数据经过RS(256,252)编码后再送入高速缓存SDRAM,从NAND FLASH读出的数据先进行RS译码再送出,其中每252字节可纠正2个字节错误。

2.2 高速缓存模块

高速缓存模块主要功能是为采用了八级流水及并行扩展的存储阵列提供不间断的数据流,保证数据加载的连续与高速。在并行扩展后,每级写操作的单位由一页扩展为N页,记为一“簇”,为了保证写操作的效率,需要提前准备好8簇数据,本设计采用SDRAM作为高速缓存[11],该模块完成SDRAM的初始化、预充电、读写、刷新等操作。

2.3 CPU接口模块

CPU接口模块主要完成FPGA与CPU之间的通信,负责提供CPU与FPGA的信号接口、命令寄存及译码、中断状态返回、硬件工作状态查询等工作。根据任务需要,由CPU向FPGA发送命令字,该模块进行指令译码提取出指令信息,启动硬件相应操作,在执行过程中对中断信号及硬件状态进行组织并返回给CPU,方便对存储过程的管理。

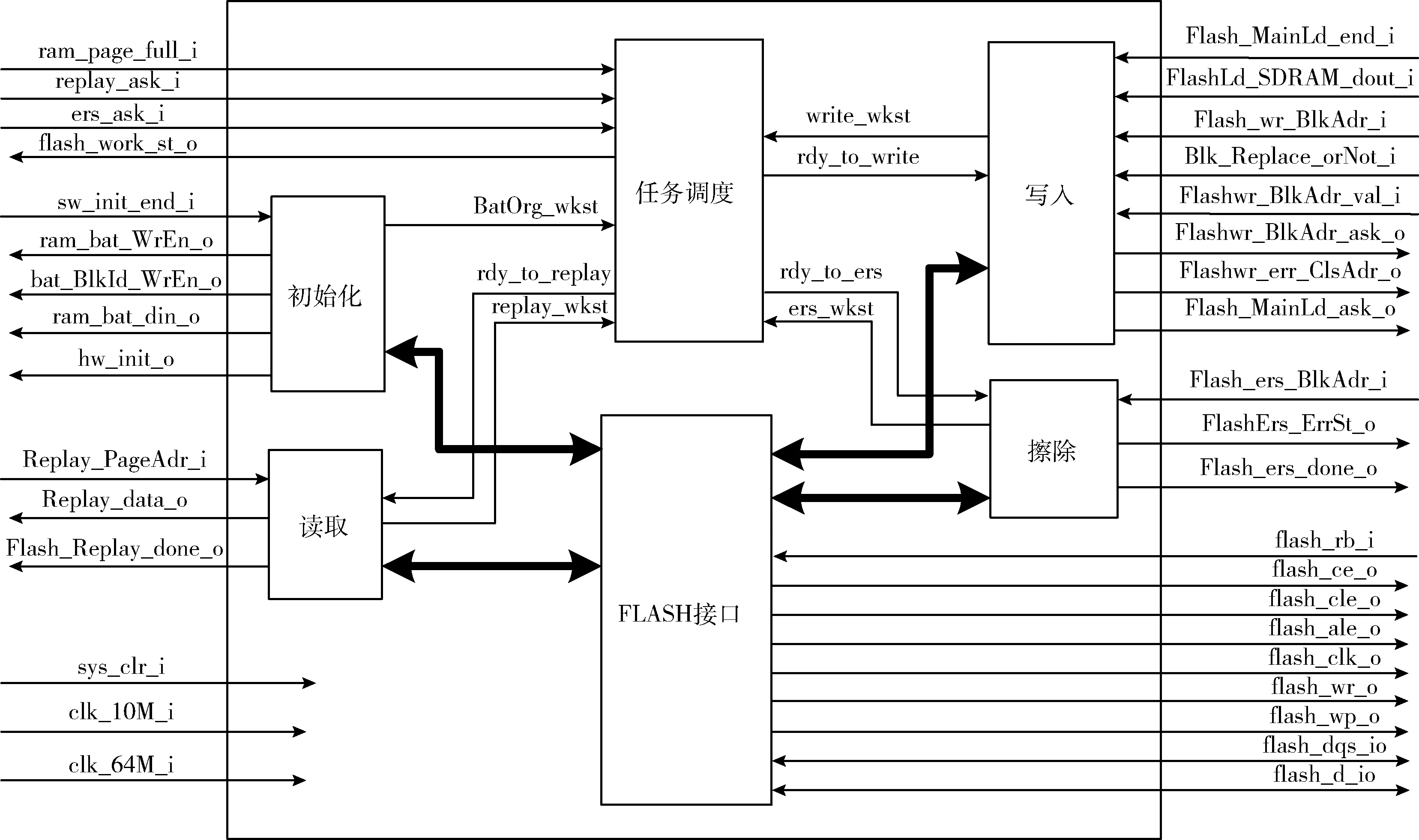

2.4 存储控制模块

存储控制模块是直接与NAND FLASH存储阵列进行交互的模块,主要功能是提供FPGA与NAND FLASH之间的信号接口,实现同步存储控制时序逻辑,并按照优先级顺序完成各存储操作任务,内部又包括初始化、写入、读取、擦除4个子模块,存储控制模块的接口及内部结构如图5所示。

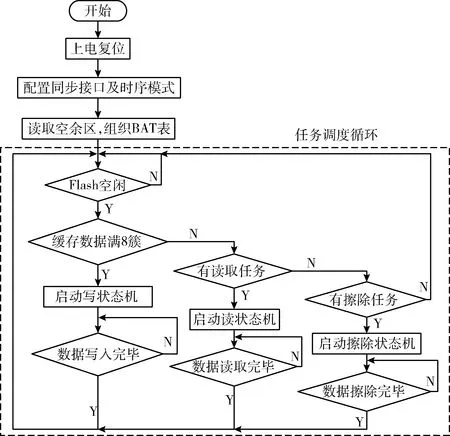

图5 存储控制模块结构

存储控制模块的操作流程如图6所示,系统上电后首先需要进行“复位”操作,然后通过“Set Feature”操作对NAND FLASH的数据接口及时序模式进行配置,配置完成后读取空余区信息,组织成块分配表(block allocation table,BAT),方便后续对存储区的管理;初始化完毕,系统将进入存储控制任务调度主循环,根据CPU指令及硬件工作状态,在NAND FLASH存储区为空闲状态时,按照优先级顺序依次判断是否进行数据写入、数据读取、数据擦除任务,并启动对应的状态机执行相应的操作。

图6 存储控制模块操作流程

2.4.1 NAND FLASH模式配置

本设计采用的NAND FLASH在上电后默认工作在异步数据接口时序模式0,工作频率仅为10 MHz,因此若要实现高速存储,需通过“Set Feature”操作对NAND FLASH的工作模式进行配置。本设计中使用同步数据接口时序模式5,该模式支持的最大工作频率为100 MHz,考虑可靠性和降额,实际工作频率设计为64 MHz。如图7所示为“Set Feature”操作的时序。

图7 “Set Feature”操作时序

“Set Feature”操作的具体步骤为:

(1)发送命令“EFh”;

(2)发送特性地址(FA):“01h”,启动数据接口及时序模式配置的操作;

(3)发送4个周期的特性参数(P1-P2):“15h-00h-00h-00h”,将数据接口设置为同步数据接口时序模式5的工作模式;

(4)在时间tWB后NAND FLASH的R/B信号将拉低,待再次检测到R/B信号拉高,设置完成。

2.4.2 同步时序逻辑设计

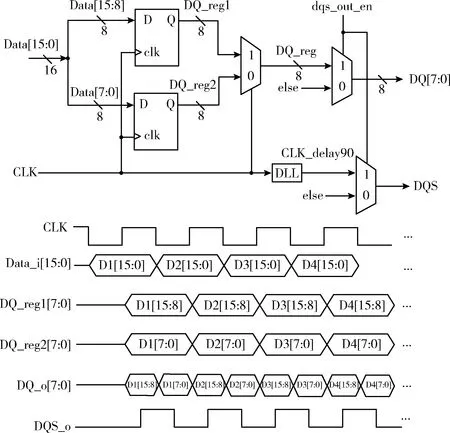

同步NAND FLASH的存储控制逻辑与传统异步NAND FLASH存在区别:异步接口模式下,命令、地址、写入数据由WE_n信号锁存,读出数据由RE_n信号锁存,数据在时钟单沿传输;同步接口模式下,命令、地址由CLK信号锁存,写入数据和读出数据由DQS信号锁存,数据在时钟双沿传输。在同步时序控制逻辑中,如何实现数据的双沿传输与读取是设计的关键。

图8给出了同步写操作中实现在CLK双沿发送数据并保证DQS信号边沿与数据中心对齐的逻辑电路及波形变换过程。NAND FLASH数据线DQ位宽为8 bits,数据在CLK双沿传输,也即一个CLK周期内需要在DQ信号线上传输2组8 bits的数据。为减少跨时钟域的操作,在64 MHz系统时钟下,将16 bits的待写入数据Data先由2个寄存器转换为2组8 bits的数据,再通过多路选择器分别在CLK为1和CLK为0时将Data的高8位和低8位送给DQ,实现数据在时钟双沿的传送。同时为保证发送给NAND FLASH的DQS边沿与数据中心对齐,设计中加入发送门控信号dqs_out_en,在dqs_out_en有效时,令DQS等于由CLK移相90度产生的信号。

图8 实现双沿送数的逻辑电路及波形变换

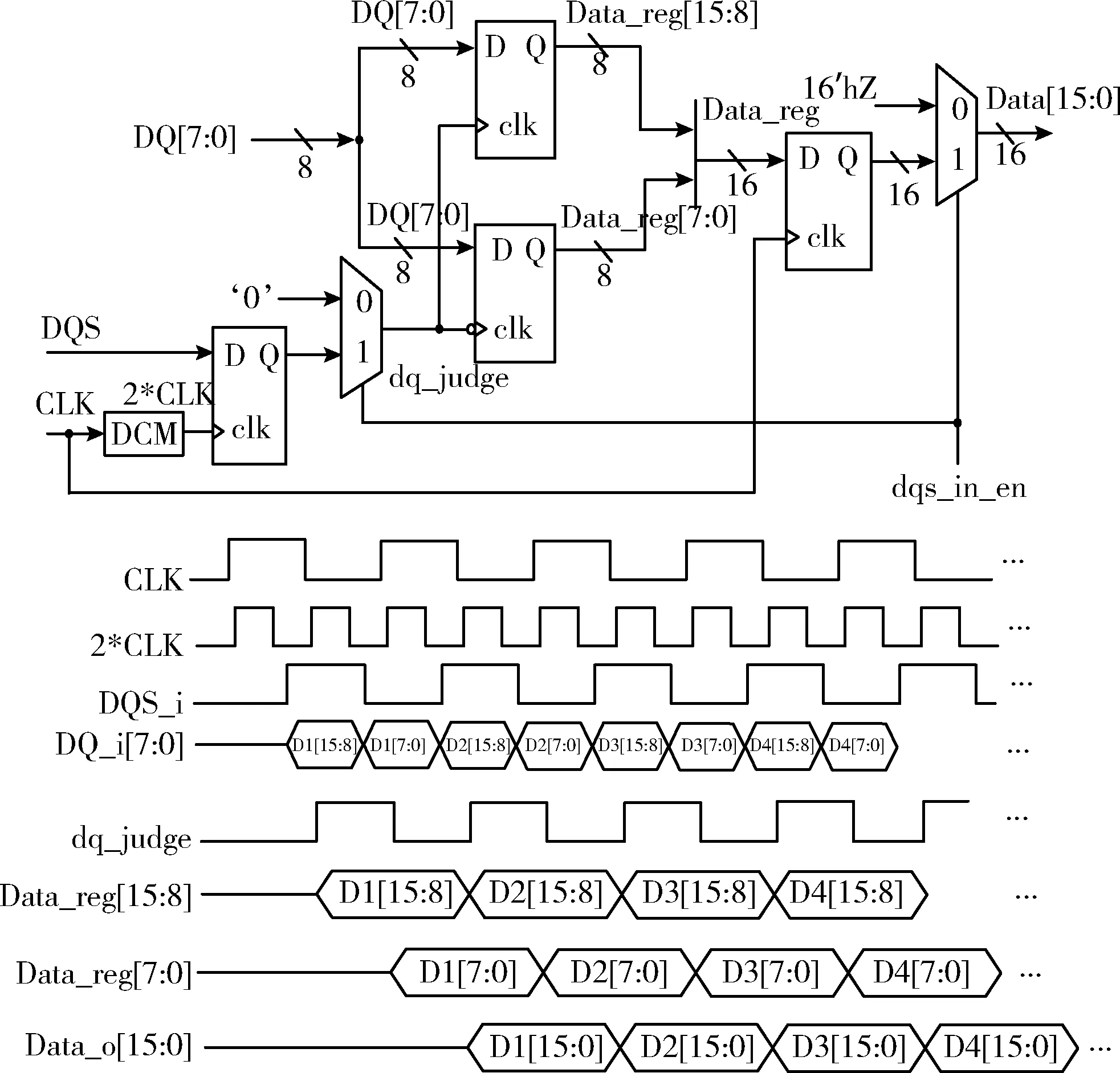

图9给出了在同步读操作中根据DQS信号读取输入数据的逻辑电路及波形变换过程。由于来自NAND FLASH的DQS信号是与数据边沿对齐的,因此直接使用DQS作为采样信号得到的数据并不准确。本设计通过DCM对CLK信号进行2倍频,并令DQS信号通过一个以该信号(2×CLK)上升沿作为触发边沿的寄存器,将产生的新信号作为数据采样信号dq_judge,在dq_judge的上升沿和下降沿对DQ信号采样,并将采到的数据分别送给寄存器Data_reg 的高8位和低8位,最终组成16 bits的回放数据Data。

图9 实现数据读取的逻辑电路及波形变换

2.4.3 八级流水操作

为充分利用操作等待时间,本设计将按照八级流水的方式将数据加载至存储区;同时考虑到读回数据的连续性,读操作将按照写入时的流水顺序及地址将数据读出;为解决地址管理及磨损均衡问题,擦除操作也将按照写入时的流水顺序及地址进行,按照先记录先擦除、后记录后擦除的原则循环使用存储块。限于篇幅,这里仅给出写操作设计过程。

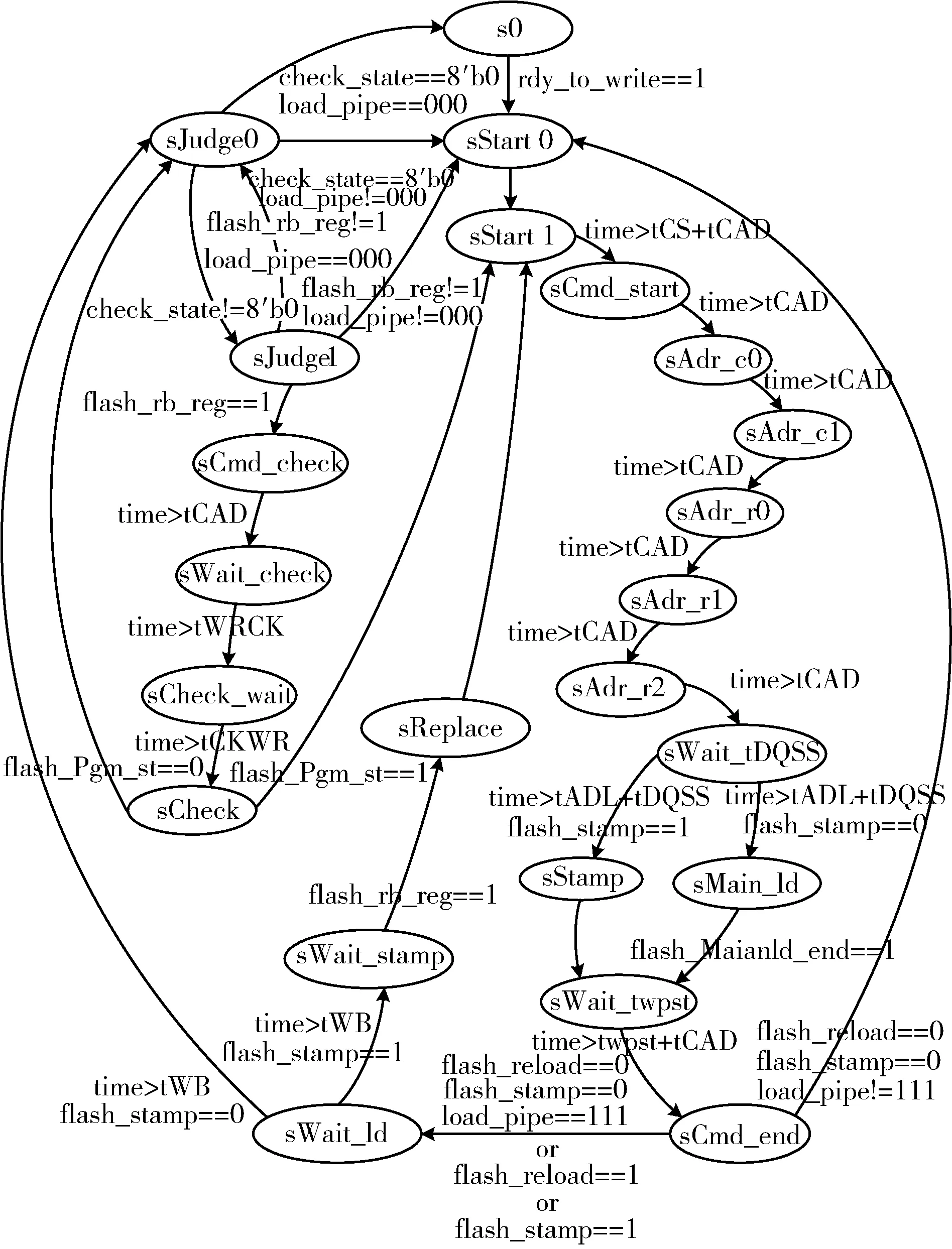

引入八级流水后的写操作状态机如图10所示。

图10 采用八级流水的写操作状态机

s0状态:监控rdy_to_write信号,若高有效则开启状态机,否则保持s0;

在大数据环境下,高校应提高社会主义核心价值观培养策略的科学性和针对性,即利用数据资源建立评价指数模型,结合爱国、敬业、诚信、友善4个指标来衡量大学生的自身价值程度,并借鉴统计学知识,完善评价体系,建立动态分析,为学校和大学生提供更准确的认识和分析数据,提高教育培养策略的实践效果。

sStart0状态:判断当前写入地址是否为本块第一页,若是则锁存该块地址并发送“地址申请”信号给CPU,以保证在本块写满前硬件可以收到下一块的地址,保持系统工作的连续高速;

sCmd_start状态:发送写命令“80h”;

sAdr_c0~sAdr_r2状态:根据是正常写操作还是标记出错块操作,向NAND FLASH发送相应5个周期的待写入页地址;

sWait_tDQSS状态:判断若为正常写操作则转到sMain_ld,若是标记出错块操作则转到sStamp;

sMain_ld状态:向NAND FLASH加载待写入数据;

sStamp状态:往空余区写入标记信息;

sCmd_end状态:发送命令“10h”,若为正常写操作则判断八级流水是否全部加载完毕,未加载完毕将回到sStart0继续下级流水的加载,若为标记出错块操作或全部加载完毕将转到sWait_ld;

sWait_stamp~sReplace状态:判断标记是否完成,向CPU申请“替代块地址”并回到sStart1进行出错页数据的重加载;

sJudge0状态:判断若有未加载完毕的则回到sStarta0继续加载,若有加载完毕需要检测编程状态的则执行sJudge1~sCheck,若全部加载且检测完毕则回到s0;

sJudge1~sCheck状态:检测NAND FLASH内部编程完成情况,若正常写入则转至sJudge0,若写入失败则转至sStart1开启标记出错块操作。

通过采用流水操作令多片NAND FLASH分时复用与FPGA之间数据总线的方法,不仅可在宏观上达到存储效率最大化,使系统吞吐率接近理论值,还可节约FPGA引脚,节省PCB布线空间。

3 星载高速同步存储控制器硬件设计

对星载高速同步存储控制器的硬件进行了功能模块化及接口标准化的设计。

3.1 功能模块设计

硬件结构按照功能可分为电源模块、主控模块、存储模块、总线模块几部分。5 V电压由外部提供,其它电压由电源转换芯片转换得到;主控芯片使用Microsemi的SmartFusion2 FPGA,其外围电路包括时钟、复位、JTAG接口等;存储芯片使用Micron支持同步数据接口的NAND FLASH,SDRAM用于外部高速数据缓存,预留NOR FLASH可用于程序存储,也可用于不经常改写的数据存储;RS422及RS485接口为系统提供内部低速管控串行总线,CAN接口为系统提供外部低速管控总线,SpaceWire及SpaceFibre接口为系统提供高速数据总线;单板采用CPCIe 3U标准板卡尺寸。

3.2 可扩展设计

考虑到通用化、可扩展的需求,硬件设计时预留了多种总线,根据不同需求连接至外部连接器或背板连接器,通过将与外部的信号接口进行标准化定义,方便实现星载存储系统在容量及速率上进一步的灵活扩展。

3.3 可靠性设计

随着工作频率的提高,在PCB设计时需要考虑信号完整性问题。布局时重要电路如主控FPGA、存储芯片优先,然后根据信号流向布局其它器件,保证关键信号线尽可能短,高低频器件分开;布线时遵循关键信号优先、高速差分信号优先、时钟信号优先的原则,将高速差分信号做就近、等长、对称、屏蔽等处理并进行阻抗匹配,为避免线延时的影响,存储阵列并行的信号线也做了等长处理。

4 实验及分析

Modelsim是针对FPGA设计的仿真软件,集成了波形比较、代码覆盖、断点调试等功能,可支持跨平台、跨版本的仿真,编译仿真速度快。本实验使用Modelsim软件,通过编写Testbench产生待测设计所需的激励信号,对设计的时序逻辑及功能进行了仿真验证。

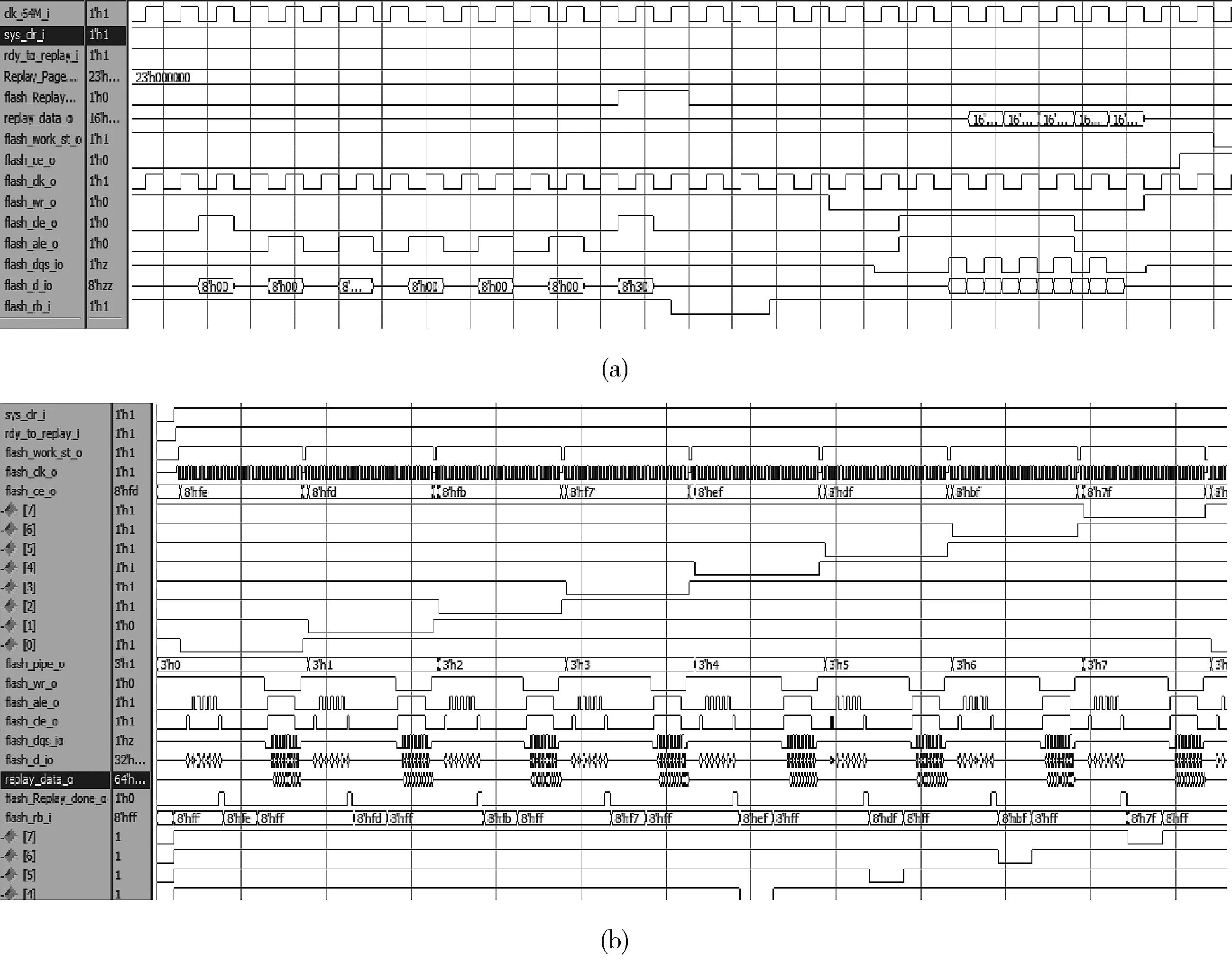

实现双沿送数的逻辑电路仿真波形如图11(a)所示,首先向NAND FLASH加载写命令“80h”,然后加载5个周期的待写入页地址,地址加载完毕将进行数据的加载,flash_dqs_io信号此时由FPGA产生,边沿与数据中心对齐,数据加载完毕发送命令“10h”,随后flash_rb_i信号拉低,NAND FLASH进入内部编程状态。经过并行扩展及引入八级流水后的写操作仿真波形如图11(b)所示,Flashld_SDRAM_dout_i为64 bits位宽的待写入数据,在写入时通过双沿送数逻辑电路转换为在CLK双沿传输的2组32 bits位宽的flash_d_io信号,flash_pipe_o信号指示当前流水级,按照顺序依次完成了八级流水的命令、地址及数据的加载。

图11 写操作仿真波形

实现数据读取的逻辑电路仿真波形如图12(a)所示,首先向NAND FLASH发送读命令“00h”,然后发送5个周期的待读取页地址,再发送命令“30h”,随后等待数据读出,此时flash_dqs_io由NAND FLASH产生,边沿与数据边沿对齐;如图12(b)所示为按照写入时的八级流水顺序及地址将数据读出时的仿真波形,flash_pipe_o信号指示当前流水级,通过读取逻辑电路将与flash_dqs_io信号边沿对齐的2组32 bits位宽的输入数据flash_d_io转换为64 bits 位宽的回放信号replay_data_o。

图12 读操作仿真波形

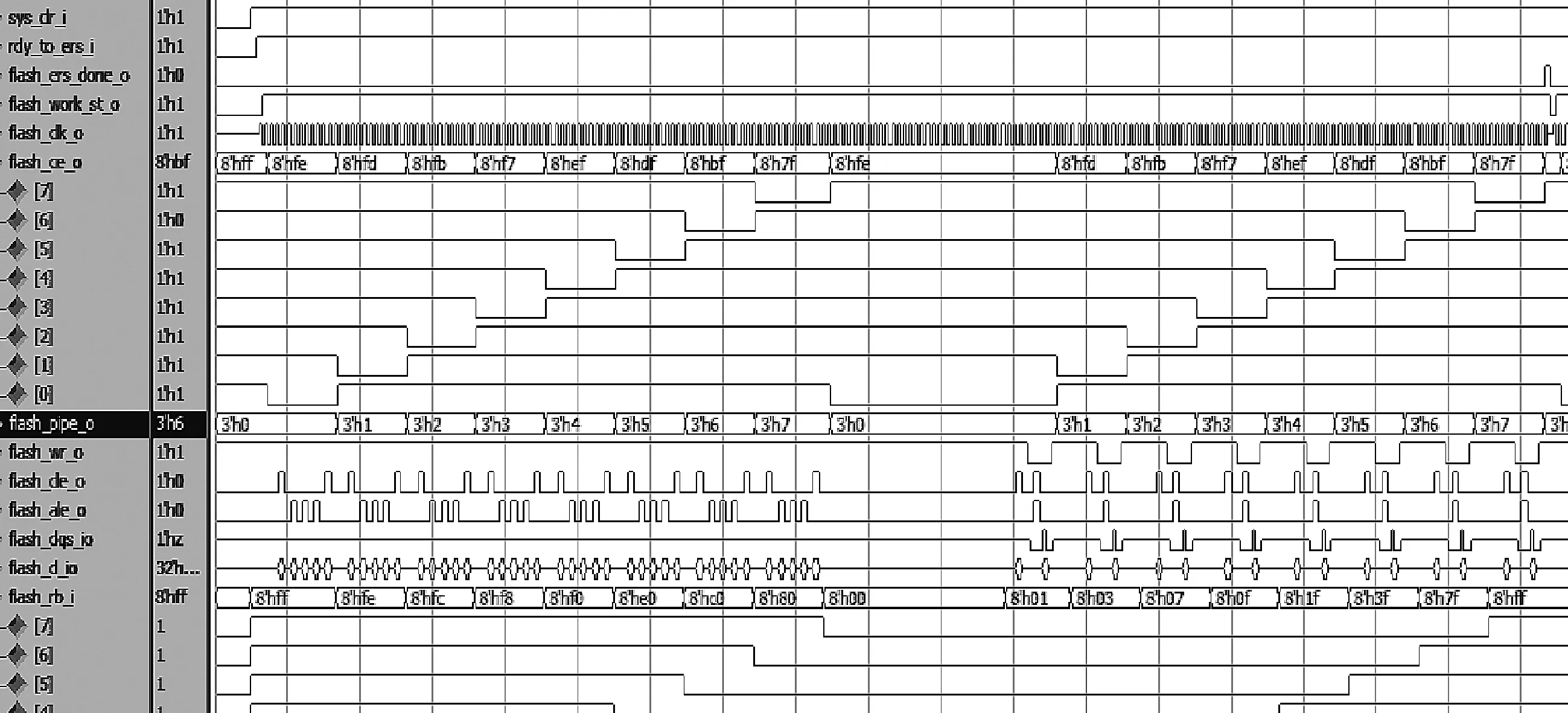

图13为按照写入时的八级流水顺序及地址进行块擦除操作的仿真波形,同样flash_pipe_o信号指示当前流水级,擦除操作首先向NAND FLASH发送命令“60h”,然后发送3个周期的待擦除块地址,地址加载完毕发送命令“D0h”,随后该级NAND FLASH进入擦除状态,继续进行下一级擦除命令及地址的加载,检测到有rb信号拉高,检查该级擦除操作完成情况。

图13 擦除操作仿真波形

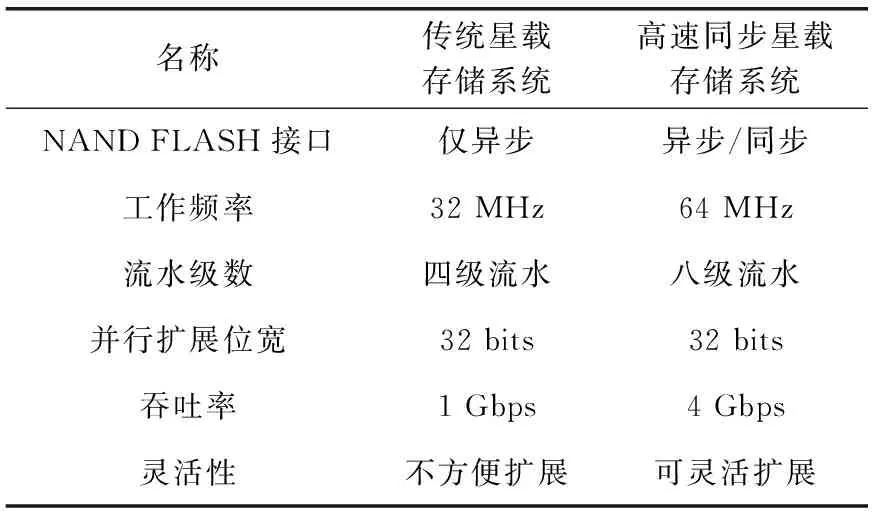

以上结果表明,星载高速同步NAND FLASH存储控制器的功能基本实现。将本设计中的高速同步星载存储系统与传统星载存储系统[5]进行比较,结果见表2,可见在相同并行扩展位宽的情况下,本设计的高速同步星载存储系统吞吐率可达到传统星载存储系统的4倍,且本设计可以通过结合背板总线进行多板并行扩展,能够进一步灵活的提升系统容量及吞吐率。

表2 两种星载存储系统性能对比

5 结束语

本文通过对影响星载存储系统吞吐率的因素进行分析,从提高NAND FLASH数据总线上的传输频率、增加可同时操作的NAND FLASH数据总线位宽、充分利用写操作等待时间3个方面入手,通过将支持同步数据接口的SLC型NAND FLASH应用于星载存储系统、扩展并行操作位宽、引入八级流水充分利用操作中的等待时间等方式,设计了一种高速同步星载NAND FLASH存储控制器。相比于传统星载存储系统,该方案可将吞吐率提升至原来的4倍,同时提出的可扩展架构有利于系统容量及吞吐率的进一步提升,为高速、灵活、小型化星载海量存储系统的研究提供思路,具有一定的实用价值。