面向Verilog HDL的信息化在线仿真平台设计

2021-11-01曹玉丹左冬红

曹玉丹, 左冬红, 朱 明

(华中科技大学电子信息与通信学院,武汉 430074)

0 引 言

随着互联网技术的发展,实施“现代远程教育工程”,形成开放式教育网络,构建终身学习体系,是教育部“面向21 世纪教育振兴行动计划” 的重要内容[1]。各高校将MOOC、BlackBoard、超星学习通等在线教学平台引入常规教学体系,对理论课程的课堂教学起到了很好的辅助作用。实验教学是理工科高等教育教学体系中非常重要的环节,现有在线教学平台只能提供实验教学演示视频学习以及问答式测验,不能构建开放、共享、有效的高等教育信息化实验教学体系。教育部关于一流本科课程建设的实施意见中指出,从2019 年到2021 年将完成1 500 门左右国家虚拟仿真实验教学一流课程认定[2]。

“计算机组成原理与接口技术”是电子信息类专业的核心课程,掌握计算机硬件系统的工作原理且具备数字系统硬件设计能力为该课程的重要教学目标,也是学生学习的难点。如何有效地提升该门课程的教学效果,一直是困扰一线教师的一个重要问题。随着电子设计技术的发展,出现了很多优秀的针对电子电路设计的仿真软件如MultiSim[3]、LogiSim[4]、Proteus[5]、PSpice[6]以及针对硬件描述语言仿真的ModelSim[7]、iverilog[8]、ISim、VCS 等。这些软件为单机版,学生完成电路仿真需具备正确安装并使用软件、设置仿真激励和判断仿真结果的能力。单机版软件无法采集学生在仿真过程中的数据,教师无法得知学生在仿真过程中遇到的问题,不能对教学过程形成反馈[9]。随着科学技术的进步,学生所学课程实验内容越来越复杂,实验教学学时却不断缩减,依赖教师人工检验学生仿真结果是否正确,需要耗费大量的课内教学时间。通过实验验收的形式检查学生对课程知识的掌握情况只能看到学生仿真的最终结果,不能发现学生在仿真过程中出现的问题和错误并加以及时纠正,这易导致学生失去学习的兴趣而直接拷贝他人的代码敷衍完成仿真任务。建设信息化线上实验教学平台是理工科高等教育发展的必然趋势。

1 研究现状

国内外计算机硬件类远程虚拟实验系统研究较早,目前已具备不少成熟的远程实验平台,它们可以分为有真实硬件支撑的远程虚拟实验平台[10]、纯仿真的远程虚拟实验平台以及两者的结合[11-12]。

绝大部分虚拟实验平台建设目标是为学习者提供便捷的实验环境,解决学习者在不具备相应实验环境的情况下也能进行远程实验的问题。它们不具备学习者实验过程数据存储、实验结果自动检验等功能。作为信息化线上实验教学平台要求具备以下功能:①为教师根据课程教学目标定制实验内容;②记录学生实验过程中的行为数据、出错信息以及自动检验实验结果;③对学生实验过程中的行为以及实验结果进行评分。促进教师改进实验教学方法,提高实验教学质量。

随着超大规模集成芯片技术的发展,硬件设计日趋软件化,越来越多场景采用硬件描述语言设计硬件电路,国内越来越多的高校数字电路以及计算机硬件设计等相关课程采用硬件描述语言进行教学[13-14]。基于以上因素,本文设计了一种面向Verilog 硬件描述语言的在线仿真自动检验信息化实验平台。

2 平台设计

本实验平台采用B/S 架构,学生实验时无须另外安装客户端。采用前后端分离的开发模式,前端UI采用Vue框架[15],实现学生、教师的人机交互;后端采用Springboot[16]框架,实现Verilog语言代码的综合、功能仿真以及功能正确性黑盒验证;实验数据的存储采用关系型数据库Mysql。在线仿真实验系统交互流程如图1 所示。主要包含:实验任务布置;实验代码提交及自动仿真验证;实验结果展示;实验成绩生成和实验行为记录等功能模块。

2.1 实验任务布置

实验任务布置模块除接收教师提交的实验任务描述、设计示例代码之外,还需教师提交电路对应的仿真激励文件。仿真激励文件为学生的电路设计提供确定的激励,如时钟信号等。在确定的激励信号作用下,电路的输出端口将输出确定的响应。本系统基于黑盒验证的思想,在教师提供的初始激励文件(原激励文件)中加入波形采集任务,仿真时生成VCD(Value Change Dump)波形文件,将电路正确的VCD波形文件与学生设计输出的波形VCD文件比较,实现电路设计正确性的自动检验。系统激励文件生成方法如图2 所示。

图2 系统激励文件自动生成方法

以半加器电路设计为例,原激励文件和系统激励文件之间关系见表1。

表1 原激励文件与系统激励文件之间的关系

其中verilog硬件描述语言的系统任务$dumpfile(“wave.vcd”)用于生成wave.vcd 波形文件,而$dumpvars(0,adder_sim)用来采集adder_sim级别为0 的端口信号变化信息,即In1,In2,Out端口信号变化信息。添加波形采集任务的系统激励文件在仿真后生成波形VCD 文件wave.vcd,并记录输入、输出信号的变化关系,用于后续电路设计正确性检验和波形的可视化。

2.2 实验代码自动仿真验证

系统的仿真功能通过iverilog软件实现,iverilog是一个支持全平台的开源Verilog 仿真软件,在Linux 系统中使用非常方便。通过以下命令在服务器中安装iverilog:$yum install iverilog。安装iverilog 时自动安装VVP,VVP 根据iverilog 生成的可执行文件生成VCD波形文件。

功能仿真及正确性检验需要用到激励文件、电路设计源文件和波形VCD 文件。源文件即学生提交的Verilog代码,激励文件为源文件提供激励,同时生成VCD文件。

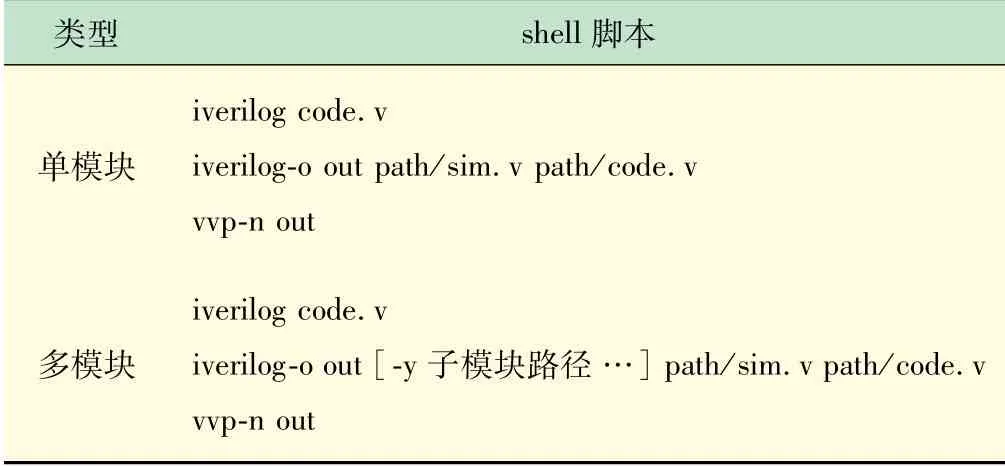

学生提交设计源文件之后,系统将学生代码存储到服务器文件系统指定文件目录下,并根据模块类型生成仿真shell脚本。Verilog代码仿真shell脚本命令格式见表2。

表2 Verilog代码仿真完整shell脚本命令格式

其中:sim.v 为激励文件;code.v 为学生提交的源文件;path为相应文件所在路径。

iverilog code.v命令对电路设计源文件进行编译完成语法检验。iverilog-o out sim.v code.v 通过激励文件为源文件提供激励,生成可执行文件,参数-o 指定了可执行文件的名字。vvp-n out 对可执行文件out

进行分析生成波形VCD 文件。通过Java Runtime 类提供的getRuntime()方法获取当前JVM的运行时环境,通过Runtime.getRuntime().exec()方法创建仿真进程调用动态生成的shell 脚本,同时创建2 个线程,分别读取仿真子进程的标准输出流和错误流,避免因缓冲区满而导致子进程阻塞产生死锁。使用waitFor()方法等待iverilog 仿真进程执行结束。仿真脚本正常退出后,通过进程的标准错误流中的信息判断仿真代码是否编译报错。若标准错误流为空,编译通过。若代码无语法错误,进一步判断仿真波形是否正确。否则代码编译报错,将报错信息返回到学生仿真界面。Verilog在线仿真流程如图3 所示。

图3 Verilog在线仿真流程

2.3 实验结果展示模块

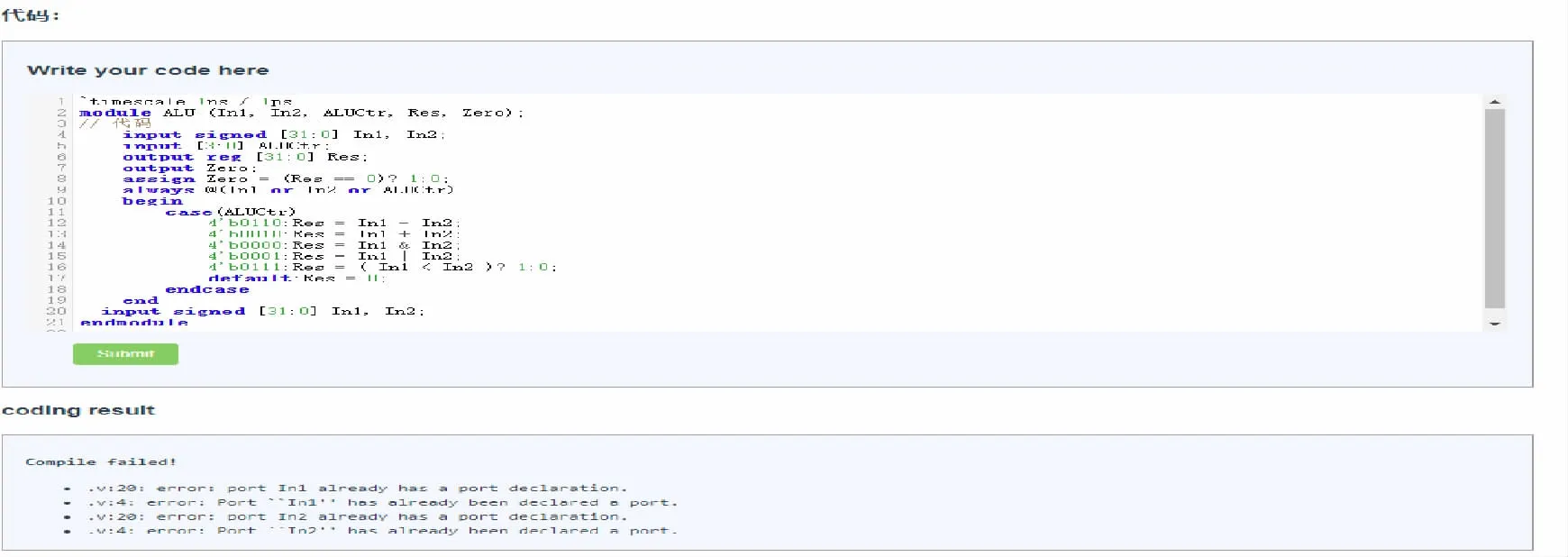

实验结果的呈现包含3 种情况:①设计代码存在语法错误;②无语法错误但存在功能错误;③既无语法错误也无功能错误。

若存在语法错误,直接将编译语法错误通过web界面显示给学生,如图4 所示,显示存在错误的代码所在行行号以及错误原因。

图4 编译报错

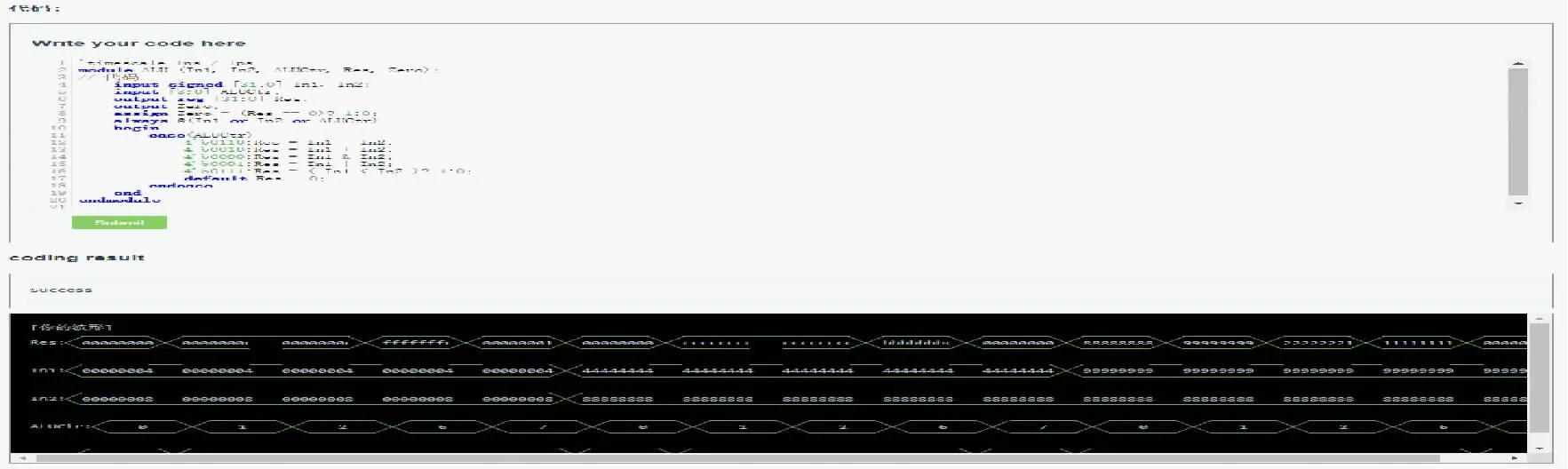

学生代码编译通过后,前端接收到服务器返回的波形数据WaveData,根据WaveData 渲染波形界面。在渲染之前先将WaveData 中的端口信号分别存储到数组中,通过Vue框架的V-for指令结合Flex弹性布局对波形信号数组中的波形数据进行水平方向循环渲染。每一个信号的每一个周期都是一个基本单元波形组件。基本单元波形组件由HTML 的span 标签以及前后2 个旋转135°伪元素共同构成,通过组合显示span及伪元素的不同边,完成多位宽波形信号基本单元组件的构建。

波形比对发现错误时,显示如图5 所示波形。此时通过对比的方式显示正确波形以及学生代码存在错误的波形,且错误之处除采用文字提醒之外,在波形图中采用红色高亮显示,并将输入\输出信号的值显示在波形图中。

图5 电路设计逻辑有误

若功能仿真成功,则仅显示正确波形如图6 所示。

图6 功能仿真成功

2.4 实验成绩生成模块

功能仿真实验时间截止时,系统自动计算学生的分数。教师在发布实验时可分别设置功能仿真实验中学生代码编译通过且波形正确、编译通过但波形不正确、编译不通过3 种情况的分数。根据教师设置的得分规则以及每一个实验模块的分值权重,对各个模块的分数进行带权累加,生成学生仿真实验总分数。

2.5 信息化实验过程数据收集

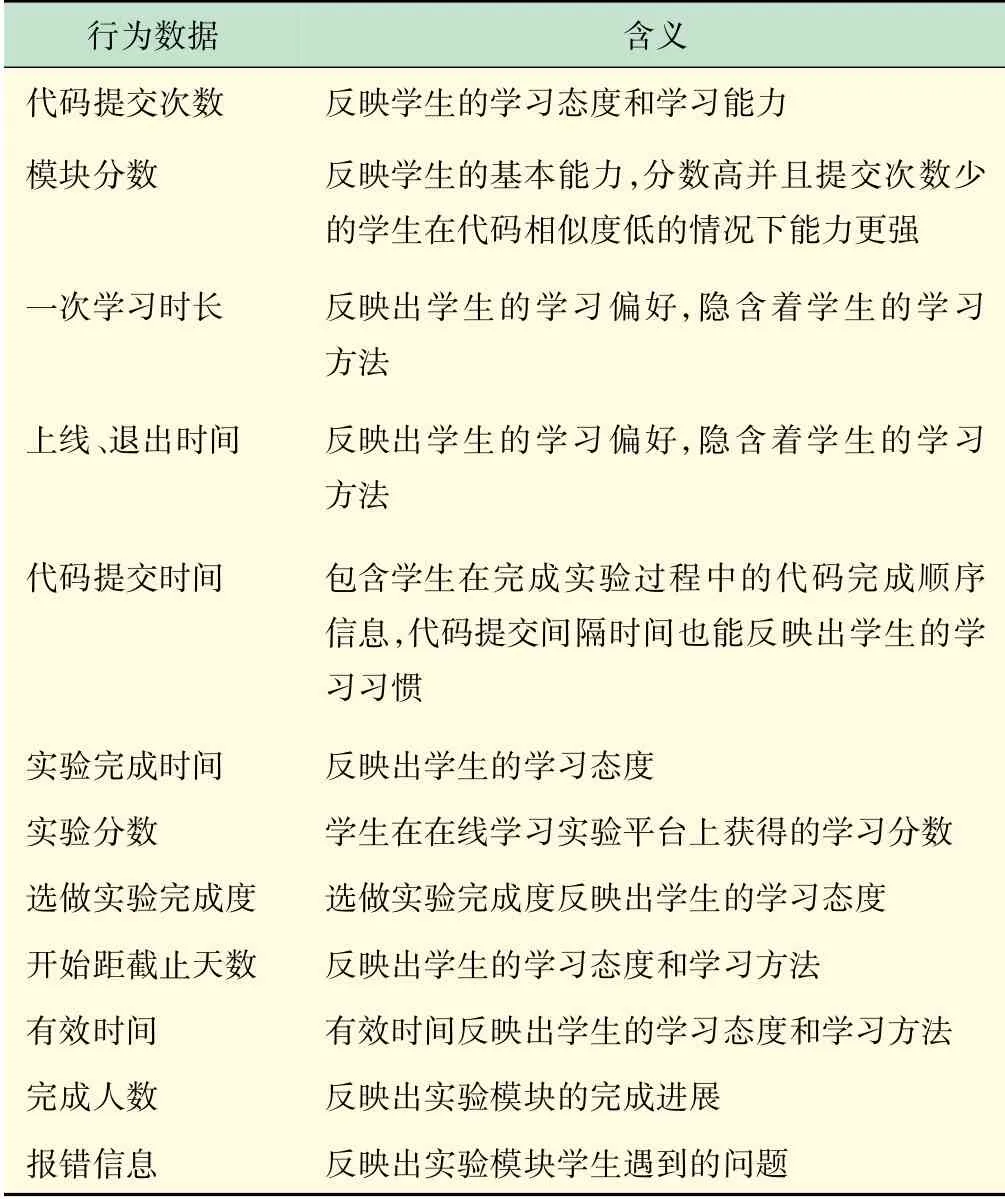

学生使用本系统完成功能仿真实验时,会进行很多操作,如登录系统、查看实验内容、提交实验代码等。本系统拦截学生实验操作的HTTP请求以及操作产生的中间数据,如代码信息、报错信息等,将这些数据的类型和内容持久化到数据库中。结合教师教学经验,将这些数据总结为如表3 所示实验数据行为指标:学生实验进展、实验行为偏好、实验遇到的问题等。平台通过对上述数据的收集以及Echart 前端可视化框架向教师实时展示实验中每一个模块每一个学生的实验完成情况,代码报错信息等,便于教师根据学生实验情况进行有针对性的教学。

表3 实验行为数据类型

3 平台应用

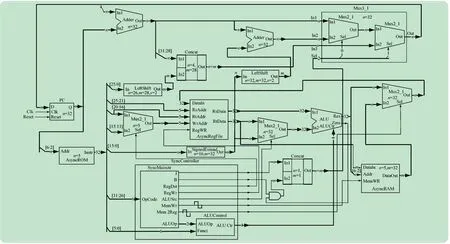

学院2018 级本科生(330 人)在开学初补做“计算机组成原理与接口技术”实验课中的微处理器设计(见图7),实验采用了该实验平台,有效缓解了实验课补课期间课内学时紧张以及实验室冲突的问题,并保证了实验教学效果。平台于8 月底上线,在9 月1 日~10 月4 日期间稳定运行,期间总宕机时长少于24h,最大限度地减少了实验平台对学生在线学习行为数据的影响,保证了数据的可靠性。实验平台共采集到316 个学生的实验数据。包括《微处理器设计》实验中的16 个必做模块,5 个选做模块,3 万多次提交代码信息、5 万多条报错信息以及其他数据。

图7 微处理器电路框图

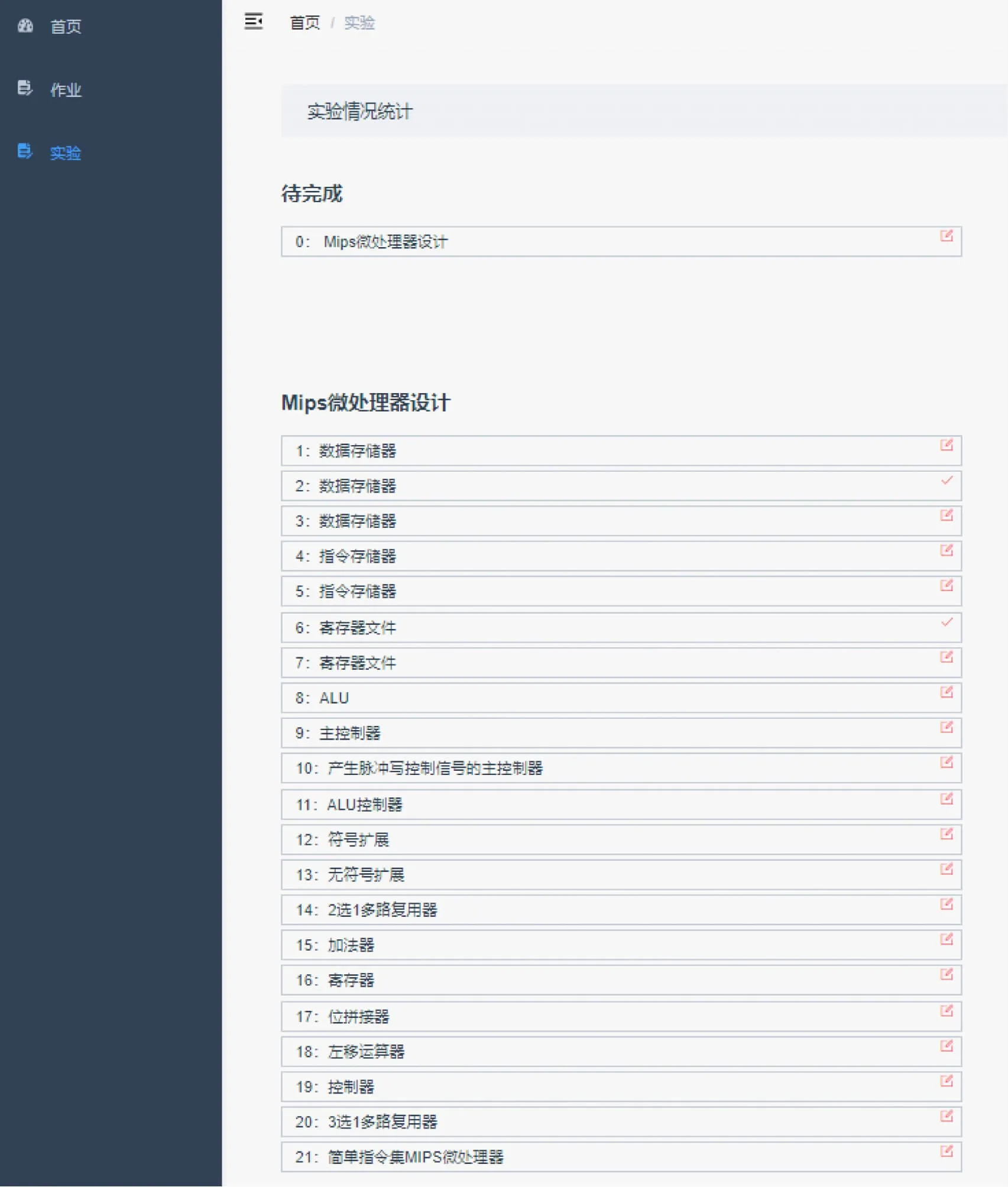

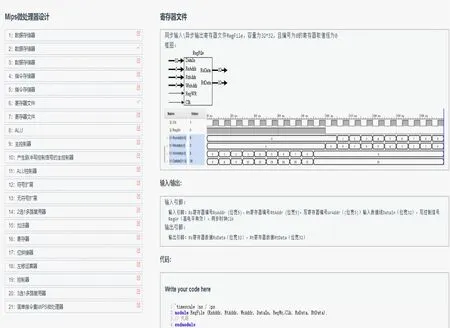

《微处理器设计》实验主界面如图8 所示,子模块详情描述界面示例如图9 所示。

图8 《微处理器设计》实验主界面

图9 子模块详情描述界面

根据平台记录的数据,分析平台记录数据所表征的实验掌握程度与课程期末成绩的相关性,得到如表4 所示结果,这说明:①平台实验分数表征的实验掌握程度能够在一定程度上预测课程的期末成绩;②开始实验距截止日期的天数与期末成绩达到了0.503 的极显著正相关性,即开始实验越早,期末成绩越高;③完成实验距截止日期的天数与期末成绩达到了0.404 的极显著正相关性,即完成实验越早的学生,期末成绩越高,而快到实验验收截止时间临时抱佛脚完成实验的学生分数较低。

4 结 语

本文将传统面向Verilog 硬件描述语言硬件电路功能仿真单机软件部署到了互联网云平台,为学生提供了在线仿真平台,同时也为教师了解学生实验过程行为提供了实验数据收集平台。它具有以下优点:①

学生无须安装任何软件即可随时随地在PC 端或移动端进行仿真代码提交、仿真结果查看。②合理设置仿真结果后,采用自动仿真结果正确性检验以及实验行为综合评分手段,实现了更加科学和公平的仿真实验验收以及实验效果评分。③无须教师参与,学生便可实时查看仿真结果,并根据可视化的波形对电路逻辑功能进行分析,有助于提高学生参与实验的积极性和热情。④学生实验行为数据的收集和分析为教师定位教学难点、改进教学方法、提高教学质量提供了参考依据。

该平台首次应用于计算机组成原理与接口技术实验课程的微处理器设计实验,它还可应用于数字电路课程基于硬件描述语言设计电路的实验,并且在添加一定的身份验证功能之后可以应用于基于硬件描述语言的实验操作考试中。借助其自动仿真验证以及多元化的数据记录和分析功能,可以减轻教师的实验操作类考试监考和验收压力。

实践告诉我们,伟大事业都成于实干。新时代是奋斗者的时代。新时代是在奋斗中成就伟业、造就人才的时代。我们要激励更多科学大家、领军人才、青年才俊和创新团队勇立潮头、锐意进取,以实干创造新业绩,在推进伟大事业中实现人生价值,不断为实现中华民族伟大复兴的中国梦奠定更为坚实的基础、作出新的更大的贡献。

——2019 年2 月20 日,习近平在会见探月工程嫦娥四号任务参研参试人员代表时强调