基于Zynq的SDI视频图像分割系统 *

2021-10-26王炜琛涂海洋王伟明赵晓博

王炜琛,涂海洋,王伟明,赵晓博

(1.石家庄铁道大学电气与电子工程学院,河北 石家庄 050043;2.空装北京军代局驻石家庄地区军代室,河北 石家庄050000)

1 引言

视频图像分割是安全监控、3D视觉、全景影像和计算成像等视频图像系统中不可或缺的技术。随着人们对视觉体验的要求越来越高,传统的PAL/NTSC(Phase Alternate/National Television Standards Committee)等低分辨率模拟视频图像格式在画质、帧率和传输速度上均难以满足需求,因此研制数字视频图像分割器具有较强的迫切性[1]。串行数字接口SDI(Serial Digitial Interface)技术作为数字视频图像的典型代表,20世纪80年代由美国的电影与电视工程师协会SMPTE(the Society of Motion Picture and Television Engineers)制定,以一根同轴电缆通过数字化的方式处理和传输音视频图像数据。SDI技术分为SD-SDI、HD-SDI、3G-SDI共3种不同的标准,有着不同的视频图像以及显示格式。SDI主要应用在广播电视行业,具有传输速度快、抗干扰能力强、物理接口简单、即插即用和远距离传输的优点[1,2]。

Figure 1 Block diagram of TW6874 application图1 TW6874应用框图

目前,多数的设计是将各路视频图像信号转换成数字视频图像信号,最后按照数字视频图像的数据格式,将4路视频图像合成1路编码输出,以实现4路视频图像分割。图像的提取、存储等都在单片FPGA内实现[3,4]。这种系统设计的优点是提高了系统的集成度,但所有的模块都是利用Verilog 进行逻辑设计,比较复杂[4]。针对以上问题,本文设计并实现了一种在XILINX Zynq的ARM+FPGA异构平台上,利用串行高清视频图像解码芯片实现视频图像分割的系统。相比较经典的FPGA,Zynq系列最大的特点是将处理系统PS(Processing System)和可编程资源PL(Programmable Logic)分离开来,固化了PS系统,提高了系统资源利用率,利用软硬件协同设计,灵活方便,且利用了IP核占用芯片面积小、运行速度快、功耗低等特点,使整个系统的运行速度得到提高,功耗降低[5 - 8]。此平台允许多路SDI的视频图像输入,并将其合成1路SDI视频图像输出,为进一步构建多路数字视频图像并行处理平台提供了可扩展架构。

2 SDI转BT.1120

本文系统的视频图像输入由TW6874 SDI视频图像解码芯片产生。TW6874具有4个独立的SDI视频图像接收通道,4个SDI数字相机通过75 Ω线缆连接至各个通道的SMA(SubMiniature version A )输入端子。每个通道由自适应均衡器、时钟数据恢复和VC-2解压缩引擎组成。图1所示为TW6874的应用框图。

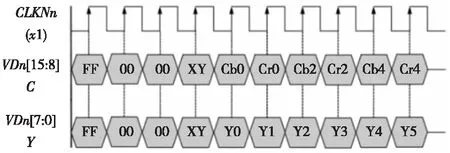

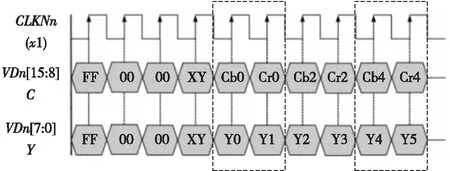

TW6874的视频图像输出格式为HD-SDI BT.1120或SD-SDI BT.656。本文系统采用的是HD-SDI BT.1120格式。HD-SDI BT.1120包含16 bit与8 bit 2种模式,为了便于进行数据传输以及数据编码,本文系统采用HD-SDI BT.1120的16 bit模式,图2所示为其时序图。

Figure 2 BT.1120 timing图2 BT.1120时序图

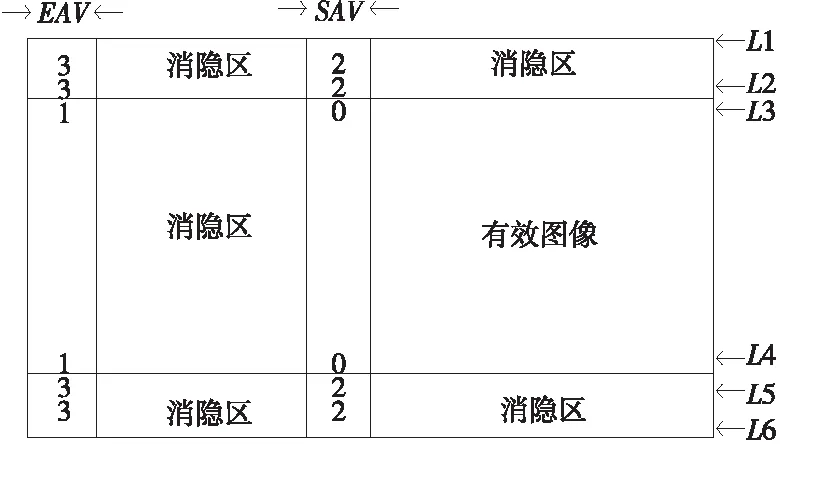

数据流的低8位为Y分量,数据流的高8位为C分量。图3所示为逐行扫描模式下的BT.1120协议,一幅图像包含消隐区和有效数据区,其中EAV、SAV(F、V、H)为图像定时基准码[9,10]。表1为L1~L6所代表的含义及其所对应的起始行号[9,10]。

Figure 3 BT.1120 format图3 BT.1120格式

符号定义起始行号有效行数目1 080L1一帧的首行1L2数字帧消隐首行41L3有效图像首行42L4有效图像末行1 121L5数字帧消隐末行1 122L6一帧的末行1 125

3 SMPTE SDI IP核

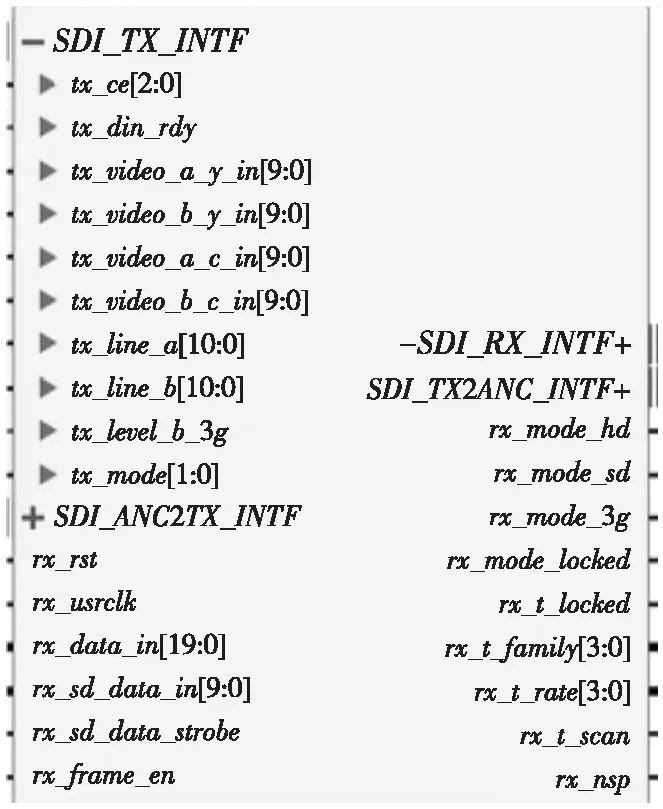

本文系统的SDI高清视频图像输出模块采用如图4所示的XILINX的SMPTE SDI IP核。

Figure 4 SMPTE SDI IP core图4 SMPTE SDI IP核

IP核接口包括输入和输出2部分,本文系统只利用了此IP核的输出接口,主要是tx_din_rdy,tx_video_a_y_in,tx_video_a_c_in,tx_mode和tx_usrclk这几个信号。其中,tx_din_rdy在SDI模式下必须保持高电平;tx_video_a_y_in与tx_video_a_c_in宽度为10 bit,为数据流Y、C的输入接口;tx_mode是宽度为2 bit的输入端口,代表了输出视频图像的格式。tx_mode为00,表示输出的视频图像格式为HD-SDI;tx_mode为01,表示输出的视频图像格式为SD-SDI;tx_mode为10,表示输出的视频图像格式为3G-SDI;tx_mode为11,表示无效的视频图像格式。tx_usrclk为视频图像输出部分的时钟域。SMPTE SDI IP模式的数据流Y、C分量宽度均为10 bit,而TW6874串行解码芯片产生的数据流Y、C分量宽度均为8 bit。为满足SMPTE SDI IP 核输出模式,将TW6874解码产生的8 bit数据均左移2位[11]。

4 系统设计

4.1 系统硬件

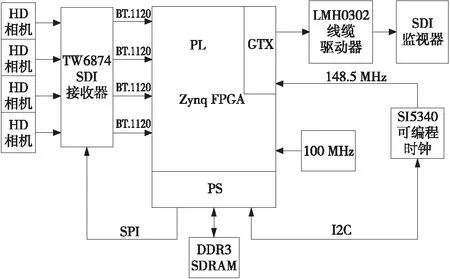

本文系统的硬件主要包括高清视频图像串行解码芯片TW6874、自适应电缆均衡器LMH0302、可编程时钟芯片SI5340、DDR3 SDRAM和XILINX Zynq系列的XZC7035 FPGA。图5所示为系统硬件结构图。

Figure 5 Hardware structure of system图5 系统硬件结构图

XILINX公司的Zynq系列FPGA具有很高的性价比,在工业界已经获得了广泛的应用。该系列资源丰富,特别是集成了双1 GHz ARM Cortex A9硬核,极大地满足了视频图像采集和各种算法处理需求,XILINX同时提供各种视频图像专用IP,可以大大加速开发进度[12,13]。Zynq的PS端配有1 GB的32 bit位宽的DDR3 SDRAM作为数据高速缓存。Zynq的PL端主要完成4路SDI视频图像的行输入、像素抽样,PS端主要通过调度AXI DMA(Direct Memory Access)完成视频图像的三缓存。

由于各通道数据带宽大,数据通常需采用芯片来并行同步处理,才能实现高速运动画面无撕裂、不丢帧、无图像追赶现象的要求。TW6874正好提供了4路SDI视频图像的接入能力。4个高清数字相机经过TW6874解串处理后,将视频图像数据转换为BT.1120数据送入PL端进行处理。处理后的数据写入DDR3 SDRAM进行高速缓存,最后经SMPTE SDI IP核和GTX高速串行发送器输出。其中GTX的参考时钟为27 MHz,是通过FPGA的100 MHz进行分频得到的,通过SI5340可编程时钟输出的148.5 MHz时钟对GTX和SMPTE SDI IP提供恢复时钟。视频图像数据经GTX输出后,由线缆驱动器LMH0302为数字视频图像信号提供驱动能力,通过SMA线缆输出至SDI监视器进行显示。

4.2 视频图像输入设计

首先需对4个1920×1080视频图像的有效数据按照图6所示方式进行抽样并重新排列,裁剪为4个960×540的视频图像数据,然后合并为1个1920×1080的视频图像数据。BT.1120数据的低8位排列规律为:Y0、Y1、Y2、Y3、Y4、Y5、Y6、Y7,高8位的排列规律为Cb0、Cr0、Cb2、Cr2、Cb4、Cr4、Cb6、Cr6,选取Y0、Y1、Cb0、Cr0、Y4、Y5、Cb4、Cr4,舍弃Y2、Y3、Cb2、Cr2、Y6、Y7、Cb6、Cr6。即高8位与低8位均隔2位取2位,将1920×1080视频图像数据抽样为960×540视频图像数据。

Figure 6 Pixel up-sampling process图6 像素的抽样处理

4.3 视频图像输出设计

由于HD-SDI BT.1120数据格式中存在消隐区,即无效数据,因此当4路SDI输入合成1路SDI输出时,本文系统设计了一个“输出框架”,以SDI视频图像格式为基础对视频图像的消隐区数据进行了统一,即根据BT.1120的格式,将视频图像的消隐区数据提前编写好,并将有效数据区分为4块,以便将处理好的有效数据导入。

在视频图像数据的输入侧,通过对SAV图像定时基准码的检测,判断行有效数据的起始,将每行的有效数据导入至AXI4-Stream Data FIFO中,然后利用AXI DMA模块写入至DDR3 SDRAM进行缓存,最后作为“输出框架”中的有效数据区输出至SMPTE SDI IP核。

4.4 视频图像缓存的设计

数据输入侧的时钟与输出侧时钟存在着相位差,是2个不同的时钟域。数据跨时钟域进行传输时,必须要经过缓存。

目前,在Zynq平台上对视频图像缓存一般采用AXI VDMA[14],这种设计大多需要与相机像素输出时序相匹配,灵活性差,资源占用多。本文系统设计了行有效数据缓存模式,利用AXI4-Stream Data FIFO缓存1行有效数据并且产生AXI DMA所需要的握手信号。这种方式灵活,便于拓展。

本文系统中FIFO的写入时钟是37.125 MHz,为了满足30帧/秒输出帧率的要求,DDR3 SDRAM的写入时钟采用150 MHz。

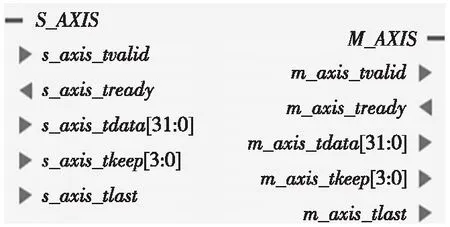

图7所示为AXI4-Stream Data FIFO,它是输入输出接口均为AXIS的数据缓存器,和其他FIFO一样是先进先出形式,可以在跨时钟域的应用中用于数据缓存。其主要的输入侧信号有s_axis_tvalid,s_axis_tdata,s_axis_last。通过对SAV图像定时基准码的检测,判断行有效数据的起始,并开始进行缓存。图8所示为AXI4-Stream Data FIFO输入信号时序。

Figure 7 AXI4-Stream Data FIFO IP core图7 AXI4-Stream Data FIFO IP核

Figure 8 AXI4-Stream Data FIFO input signal timing diagram图8 AXI4-Stream Data FIFO输入信号时序图

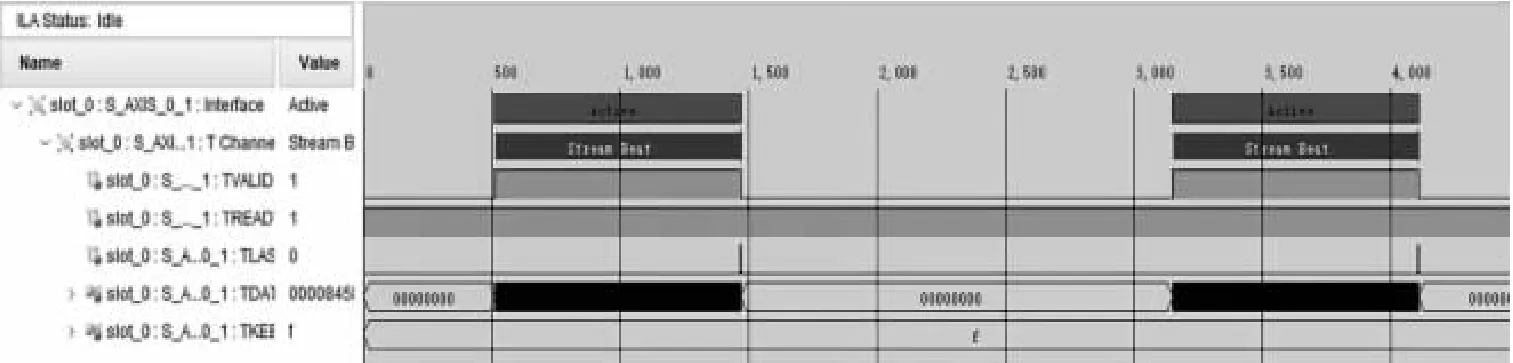

AXI DMA为内存和AXI4-Stream目标外设之间提供高带宽内存访问。AXI DMA的主要信号有AXI DMA写入时钟m_axi_mm2s_aclk,AXI DMA数据写入端口s_axi_s2mm_tdata,AXI DMA读出时钟m_axi_s2mm_aclk,AXI DMA数据读出端口m_axi_mm2s_tdata,AXI DMA的写入握手信号有s_axi_s2mm_tready,s_axi_s2mm_tlast,s_axi_s2mm_tvalid。图9所示为AXI DMA写入握手信号时序图。AXI DMA的读出握手信号有m_axi_mm2s_tready,m_axi_mm2s_tlast,m_axi_mm2s_tvalid。图10所示为AXI DMA读出握手信号时序图。

Figure 9 AXI DMA input handshake signal timing图9 AXI DMA写入握手信号时序图

Figure 10 AXI DMA output handshake signal timing图10 AXI DMA读出握手信号时序图

为了使视频图像流畅无撕裂现象,利用AXI DMA通过DDR3 SDRAM进行了帧的三缓存设计。利用AXI4-Stream Data FIFO每行960个数据产生s_axi_s2mm_tlast信号与AXI DMA进行握手,将数据缓存至DDR3 SDRAM中,缓存540行之后进行下一个缓冲区地址的切换,4个AXI DMA每路视频图像均有3个缓冲区,一共12个缓冲区。且通过将不同AXI DMA的m_axi_mm2s_tready信号置成高电平来切换不同的视频图像源,4路视频图像分为4个区域,形成田字格分布,分别对应4个AXI DMA模块。图11为AXI DMA模块分布,前540行分别是DMA1与DMA2切换,后540行是DMA3与DMA4进行切换。

Figure 11 AXI DMA module distribution图11 AXI DMA模块分布

5 实验结果

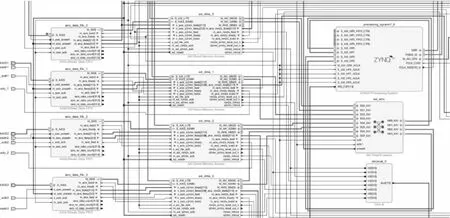

如图12所示为本文系统在Vivado环境下的顶层设计框图,即采用了4个AXI4-Stream Data FIFO与4个AXI DMA对视频流进行行缓存以及利用PS核对AXI DMA进行控制。

Figure 12 Block design diagram图12 顶层设计框图

将4个高清数字相机通过SMA线缆与FPGA连接,加电正常工作后,如图13所示,在监视器上可以看到4路SDI视频流分开显示的效果。视频图像无撕裂、无抖动,且流畅。整个系统设计使用的LUT、LUTRAM、FF、BRAM和IO资源利用率如表2所示。为后续加入视频图像处理算法提供了充裕的空间。

Figure 13 Experimental results图13 实验结果图

Table 2 System resource utilization

6 结束语

本文设计并实现了一种基于Zynq FPGA的SDI视频图像分割系统。该系统采用高清数字串行解码芯片TW6874同时对4路数字高清视频图像进行并行采集抽样,并导入至FPGA中,从而在显示器中分开显示。采用AXI4-Stream Data FIFO模块进行行缓存,灵活方便。并用AXI DMA模块将视频图像数据高速三缓存至DDR3 SDRAM,资源占用少,为以后视频图像处理算法的集成提供了充裕的空间。本文系统实现了分割视频图像无撕裂、无抖动、高帧频的输出,解决了传统的视频图像分割器辨率低、帧率低等问题,为实现大视场视频图像拼接提供了基础。