一种双回路驱动的纳秒快前沿高重复频率脉冲源

2021-10-11黄寅孟永鹏黄彦钦王亚杰高新宇成永红

黄寅,孟永鹏,黄彦钦,王亚杰,高新宇,成永红

(1.西安交通大学电力设备电气绝缘国家重点实验室,710049,西安;2.西安电子工程研究所,710100,西安)

随着科学技术的不断进步,电子设备在不断小型化和集成化的同时,也增加了其对电磁干扰的敏感性和易损性,使得电磁威胁变得越来越突出[1-2]。由于强电磁脉冲不断实现超大功率化和超宽带化,迫使各国积极开展电子设备在强电磁脉冲环境下的适应性及其防护加固技术的研究[3]。对于电磁脉冲环境及其工程防护技术的研究,以及各种电磁脉冲防护措施防护效果的检验与评定,均离不开电磁脉冲模拟试验[4-5]。电磁脉冲模拟环境一般通过模拟系统产生,该系统主要由脉冲源、天线和测试系统组成[6]。模拟系统所能提供的模拟环境取决于脉冲源与天线的设计,其中脉冲源是电磁脉冲模拟器中提供电磁能量的核心装置,其性能指标将直接决定着电磁脉冲模拟环境的参数指标。

实际上,真实的电磁脉冲环境是非常复杂的,单脉冲并不能模拟真实的电磁脉冲环境,高重复频率的脉冲比单脉冲更接近于真实情况中的电磁脉冲环境,故重复频率参数也逐渐纳入到模拟试验环境的标准中[7-8]。在工业应用方面,大功率和高能量已不是单纯追求的目标,相比之下更重要的是脉冲波形和重复频率[9-10]。围绕设计并研发具有快前沿、窄脉宽(半高宽,本文中脉宽均代表波形半高宽度)或高重复频率参数特性的脉冲电源,国内外学者开展了一系列的研究。国内方旭等人研制了一套前沿700 ps、幅值2 kV、工作频率200 kHz的脉冲源,可连续工作3 min[11];赖雨辰等采用漂移阶跃恢复二极管(DSRD)器件与脉冲变压器研制了一套纳秒级前沿、幅值可调、工作频率400 kHz的固态脉冲源[12];国际上,Grekhov采用快速离化二级管开关(FID)技术研制了一套可产生10 kV、前沿80 ps、重复频率100 kHz的GIN-10型脉冲电压源[13];Merensky等研制一套幅值2.2 kV、在脉冲串模式下工作频率仅为1 MHz的固态脉冲源[14]。近年来,这些研究成果虽然凭借不断提升的幅值、重复频率以及更快的前沿和更窄的脉宽丰富了高功率电磁环境模拟与效应的研究,但随着电磁脉冲技术研究逐渐向兆赫兹以上的工作领域拓展,对于具备更宽频谱的纳秒快前沿窄脉宽,且重复频率达兆赫兹以上水平的脉冲电源的研究在国内仍鲜有报道,有关工作还需要进行更加深入的研究。

DSRD是一种新型的半导体固态开关,它具有开断速度快、功率密度大、重复频率高等优点,被认为是脉冲功率发生器的理想固态开关[15-16]。针对脉冲源的纳秒快前沿与3 MHz高重频参数,本文利用正反向泵浦电流原理设计了基于DSRD开关的脉冲仿真电路,采用双回路驱动方式的脉冲发生电路,与单回路驱动方式相比降低了储能电感的电流,提升了储能电感的充放电效率,优化了DSRD正反泵浦的工作条件,从而提高了脉冲发生电路的工作频率;建立了DSRD等效仿真模型,计算了脉冲发生电路的主要元件参数,并分析了输入电压、导通时间、负载电阻及DSRD寄生电容等对输出脉冲特性的影响规律,最终应用新型双回路驱动DSRD器件研制了一台纳秒快前沿高重频脉冲源,产生前沿小于2 ns、幅值1 kV、工作频率达3 MHz的重复频率脉冲。本文为开展与电磁脉冲相关的各种效能以及损伤规律提供了基础设备,同时也为等离子体化学应用及材料表面改性等工业应用提供了相应的技术支持。

1 脉冲源电路设计

1.1 DSRD工作原理

相较于普通二极管,DSRD本征部分的掺杂水平更低,从而能够实现漂移恢复。DSRD的典型结构如图1所示[17]。其一般由一个或多个P+-N-N+结构组成,在实际器件制造过程中,一般采用多个DSRD串联堆叠而成。在脉冲发生电路中,由于DSRD空间电荷载流子的产生与消失是其工作特性的关键,因此一般采用反向泵浦电流将载流子强制复合,从而实现器件的快速关断。

图1 DSRD典型结构示意图[17]Fig.1 Schematic diagram of typical DSRD structure[17]

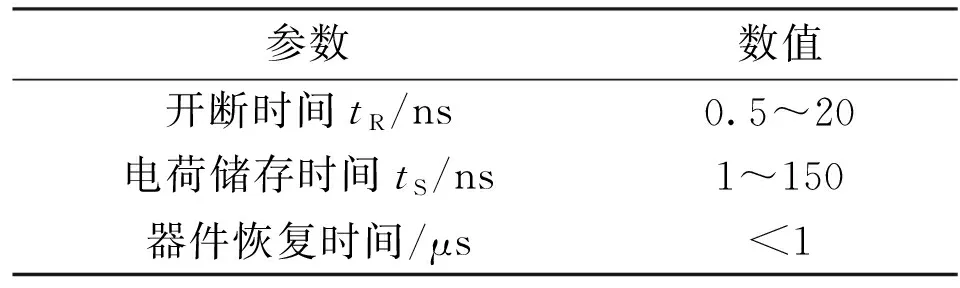

输出脉冲波形的前沿与重复频率主要由所采用的DSRD器件的技术参数与脉冲发生电路的结构决定,目前国内外已应用的DSRD器件的主要技术参数如表1所示[18-20]。

表1 DSRD主要技术参数Table 1 Main technical parameters of DSRD

1.2 双回路驱动DSRD脉冲发生电路设计

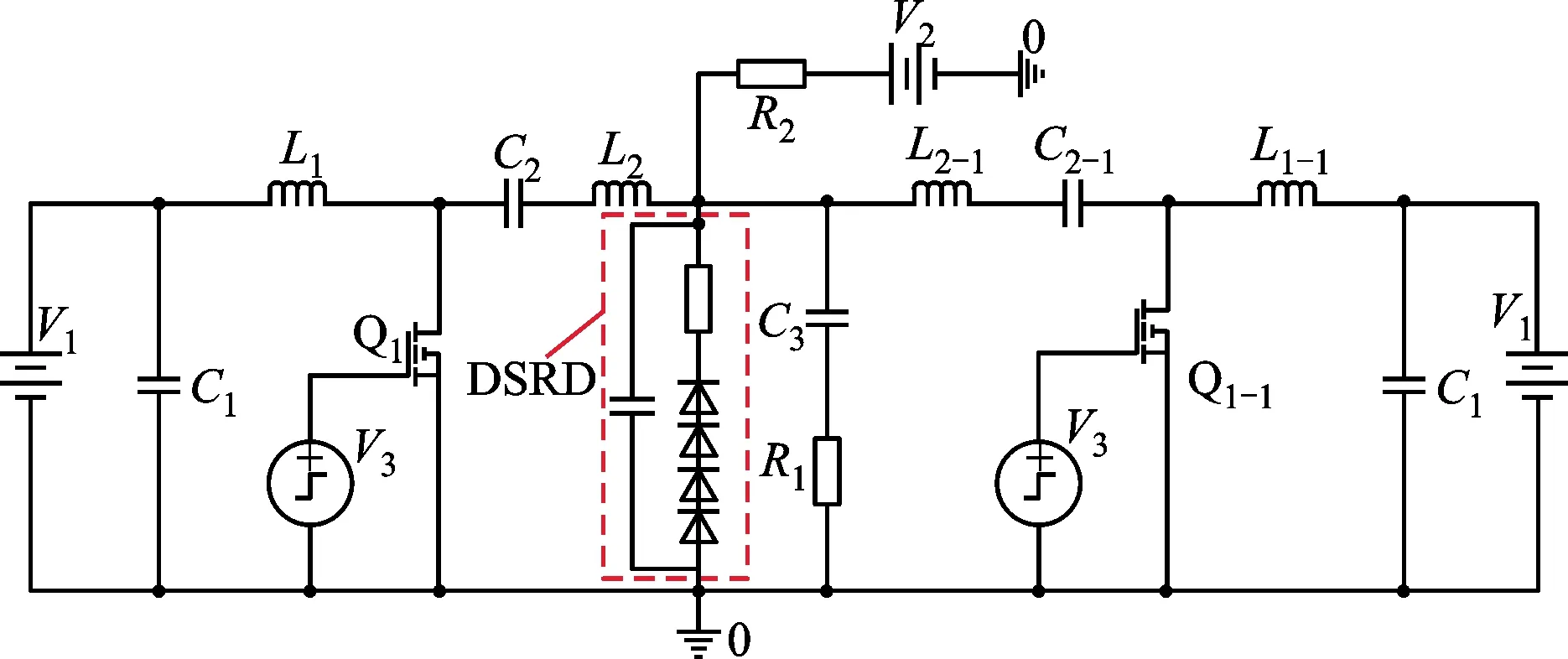

设计的双回路驱动DSRD脉冲发生主电路如图2所示,其中V1、V2为输入直流源,V3为开关管Q1与Q1-1的触发源。电阻R2为直流源V2的隔离电阻,在产生高压脉冲时,使高压降在电阻上以保证V2电压的恒定。

图2 脉冲发生电路Fig.2 Pulse generating circuit

双回路电路的工作原理如下:当初始时间t=0 s时,开关管均为关断状态,回路中没有电流流动,电容C2与C2-1被直流源V1、V2充电至偏置电压ΔV(ΔV=V1-V2),之后开关管Q1与Q1-1在V3的触发信号下导通,直流源V1通过开关管回路对前级储能电感L1与L1-1分别充电,同时Q1、Q1-1,C2、C2-1,L2、L2-1分别与DSRD构成两组振荡放电回路,DSRD在正向泵浦电流的作用下导通,经过开关管导通时间ΔT后,开关管Q1与Q1-1关断,此时DSRD在正向储存电荷的作用下仍然维持导通,V1通过L1、L1-1,C2、C2-1,L2、L2-1,DSRD回路对后级电感L2与L2-1进行反向充电,并对DSRD进行反向泵浦,反向电流不断消耗着先前泵入P+-N-N+结中的储存电荷,当结中的正向电荷被消耗完时,DSRD将在纳秒级的时间内关断,使得流经电感L2与L2-1的电流切换通路通过隔直电容C3向负载R1放电,从而形成前沿为纳秒级的快前沿脉冲。

放电回路中L2、L2-1与R1的参数将直接影响脉冲的后延时间,从而改变脉冲波形的脉宽;而直流源V1、V2的差值[21],开关管的导通时间ΔT将影响电感的充电电流与充电时间,L1与L1-1的充电电流增加或充电时间增大,都将使得DSRD正向导通时所产生的载流子增多,反向泵浦时间将延长;电感L2与L2-1的电流越大,在负载上产生的脉冲电压峰值越高,反之,负载上产生的电压将降低。

当采用双回路驱动脉冲产生电路时,由于两回路为并联方式,因此实际对负载R1放电回路中的电感L0=(L2L2-1)/(L2+L2-1),即在产生同样参数的脉冲波形时,每条支路电感的取值约为单回路驱动时的1倍,而其峰值电流仅为单回路的1/2,电感中存储的能量为

(1)

式中:I1为开关管关断时的电流。根据式(1)可知,双回路驱动时每条支路中储能电感最大能量仅为单回路的一半;当脉冲产生电路为双回路驱动时,可提升每条支路储能电感的充放电效率,使快前沿脉冲源能够在更高的触发频率下稳定工作。

1.3 DSRD等效模型

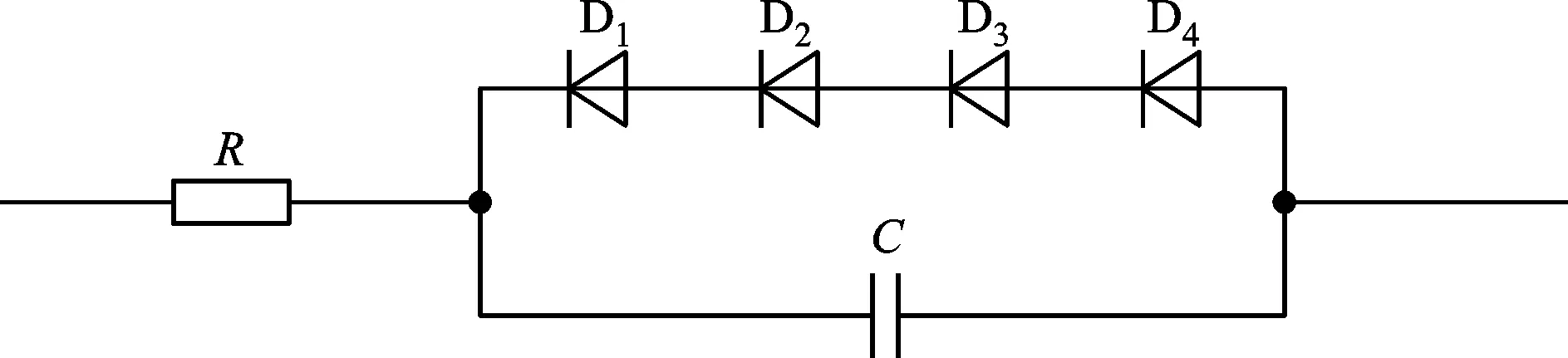

由于每层P+-N-N+结存在电容效应,而电容的大小将直接影响到脉冲的前沿时间,此外DSRD器件在工作时也会产生相应的热损耗,如正向、反向热损耗、恢复损耗等,造成器件的发热升温。在仿真过程中,采用单一的二极管等效模型无法模拟出实际DSRD的工作情况。本文建立的等效模型采用IN4007二极管等效DSRD的P-N结构,通过4级串联来等效P-N结的多层堆叠,使用并联电容来等效P-N结所产生的电容效应,此外由于DSRD耐压值等参数的不同,其实际寄生电容的大小一般在2~30 pF,可根据实际需求修改模型参数,同时用电阻等效实际的热阻及相应损耗,阻值取1~3 Ω,建立的等效DSRD仿真模型如图3所示。

图3 DSRD等效仿真模型Fig.3 Equivalent simulation model of DSRD

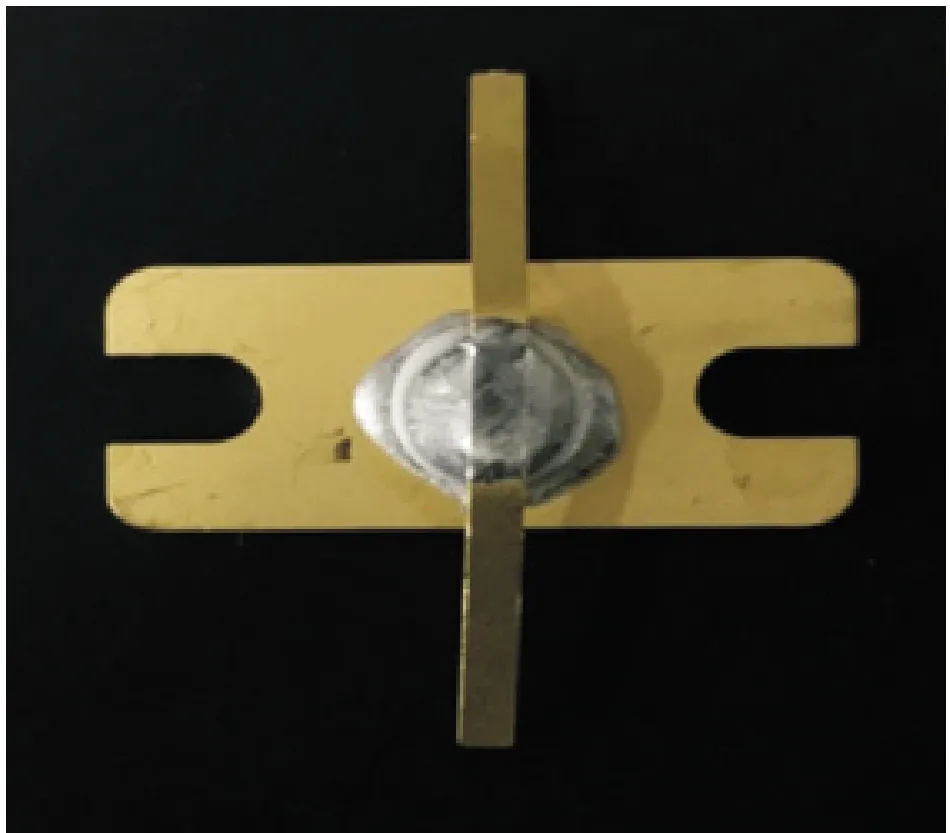

纳秒快前沿高重复频率脉冲源设计中使用的DSRD器件如图4所示。器件耐压值为4 kV,经测试其导通电阻R约为1 Ω,寄生电容C约为20 pF,开断时间tR<2 ns。在建立该器件的等效模型时,采用器件实际参数进行仿真设计。

图4 DSRD器件Fig.4 DSRD device

2 脉冲源主回路参数设计

以输入V1为100 V、负载电阻R1为50 Ω产生脉宽8 ns、幅值1 kV、重复频率3 MHz的重频快前沿脉冲为输出目标,进行脉冲产生电路中主要元件参数的计算。

首先对电感L2与L2-1进行计算,使放电回路的时间常数满足脉冲波形脉宽的要求。以图2左半部分的单回路为例,当L2对R1放电时,L1中储存的能量已全部转移到L2中,此时流经L1的电流IL1约为0.19 A,相对于IL2较小,因此可只考虑L2对放电回路的影响。

(2)

式中:L0=(L2L2-1)/(L2+L2-1),即L0为L2和L2-1的并联值;IR为负载R1上的实时电流;I0为负载上产生的峰值电流。由于DSRD等效仿真模型在实际仿真过程中关断时间为2 ns左右,即当负载上实时电流下降到峰值电流一半的时间为6 ns时,整个脉冲波形的脉宽时间约为8 ns,故可令I/IR=2,由式(2)可得

(3)

将t=6 ns、R1=5 Ω代入式(3)可得L0=432.8 nH。考虑实际仿真前沿时间等因素,可取电感L0为450 nH,即L2=L2-1=900 nH。在正反向电流泵浦过程中,电感L2与L2-1的能量均来自于L1与L1-1,加之回路中的热损耗,L1、L1-1的取值将略大于L2、L2-1,为了将前级电感中能量完全转移至后级,可取L1=L1-1=1 000 nH。因负载上电压幅值为1 kV,可知I=20 A,故L1、L1-1在开关管关断时的电流I1应为1 A。在开关管导通时,直流源V1稳压电容C1,开关管Q1、Q1-1与电感L1、L1-1构成两路二阶过阻尼振荡电路,仿真电路中使用Rs等效开关管的导通电阻,则L1、L1-1的充电电流可表示为

(4)

其中

(5)

(6)

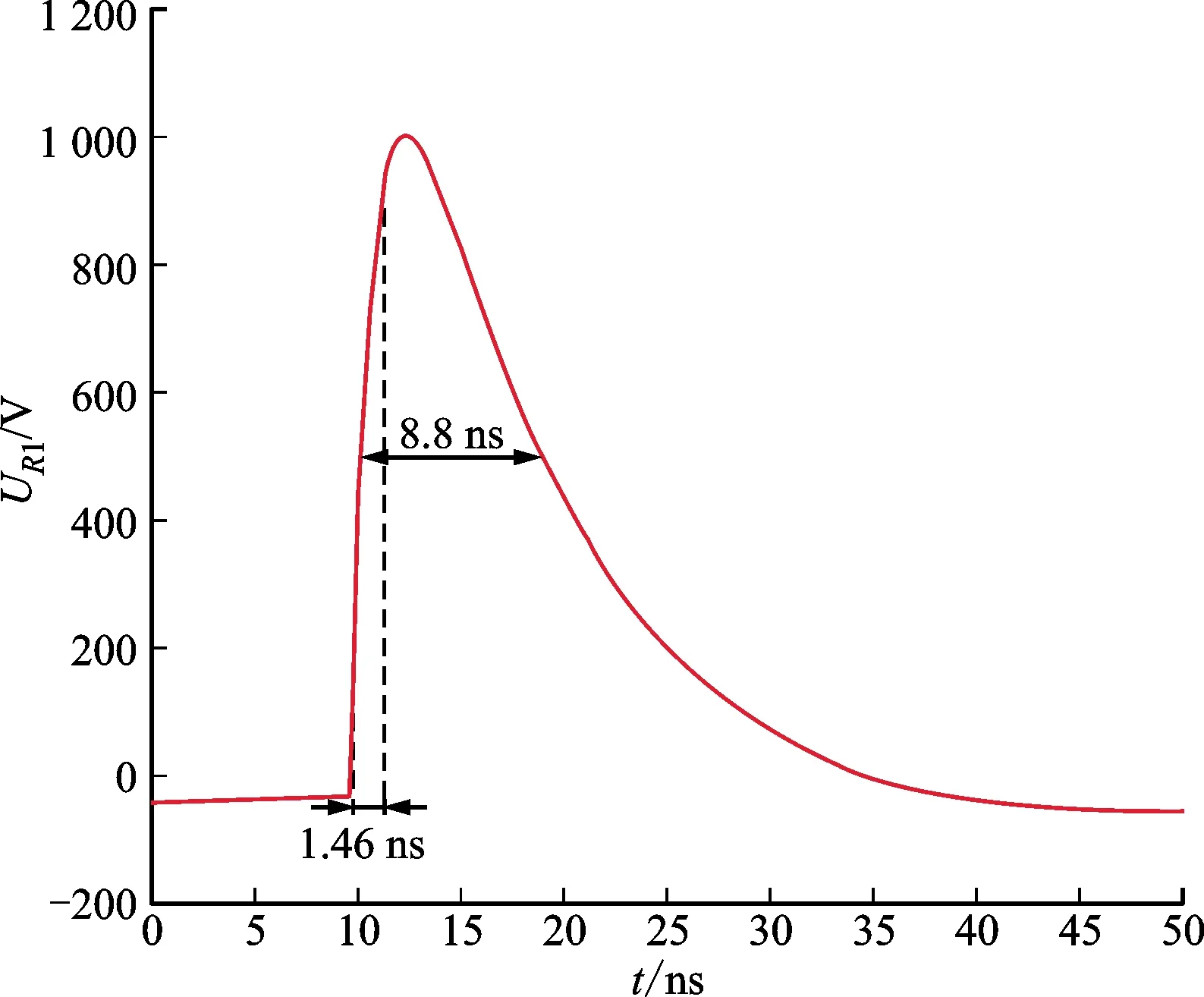

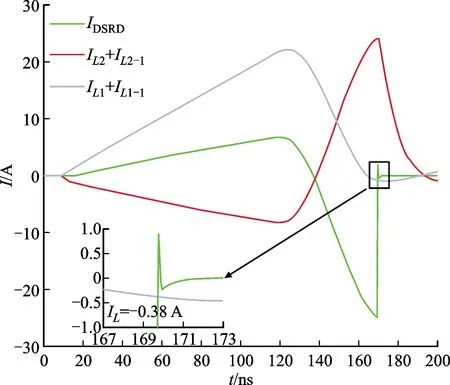

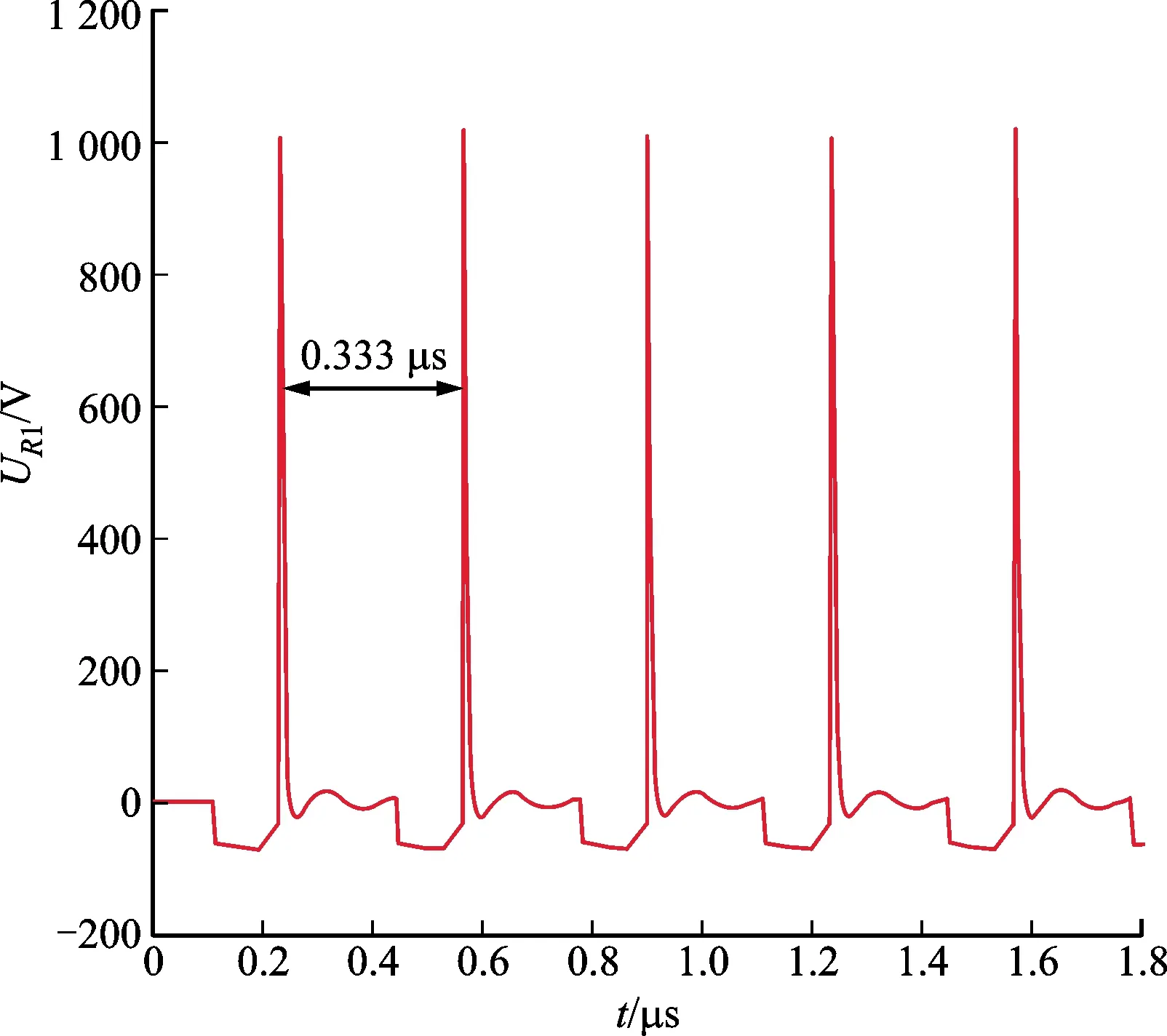

将V1=100 V、L1=1 000 nH、Rs=0.1 Ω、C1=1 μF、I1=10 A代入式(4)得t=93.6 ns,故可取开关管导通时间ΔT为95 ns。采用计算得到的元器件参数搭建脉冲源主回路的PSpice仿真模型,脉冲源以输入参数V1=100 V、V2=60 V、ΔT=95 ns进行仿真。图5~7分别为实际仿真时负载上产生的快前沿脉冲波形,储能电感与DSRD的电流波形,以及负载上的重复频率脉冲串。可以看到,输出脉冲前沿为1.46 ns,脉宽为8.8 ns,幅值1 025 V,重复频率3 MHz,各项参数满足预期输出指标。

图5 负载上产生的快前沿脉冲Fig.5 Fast rise time pulse generated on the load

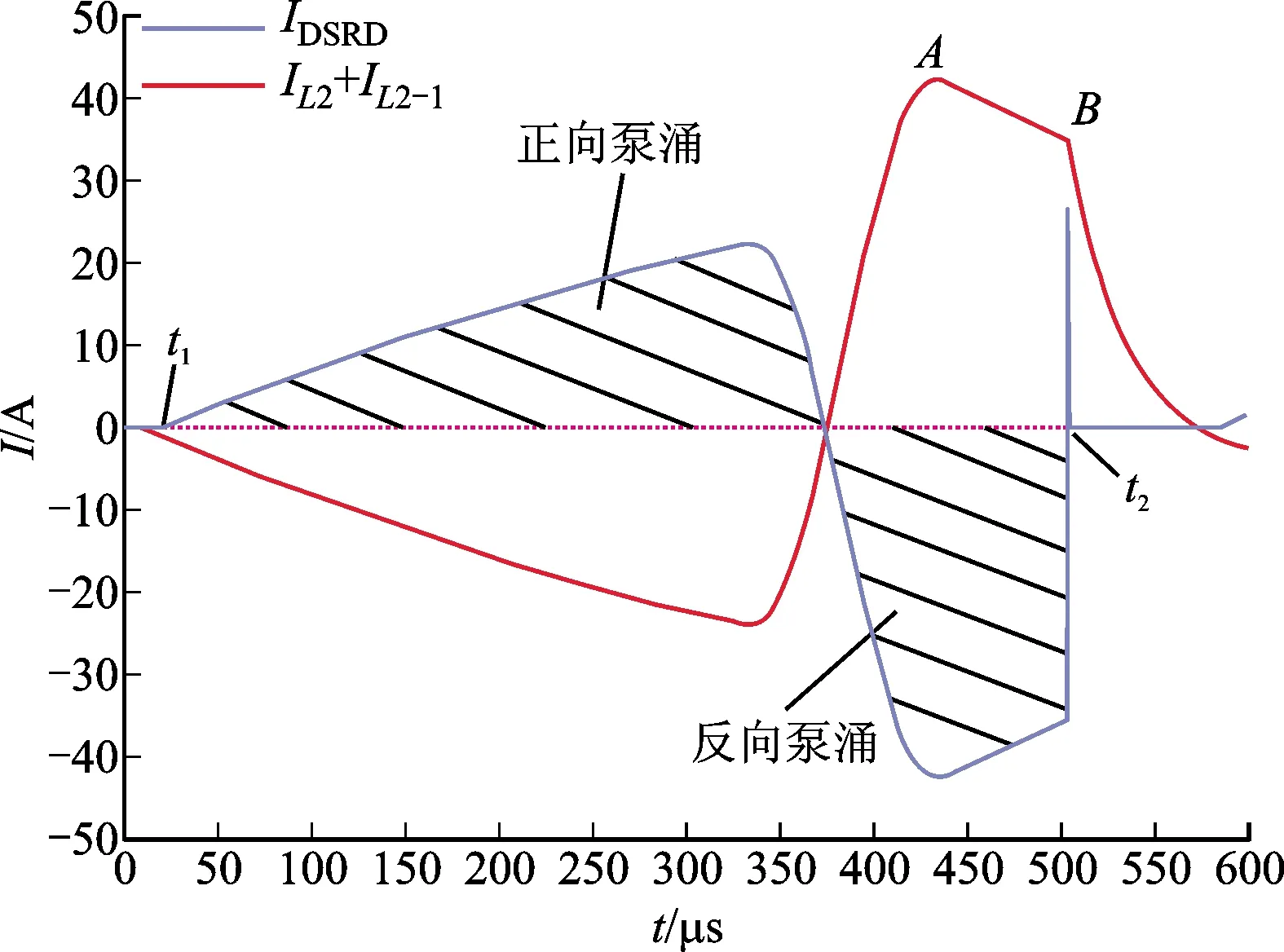

图6 储能电感与DSRD的电流波形Fig.6 Current waveform of energy storage inductor and DSRD

图7 负载上产生的重频脉冲串Fig.7 Repetitive pulse train generated on the load

值得注意的是,当要求产生脉冲后沿时间较长且幅值较高时,会出现实际输出脉冲幅值低于理论计算值的情况。这是由于当前级电感将开关管导通时间内所储存能量完全传递至后级电感时,后级电感中的电流将达到最大值,但由于反向泵浦电流持续时间不足以将二极管中所积累的正向电荷消耗完全,二极管尚未关断,根据式(7),可认为DSRD中所产生的电荷数量为流过电流对时间的积分。也就是说,当正向泵浦电流与坐标轴包围的面积与反向泵浦电流的大小相等时,DSRD中积累的电荷全部被消耗完,二极管关断,如图8所示。电荷数量的计算公式为

图8 储能电感与DSRD的电流波形Fig.8 Current waveform of energy storage inductor and DSRD

(7)

从图8可以看出,当后级电感电流达到最大值时(图中A点),由于DSRD未关断,后级电感将对前级电感进行反向充电;当二极管积累电荷消耗完全时(图中B点),回路电流切换通路,对负载进行放电,但由于电流下降,脉冲峰值无法达到预期输出指标。

因此在计算后延时间较长、幅值较高的脉冲电路参数时,应将ΔT适当增大,提高后级电感的电流幅值,使得DSRD关断时,后级电感的电流大小为实际需求的电流值,从而得到满足幅值要求的快前沿脉冲波形。

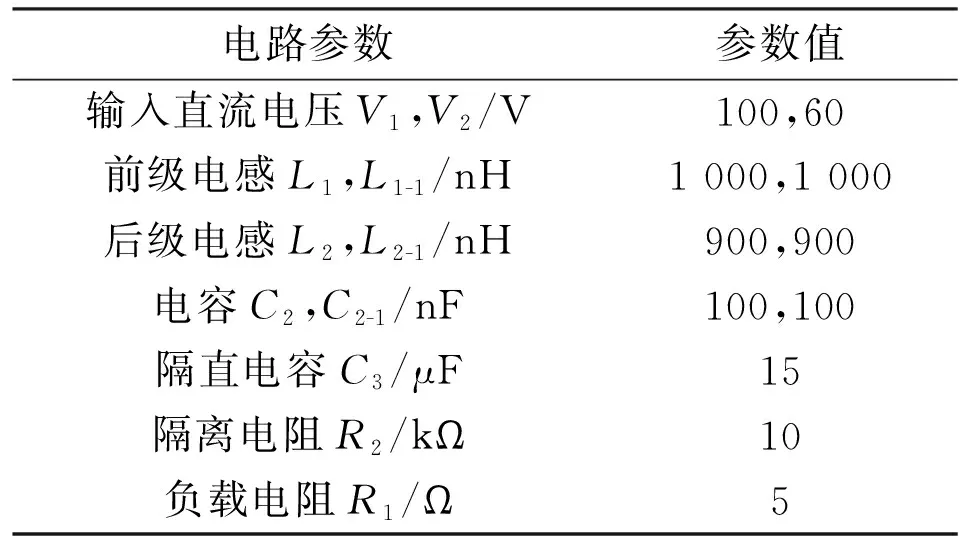

根据仿真计算得到的脉冲源发生电路主要元件输入参数如表2所示。

表2 脉冲电路相关参数Table 2 Related parameters of pulse circuit

3 脉冲源输出特性影响因素分析

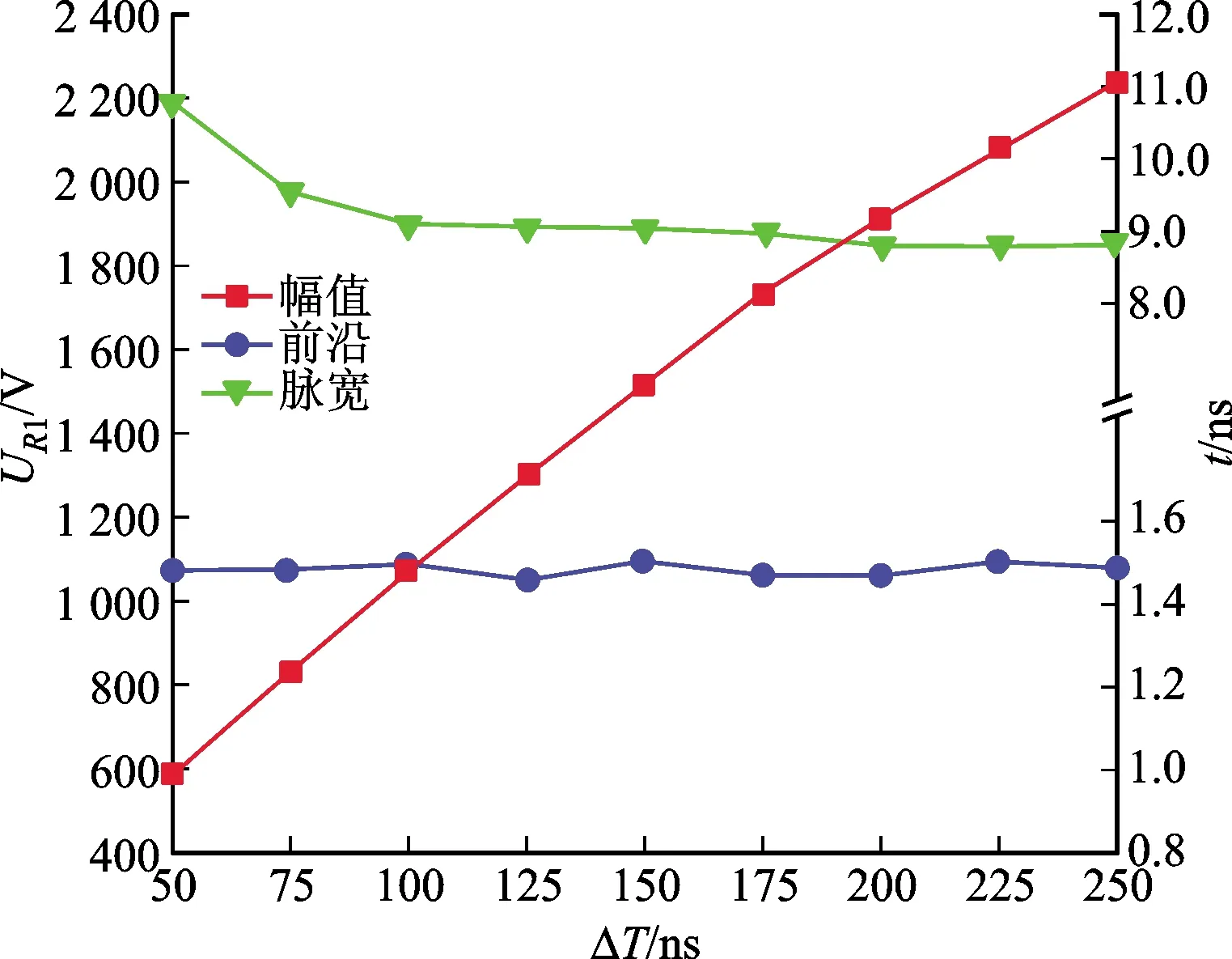

3.1 开关管导通时间对脉冲输出特性的影响

开关管Q1、Q1-1的导通时间将决定前级电感的充电时间,即决定脉冲发生回路中的电流峰值,从而改变快前沿脉冲的输出特性。图9所示为脉冲电路输出幅值、前沿及脉宽随开关管的导通时间ΔT的变化。可以看出,随着导通时间的延长,输出脉冲的幅值近似呈现线性增长,未出现后级电感反向充电造成幅值下降的现象。脉冲前沿基本保持不变,而脉宽将随着回路中充电电流的增大略微下降。在设计脉冲输出电路元件参数时,应考虑充电电流对脉冲后沿的影响,此外在要求脉冲输出幅值较高时,应考虑DSRD正向积累电荷消耗的问题,并根据实际情况调整开关管的导通时间,从而满足对快前沿脉冲参数的需求。

图9 ΔT对脉冲输出特性的影响Fig.9 The influence of ΔT on pulse output characteristics

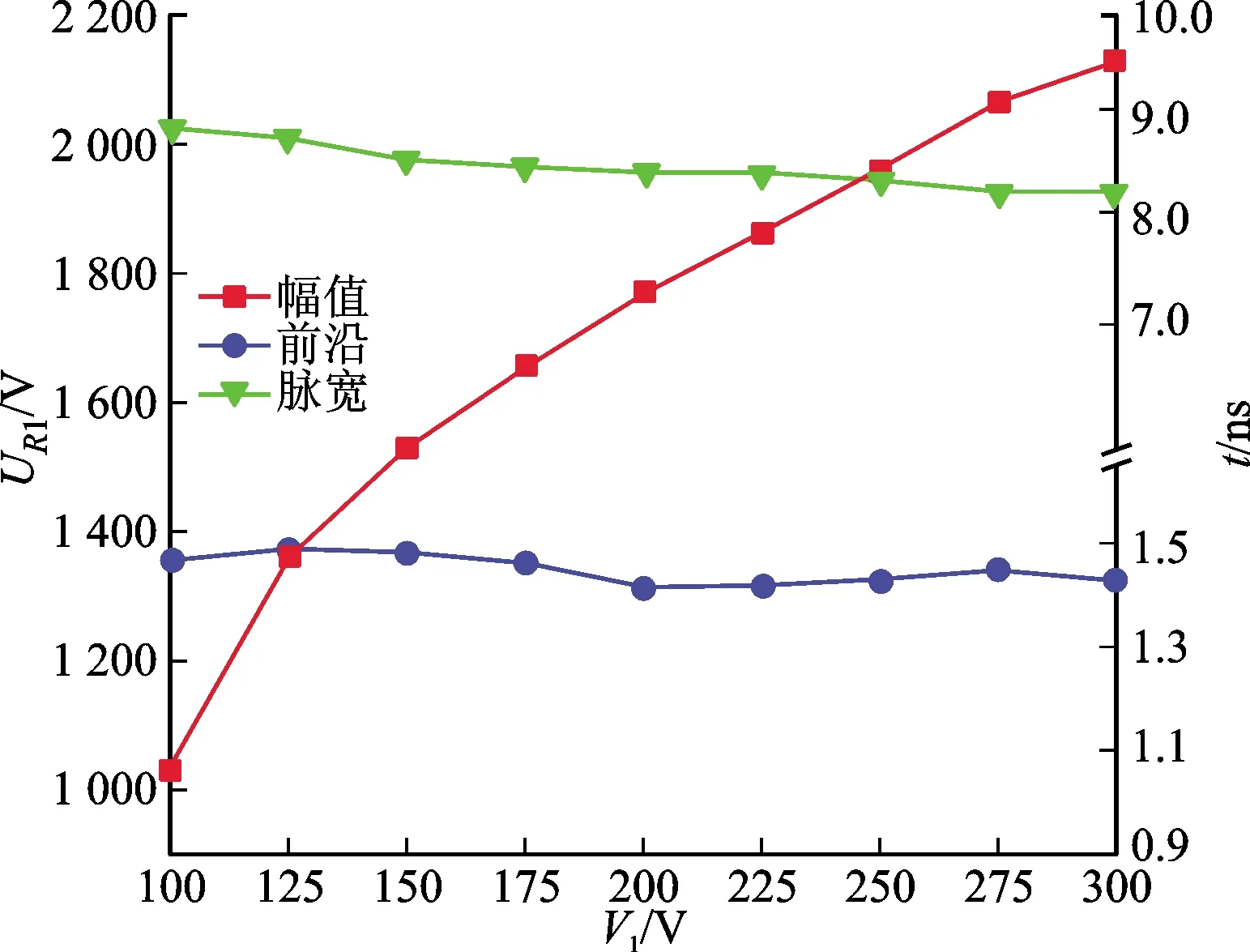

3.2 输入电压对脉冲输出特性的影响

当脉冲电路输入直流电压V1增大时,电容C2、C2-1两端电压差ΔV将增大,使得开关管导通时前级储能电感的充电电流上升速度更快。脉冲电路各项输出特性随直流输入电压V1的变化如图10所示。

图10 V1对脉冲输出特性的影响Fig.10 The influence of V1 on pulse output characteristics

从图10可以看出,当输入直流电压小于125 V时,输出脉冲的幅值呈现线性增长,而在直流电压较大时,电压幅值的增加不再符合线性增长,说明脉冲发生电路中出现了DSRD正向积累电荷过多的现象,导致幅值略微下降。与开关管导通时间对输出特性的影响类似,直流输入电压的改变对脉冲前沿的影响较小,而当回路中电流峰值增大时,同样出现了脉宽减小的现象。

3.3 负载电阻对脉冲输出特性的影响

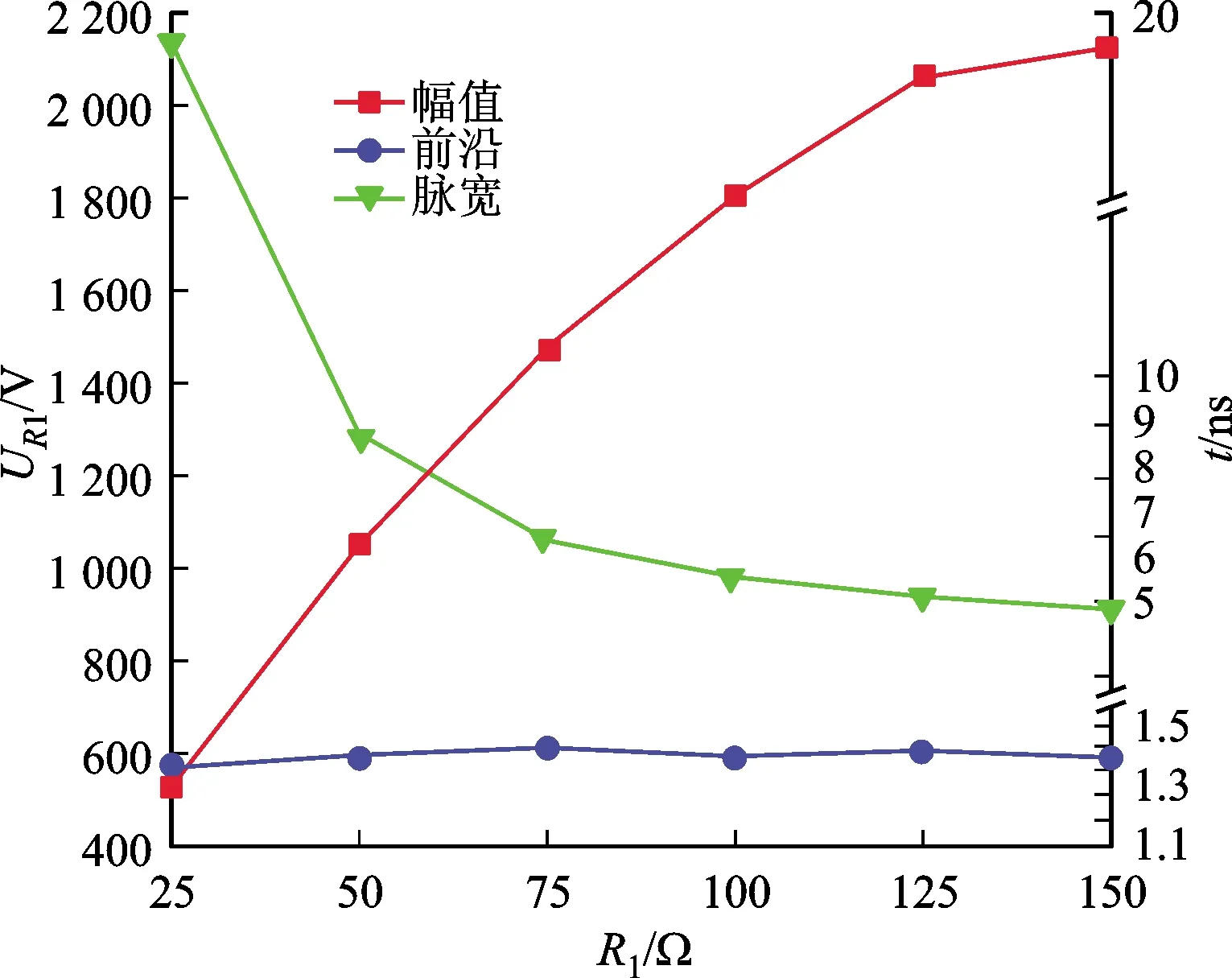

由式(2)(3)可知:输出负载R1的变化将直接影响输出脉冲的幅值与脉宽。当输出负载变化时,脉冲电路各项输出特性的变化如图11所示。

图11 R1对脉冲输出特性的影响Fig.11 The influence of R1 on pulse output characteristics

从图11可以看到,随着输出负载的增大,脉宽的减小速度逐渐缓慢并趋于稳定,而负载变化对脉冲前沿无明显影响,此外负载的线性增加并不能使电压幅值线性增加,负载的增大将影响脉冲发生回路的电流峰值,使脉冲幅值上升趋势变缓。

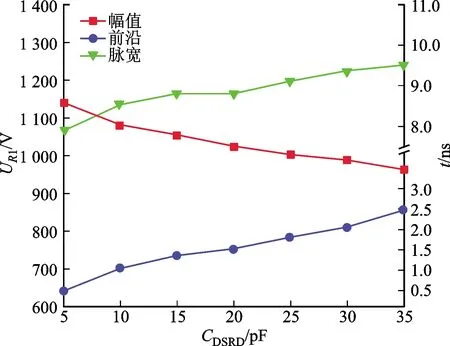

3.4 DSRD寄生电容对脉冲输出特性的影响

DSRD器件的技术参数将直接决定脉冲波形的前沿与脉宽等特性,通过调整DSRD等效仿真模型中寄生电容的取值,得到脉冲电路各项输出特性的变化如图12所示。可以看出,当寄生电容增大时,输出脉冲的前沿明显延长,前沿的变化同样会引起波形脉宽的略微增加。此外当寄生电容减小时,在DSRD关断时流过其的电流减小,放电回路电流增大,将使得输出电压幅值增大。因此,在进行DSRD器件筛选时,应根据具体脉冲前沿要求选取寄生电容合适的器件。

图12 DSRD寄生电容对脉冲输出特性的影响Fig.12 The influence of DSRD parasitic capacitance on pulse output characteristics

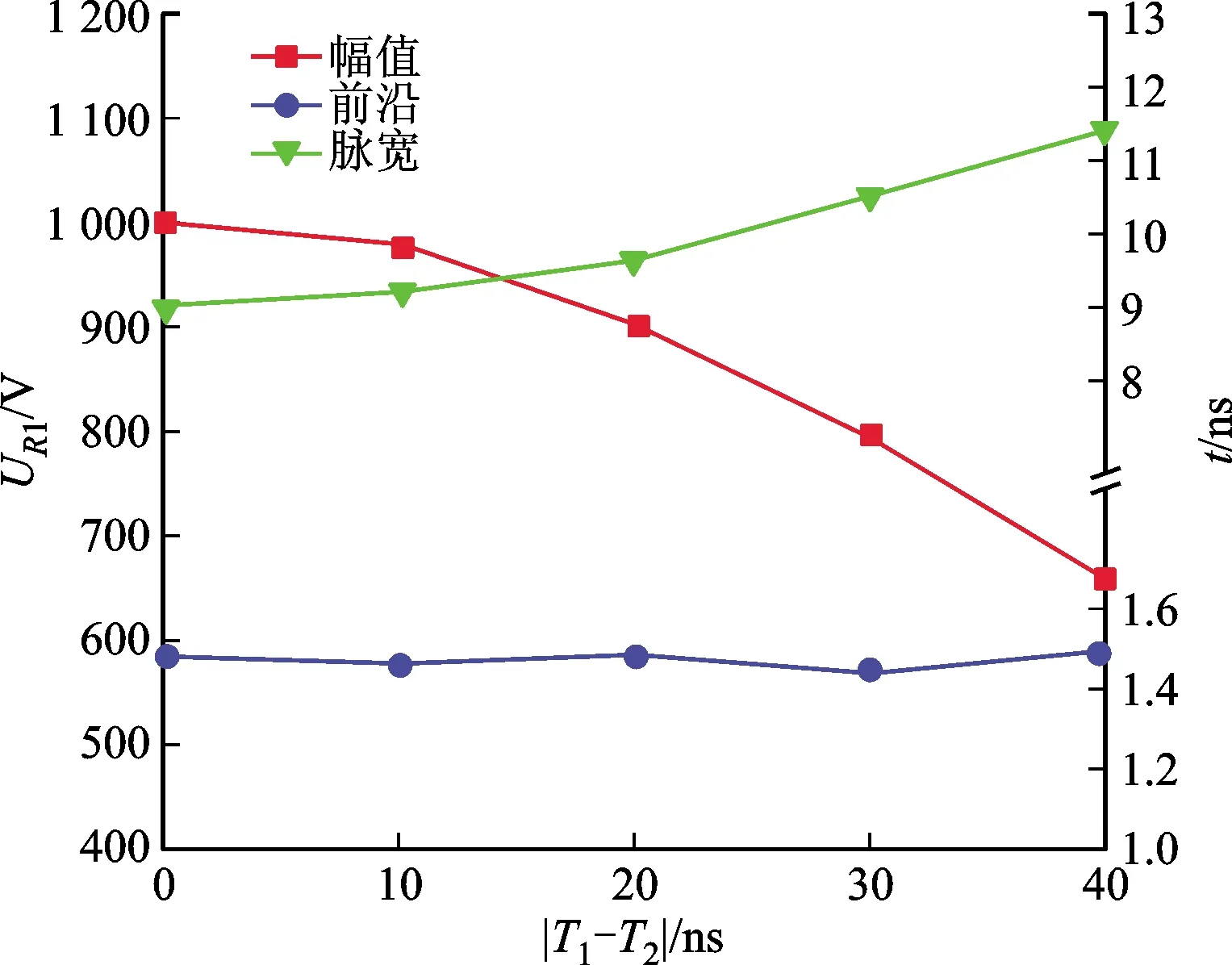

3.5 开关管触发同步性对脉冲输出特性的影响

对于双回路驱动的脉冲发生电路,两个开关管触发同步性将影响两条储能回路中电感储存的能量。如图13所示,当两个开关管的触发时间差值|T1-T2|<10 ns时,所产生的快前沿脉冲无明显的区别,能够满足相应的参数要求,而当触发时间差大于15 ns时,将对输出脉冲的电压幅值与脉宽产生较大的影响,电压幅值将急剧下降,造成波形畸变或失真。因此在实际脉冲源的设计中应当采取相应的同步触发措施,保证两个开关管的触发时间差小于10 ns,保证输出波形的各项参数符合要求。

图13 触发时间差对脉冲输出特性的影响Fig.13 The influence of trigger time difference on pulse output characteristics

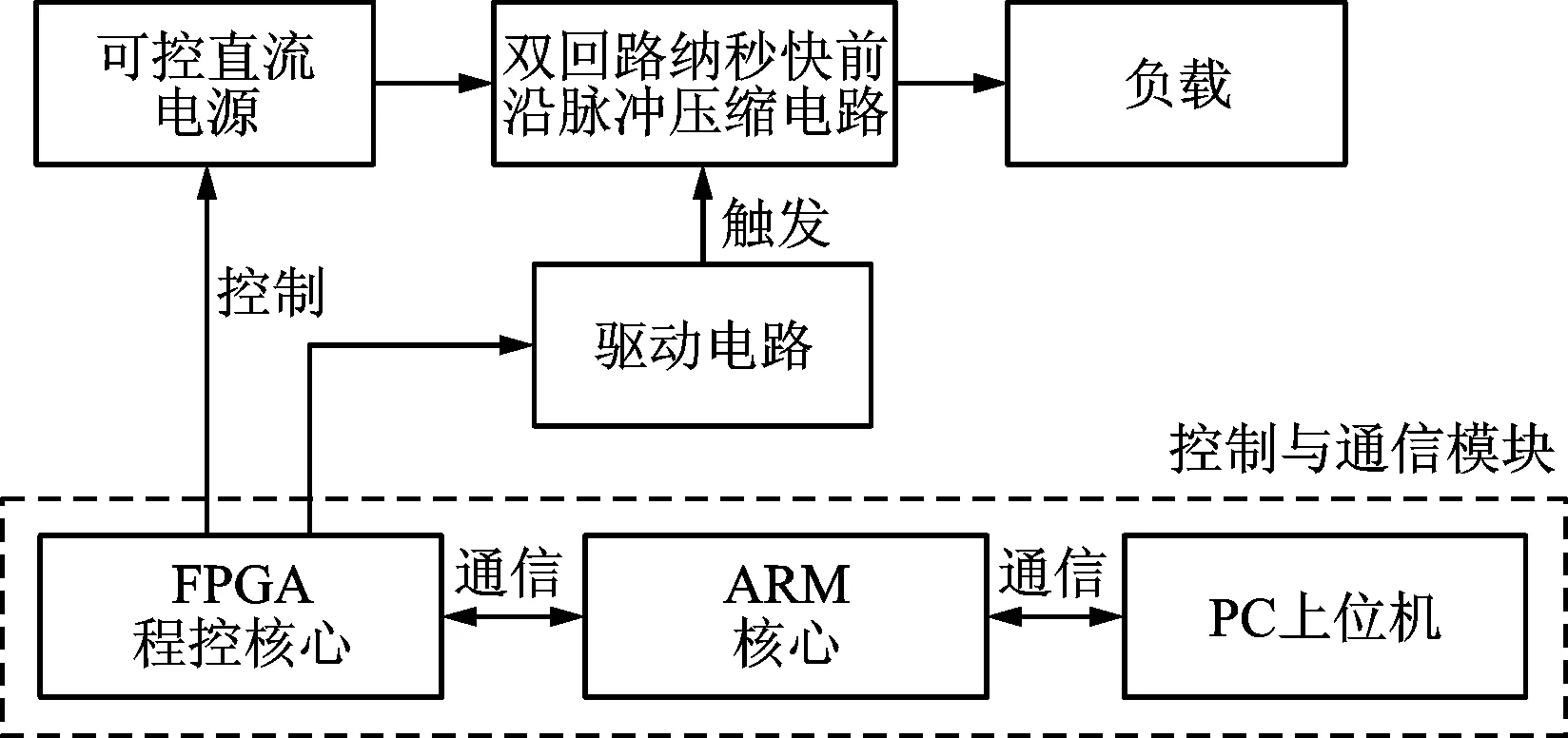

4 脉冲源的设计与实现

4.1 脉冲源设计

根据仿真分析结果,在脉冲源实际研制过程中,首先根据输出参数需求对其中的DSRD开关器件及储能电感分别进行筛选和设计,从而确定脉冲波形的前沿和工作频率。输出脉冲波形的幅值与脉宽可通过调节直流输入电压、开关管触发时间及输出负载来进行调整。

本文设计的快前沿脉冲源整体结构如图14所示,控制核心采用快速低功耗FPGA(EP3C5E144I7 N)作为核心控制器,驱动电路中采用的金属氧化物半导体场效应晶体管(MOSFET)为IXYS公司的DE475-102N21A,其最大漏源击穿电压VDSS=1 000 V,开通和关断时间分别约为5、8 ns[22]。驱动电路部分采用高速电压比较器将触发信号前沿进一步缩短并将信号幅值升高至5 V,保证了两个MOS管的同步触发,并可通过上位机设置输出脉冲的幅值、频率、工作模式等各项参数对电源的输出进行控制。

图14 快前沿脉冲源整体结构框架Fig.14 The overall structure frame of the fast rise time pulse source

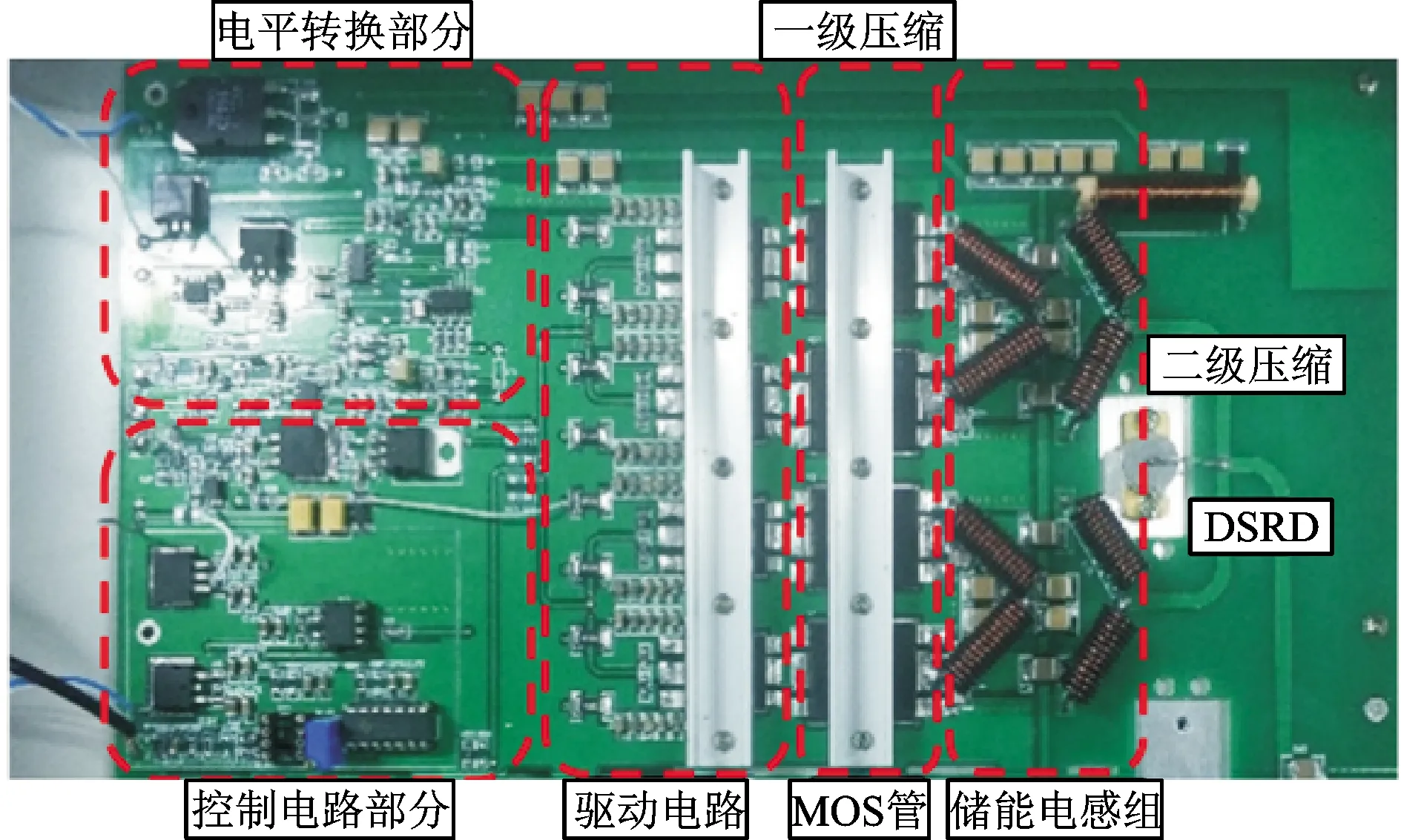

图15为设计得到的脉冲源电路,整体结构按照低压与高压分区布置,低压分区包含电平转换部分、控制电路部分,高压分区包含双路并联脉冲形成的主回路,布局为轴对称结构设计,满足并联工作同步性要求,并降低了各功率器件的热功耗。负载采用特征阻抗为5 Ω的同轴负载,以便能较为理想地反映脉冲源的各项输出特性,验证所设计的双回路驱动DSRD脉冲发生电路的可行性,在其他应用场景下,需考虑不同负载类型对脉冲波形参数的影响。

图15 脉冲源电路Fig.15 Pulse source circuit

4.2 实测波形

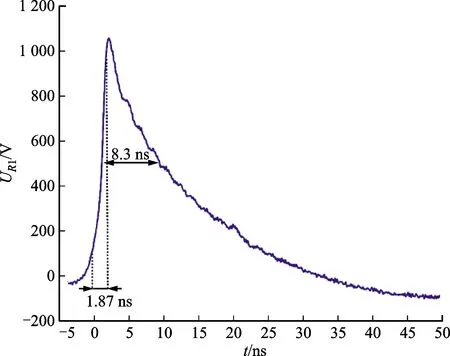

对研制出的纳秒快前沿高重复频率脉冲源进行了测试,在设定输入直流电压100 V、重复频率3 MHz条件下,负载上所产生的快前沿单个脉冲和重频脉冲波形分别如图16和图17所示,可以看到实测波形前沿(1%~90%)为1.87 ns,脉宽8.3 ns,重复频率3.02 MHz,首个脉冲幅值达156 V。相较于仿真波形,实测波形前沿略微增加,脉宽略微减小,这是因为等效DSRD的仿真模型采用的是理想二极管,在导通时可瞬时导通,而实际的DSRD在关断过程中具有一定关断时间。此外受制作工艺以及电路中安装方式的影响,器件寄生电容会增加,使得波形前沿较仿真结果更长。而实际电路中电感非理想元件,将有一定的电阻,根据式(2)和(3)可知,这将使得回路的时间常数增大,负载上的放电时间变短,脉宽减小,图11的仿真结果也表明了脉宽随回路电阻增大而减小。

图16 单个快前沿脉冲波形Fig.16 Single fast rise time pulse waveform

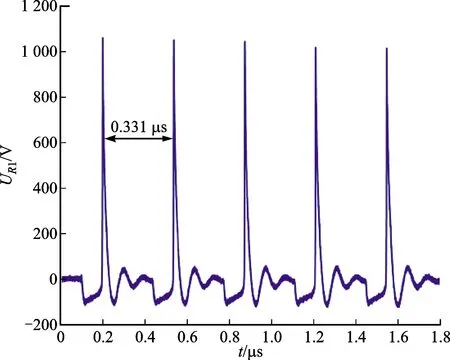

在图17中,单个脉冲幅值将随着脉冲数量的增加略微下降,这是由于脉冲源在高重频的工作环境下,各器件上将产生一定的热损耗,释放在负载上的能量将略微下降。脉冲幅值从1 056 V下降到1 010 V,下降率4.6%,最小脉冲幅值大于1 kV,满足预期的输出指标。脉冲波形比较理想,工作稳定,能够满足相关的实验需求。

图17 高重频快前沿脉冲Fig.17 High repetition frequency and fast rise time pulse

5 结 论

本文利用正反向泵浦电流原理设计了双回路驱动快速开关的快前沿重复频率脉冲电路。该电路提升了储能电感的充放电效率,优化了DSRD的正反泵浦条件,使其重复工作频率可达3 MHz。建立了DSRD等效模型,并计算了脉冲产生电路的主要元件参数,仿真分析了脉冲发生电路中不同参数对脉冲前沿、脉宽、幅值等输出特性的影响规律。研究表明DSRD器件参数直接影响脉冲的前沿与脉宽,输入电压与导通时间主要影响脉冲的电压幅值,而负载电阻的变化会影响脉冲的幅值与脉宽。

基于仿真设计参数,应用新型半导体固态开关DSRD研制出一台纳秒快前沿高重频脉冲源,可输出前沿1.87 ns、脉宽8.3 ns、幅值1 kV、工作频率可达3 MHz的重复频率脉冲,为电磁防护、等离子体化学应用及材料表面改性等工业应用相关研究提供了实验手段和技术支持。