无源数字相控阵信号侦察处理平台设计∗

2021-10-11乔雪原

乔雪原

(中国西南电子技术研究所 成都 610036)

1 引言

相控阵体制的无源侦察系统采用数字波束赋形(Digital Beam Forming,DBF)算法形成多个高增益波束来实现信号侦察,该方法具有多目标跟踪、机动性强、反应时间快、抗干扰能力强等优点,相比传统侦察系统可大幅提高目标截获概率[1~6]。

尽管相控阵雷达具有如此明显的优势,但随着空间目标的日益复杂,采样率的不断提高,更高的数据率、更大的信号带宽,更多的数据类型也为相控阵雷达带来了新的问题[2]。为了实现全频段、全空域的信号侦察,信号侦察处理平台需要具备快速进行信号检测、信号识别和信号分析的能力;为了便于进行信号的事后分析和回放,需要将目标信号的中频或基带信号按统一的数据格式进行实时存储。同时,由于数字相控阵可以同时跟踪多个目标,处理平台需要同步存储多路信号的采样数据,这就要求信号侦察处理平台具备实时、高速的数据存储能力。

2 系统设计

2.1 工作流程及组成

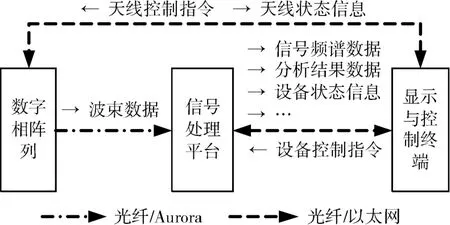

无源数字相控阵信号侦察系统主要包括无源数字相控阵天线、信号处理平台和显示与控制终端三部分组成,组成框图如图1所示。其中信号处理平台主要接收数字相控阵输出的合成后波束数据,对数据进行频谱处理,完成全频段的信号搜索及信号检测发现,实现全频段、全空域的频域监视;完成信号的检测识别、解调、采集存储等功能;根据显示与控制系统的控制指令,完成信号处理算法参数的设置和数据存储、读取和管理等功能。

图1 数字相控阵信号侦察系统总体框图

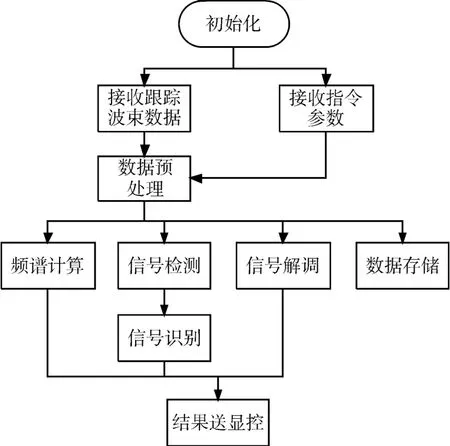

接收处理平台的工作流程如图2所示,工作流程采用数据驱动的方式,将算法与流程控制逻辑分离,这种流程处理方式可以极大地提高系统软件的可靠性和可移植性。信号处理平台接收数字相控阵发送的波束数据,根据接收的指令参数进行数据预处理,并将算法相关的参数添加到预处理后的数据流,后续的信号分析算法从数据流中解析出算法所需参数,完成频谱计算、信号检测、信号识别、信号解调和数据存储等功能。

图2 信号处理平台的工作流程图

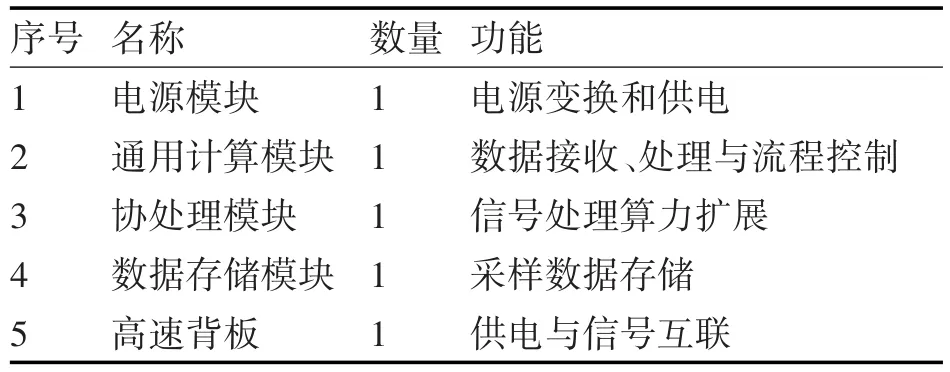

通过上述对信号侦察处理系统功能和工作流程的分析,设计了一种信号侦察处理平台,处理平台的主要设备组成及功能见表1。

表1 处理平台的主要设备组成

2.2 主要功能设计

接收处理平台采用通用化、综合化的设计思想,选用19寸上架机箱,采用VPX总线模块,并通过高速背板进行互联。VPX总线模块是基于VPX总线的一类模块,模块标准包括VITA46、VITA48、VITA62、VITA65等一系列标准,分别规定了模块的结构封装、网络传输协议和电讯接口形式等[7]。模块之间的互联可以采用Serial RapidIO、PCI Express、Fibre Channel、InfiniBand、Hyper-transport、10GB以太网等高速串行总线,能够适应现代雷达领域处理功能繁多、运算复杂、数据量大及高速实时处理的要求[7~8]。

通用计算模块是整个信号侦察处理平台的控制中心和处理中心,同时具有计算密集型和IO(Input and Output,输入和输出)密集型的特点。FPGA的并行处理能力,在实现高速通信接口、大规模数字信号处理方面具有显著的优势[9~11],但在复杂逻辑上的开发和处理上又有复杂、调试困难的特点,因此通用计算的处理架构采用FPGA+CPU的架构,FPGA负责处理计算密集和实时性要求高的计算,复杂流程的控制由CPU进行处理。比如,FPGA负责外部接口的数据通信、数据的预处理、频谱计算和信号解调等,CPU负责指令接收分发、任务控制、信号检测等。

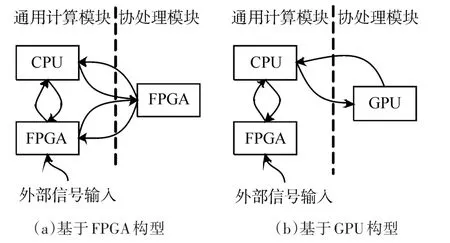

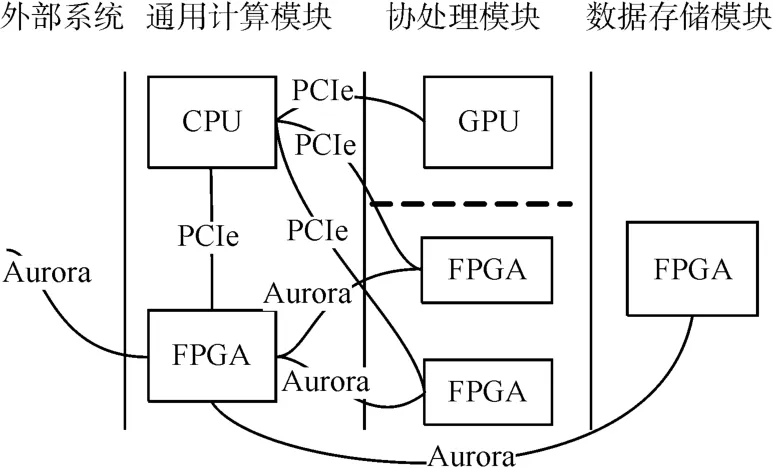

受限于VPX板卡的尺寸和功耗限制,单模块的信号处理能力可能无法满足信号处理算法的计算需求,设计采用增加协处理模块的形式用于信号处理算力的扩展。协处理模块的设计有基于FPGA和基于GPU两种构型,基于FPGA的构型至少支持2片FPGA,两种构型的数据流图如图3所示。基于FPGA构型的协处理模块与通用计算模块的CPU和FPGA均有高速互联接口,数据流可以直接由通用处理模块的FPGA直接发送给协处理模块的FPGA,再由协处理模块的FPGA将结果直接反馈给CPU,减少了通过CPU进行中转的环节,可极大地减少处理时延;同时数据也可以由CPU进行调度,以满足对CPU控制紧耦合算法的应用。基于GPU构型的协处理模块,只能与CPU直接互联,数据需要通过CPU进行调度。

图3 协处理器数据流示意图

数据存储是信号侦察系统重要的组成部分,由于基于数字相控阵信号侦察系统的多波束特点,需要同时处理和存储多路信号的采样数据。目前高速、实时存储大都采用基于 FPGA 进行实现[2,12~13],处理平台同外部接口的处理器采用的也是FPGA,因此,数据存储模块的设计也采用FPGA实现对外接口,这样方便统一各模块间的互联标准。

2.3 高速总线互联设计

基于上述对模块功能的设计,方案采用了PCIe总线和Aurora总线。PCIe(Peripheral Component Express,高速串行计算机扩展总线)总线,采用了点对点串行差分传输,每个设备独享通道带宽,单通道数据传输速率可以达8Gbps(PCIe3.0),主要用于CPU与外部设备的互联和接口扩展。Aurora协议是Xilinx公司开发的一个免费、开放、可扩展、低成本、高带宽的高速串行链路层协议。它可以支持多路的光纤传输,灵活的扩展光纤链路的数量,实现通信带宽的无缝升级。同时,协议自带的信道初始化与时钟校正等功能有效保证了点对点传输的高速数据同步,能有效解决数据传输的瓶颈[14]。

通用计算模块中的FPGA与CPU之间采用8通道PCIe3.0标准的链路,支持2路×4或1路×8工作模式,总链路带宽单向8GB∕s;CPU与协处理模块采用1路16×模式的PCIe3.0接口,可以适配主流的嵌入式GPU板卡,同时支持2路8×模式的PCIe3.0接口用于与FPGA进行互联;FPGA与协处理模块、数据存储模块以及外部系统接口采用Aurora总线,其中与协处理模块设计3路×4或1路×4加1路×8工作模式;与数据存储模块和外部系统均采用1路×8、2路×4或8路×1工作模式。逻辑框图如图4所示。

图4 高速总线互联关系示意图

3 关键技术

3.1 高速通信接口协议转换

通用计算模块对外部系统、协处理模块的FPGA以及数据存储进行数据读写时,涉及PCIe协议向Aurora协议的转换问题,主要有两个难点:一是需要实现单路PCIe接口与多路Aurora接口之间的数据路由;二是CPU端软件的运行受操作系统调度、缓存机制等因素的影响,无法实现带宽稳定的数据接收。

数据路由问题的解决设计采用了PCIe总线协议 XDMA(DMA∕Bridge)多通道的功能[15~16]。XDMA是Xilinx公司提供的高性能DMA IP核,具备AXI Stream接口、AXI LITE接口和AXI4 Memory Mapped接口三种用户接口。XDMA最多可以配置为4个H2C通道和4个C2H通道,共8个独立的DMA通道。这些DMA通道可以映射为AXI Stream接口,也可以通过AXI4 Memory Mapped接口进行交互。在基于Linux操作系统的环境下,设备驱动程序会生成c2h、h2c、control、user、bypass、events*等设备文件,不同的Aurora通道映射为不同的c2h、h2c设备文件,应用程序可以通过这些设备文件读写实现数据的收发。

数据接收端与数据发送端速率不匹配问题的解决,采用了缓存机制和PCIe、Aurora总线协议的流控机制[17~18],通过采用FPGA外挂的大容量DDR实现FIFO进行数据的缓存,CPU无法及时读取的数据暂时缓存在FIFO中。实现原理示意图如图5所示。

图5 高速通信接口协议转换逻辑框图

3.2 统一应用程序编程接口

应用程序与外部的交互接口主要有以太网、PCIe和CAN总线通信接口。以太网采用系统的标准Socket编程接口。PCIe和CAN虽然也是标准的总线,但由于PCIe接口设备需要完成PCIe总线与Aurora总线数据转换和分配;标准CAN总线每次只能发送8个字节的有效数据[19],发送超过8个字节的数据是需要应用程序进行封包和拆包,对这些接口的操作会存在不同的实现方式。因此,根据接口逻辑的实现方案和使用习惯,对业务无关的逻辑进行了封装,设计了统一的应用程序编程接口。

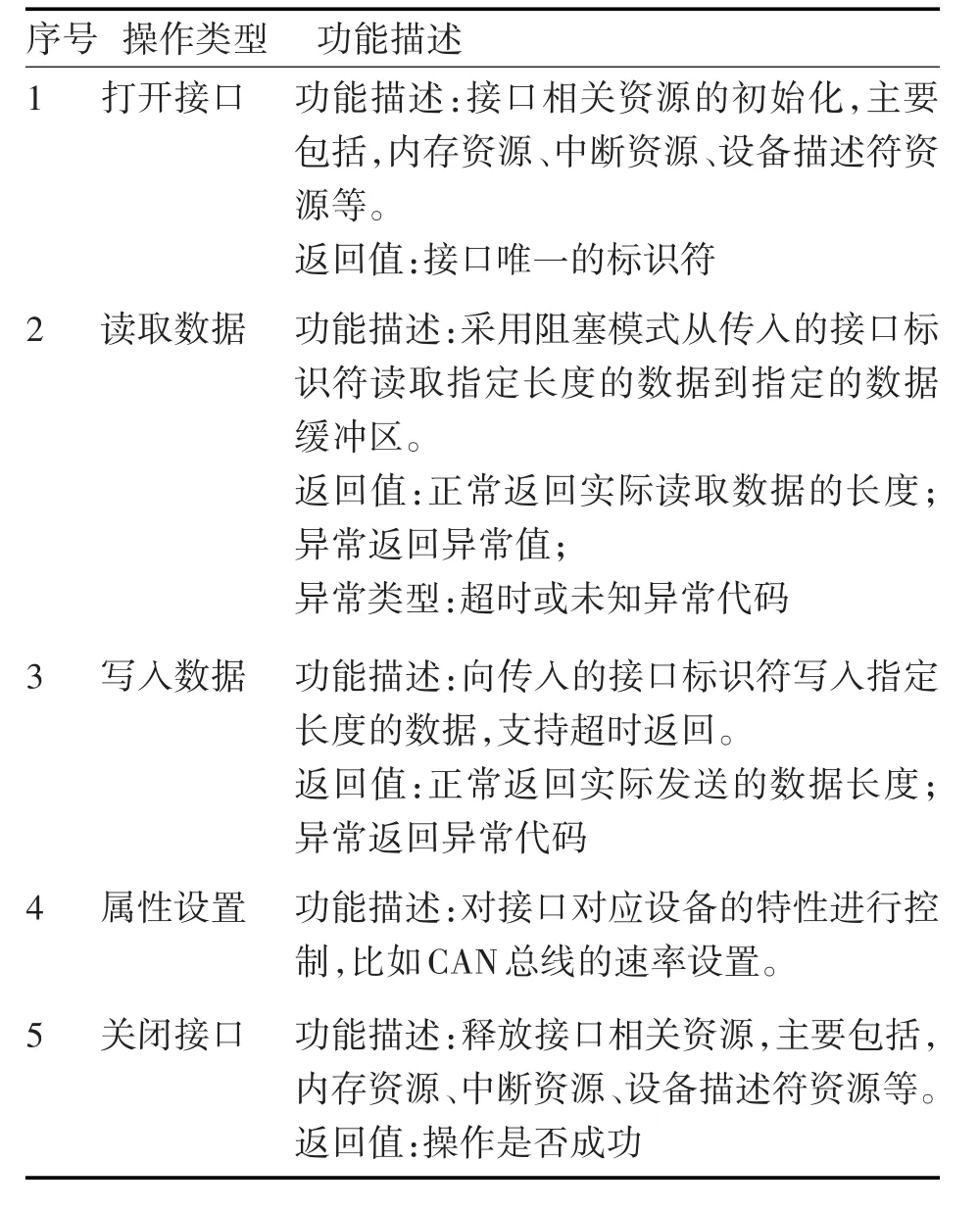

应用程序编程接口参考了Linux内核提供的标准系统调用,这些系统调用主要有open()、read()、write()、ioctl()、close()等[20~21],对应的功能分别是打开接口、从接口读取数据、向接口写入数据、接口属性设置和关闭接口等操作,编程接口的功能描述见表2。

表2 应用程序编程接口功能描述

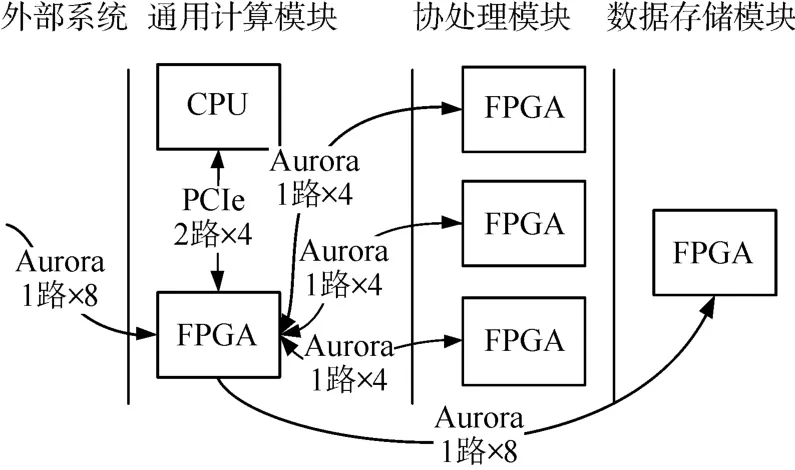

4 工程应用

目前,该信号处理平台已经在某遥测信号侦察系统和某信号处理平台项目中使用,采用的高速总线互联方案如图6所示。外部通过1路8x的Aurora接口接收相控阵天线的数据,经通用计算模块的FPGA接收,预处理后通过1路8×的Aurora接口发送到数据存储模块进行存储。通用计算模块CPU端的PCIe接口采用2路×4的PCIe接口,通过板内的FPGA扩展3路×4的Aurora接口,分别连接到协处理模块的3个FPGA,其中1路PCIe接口对应1路Aurora接口,另1路PCIe接口对应2路Aurora接口。通过项目开发团队的使用表明,统一应用程序编程接口的引入,解耦了业务软件开发人员与接口驱动开发人员的研发工作,团队间可以独立的进行功能测试和优化,提高了项目开发效率。经性能测试,通用计算模块CPU通过PCIe接口读取外部输入数据的速率约为1.3GB∕s,满足任务系统要求。

图6 某信号处理平台高速总线互联关系示意图

5 结语

本文通过分析了基于无源数字相控阵体制的信号侦察处理架构和流程,提出了一种信号接收处理平台的设计方法。经项目实际使用测试和验收,该信号处理平台满足工程使用要求,验证了设计思路是实际可行的。同时,高速接口的驱动由于底层缓存链表的大小受限于操作系统固定的页大小,接口通信数据带宽距离理论带宽还有很大的差距,后续如何进行优化还需要继续研究。