小像元10μm中心距红外焦平面读出电路设计

2021-10-08吴圣娟姚立斌李东升姬玉龙杨春丽李红福许睿涵

吴圣娟,姚立斌,李东升,姬玉龙,杨春丽,李红福,罗 敏,李 敏,许睿涵

(昆明物理研究所,云南 昆明 650223)

0 引言

红外探测器有广泛的应用前景,从军事角度来说,红外探测技术应用于侦察、监视、精确制导、搜索跟踪系统和光电对抗等领域,从民用角度来说,红外探测技术应用于安全生产、安防、消防等领域。这些领域的需求,促进了红外探测技术的不断发展[1-6]。小像元红外探测器推动先进技术,各个红外探测器厂商都在加紧高质量小像元探测器的研制工作[7-11]。小像元红外探测器组件具有如下优势:因其空间分辨率高,因此有着较好的图像成像质量以及系统识别能力;随着HgCdTe 芯片尺寸减小,可以降低组件的体积和重量,有助于红外探测器在整机上的应用[12-13];根据约翰逊判据(Johnson Criterion),阵列规模变大有助于提高目标探测器的可信度[14-15]。

在红外焦平面探测器的广泛应用背景下,读出电路技术得以不断发展,随着集成电路工艺水平的提高为更高性能读出电路的实现提供了可能。目前读出电路的研制方向如下:1)大面阵小像元。随着第三代红外探测技术的发展,焦平面的面阵规模越来越大,而单元面积越来越小,在此背景下增加了大面阵小像元读出电路的需求。2)双色及多色工作。由于红外系统应用的需求,双色及多色红外焦平面快速发展,未来多色红外焦平面读出电路也一定会有广阔的发展前景。3)数字化读出电路。数字化读出电路将ADC 芯片集成到读出电路中,读出电路直接输出数字信号,极大地方便了后续成像工作。

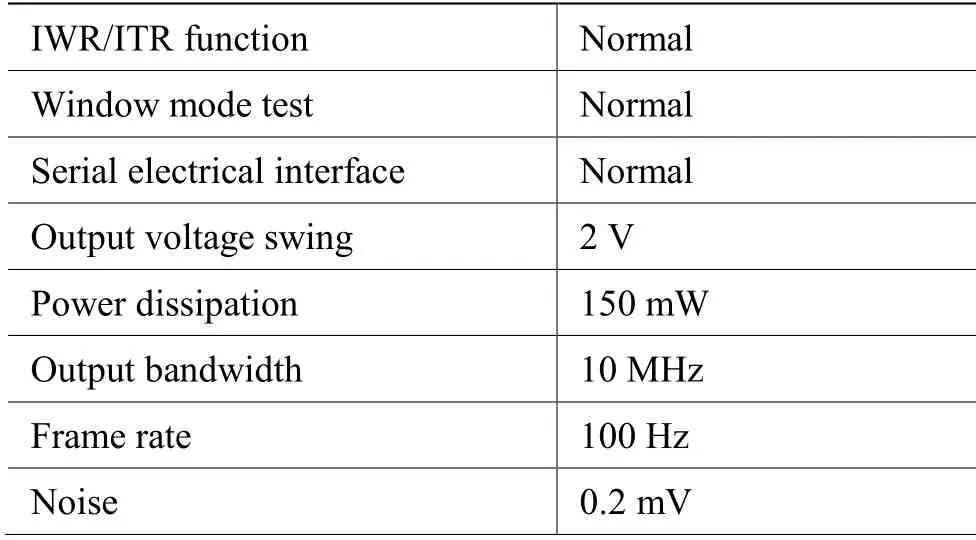

国外厂商近年来报道的大面阵、小像元ROIC 的研制进展如下:法国Sofradir 公司报道了大面阵、小像元读出电路,阵列规格1280×720,像元中心距为10 μm,应用波段为中波[16-20];美国雷神(Raytheon)公司报道了3 款大面阵的读出电路,阵列规格2 k×2 k,像元中心距分别为25 μm、20 μm 和15 μm,应用波段为短波和中波[21];美国TIS 公司报道了大面阵、小像元读出电路,阵列规格4 k×4 k,像元间距10 μm 和15 μm,卷帘曝光模式,应用波段为短波[22-24]。其中,Sofradir 公司研制的1280×720 的读出电路具体指标如表1所示。

表1 法国Sofradir 公司推出的Daphnis 产品信息Table 1 Daphnis product information by Sofradir

本文设计了一款大面阵、小像元读出电路,阵列规格1024×768,像元中心距10 μm,读出电路适配碲镉汞(MCT)中波红外焦平面探测器,组件工作温度77 K。电路设计两档增益,具备IWR(integration while reading)/ITR(integration then reading)功能。本文重点分析了小像元在比较小的保持电容情况下,电路抗干扰能力;重点分析了器件测试过程中产生的盲元拖尾的现象,并针对拖尾现象给出了解决方案。

1 总体设计

1.1 读出电路总体框架设计

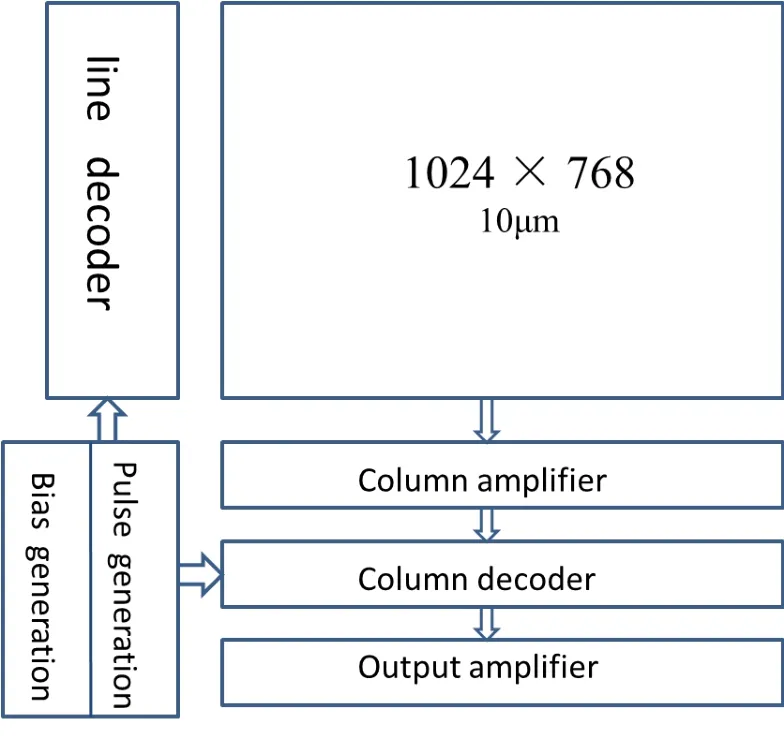

读出电路系统框架如图1所示,像元阵列、列级电路以及输出接口电路构成信号模拟通路。数字电路包括控制波形产生电路、行列译码电路。偏压模块产生模拟偏压,为列放大器以及输出放大器提供偏置。

图1 读出电路结构示意图Fig.1 Schematic diagram of readout circuit structure

1.2 信号模拟链路设计

我们设计的小像元10 μm 间距1024×768 读出电路适配中波探测器,因此像元电路输入级选择直接注入DI(direct injection)结构。

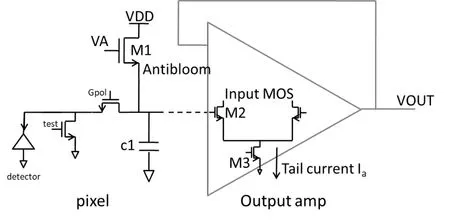

信号模拟链路原理图如图2所示,Gpol 管与探测器相连,通过调节Gpol 电压调节探测器偏置。antiblm 管是抗晕管,当电容电压降低到一定值后,抗晕管开启,此时电流是由电源VDD 提供,电容上的电压将保持不变。test 管是测试管,只用来验证读出电路性能,在正式杜瓦封装应用中,测试管是关断状态。信号经过列和输出放大器时,电压为1:1 传输。如图3为IWR模式像元开关时序图,在上一帧读出结束后,先将保持电容C上开关复位,并通过IWR 开关将当前帧的积分信息存到保持电容上。图4为ITR 模式像元开关时序图,可以看到,积分前电容复位开关与Gpol 开关有较长时间同时开启的状态,这个时间进行光电二极管的复位。

图2 模拟链路设计原理图Fig.2 Schematic diagram of analog design

图3 IWR 模式像元开关时序图Fig.3 Sequence diagram of IWR mode pixel switch

图4 ITR 模式像元开关时序图Fig.4 Sequence diagram of ITR mode pixel switch

1.3 读出电路主要性能参数

读出电路像元阵列1024×768,像元中心距10 μm,读出模式为IWR/ITR 模式,ITR 模式下增益有两档可调,电荷满阱容量为4.3Me-和1.6Me-。具体参数如表2所示。

表2 读出电路主要性能参数Table 2 Main performance parameters of readout circuit

2 像元电路抗干扰能力设计

电路像元中心距为10 μm,读出电路提供IWR模式,保证在积分时间较长的情况下,读出时间不占用帧频。由于面积限制,并且为了保证IWR 模式下的摆幅,保持电容C要做小,此时电容上的电压容易受到开关电荷注入、信号跳变的影响,抗干扰能力弱,在以下两方面应注意:

①沟道电荷注入效应对保持电容的影响;

②列放大器工作时,列总线电压的变化对保持电容的影响。

以下用定性及定量的方法分析以上两种干扰的影响,最后通过列表定量表征上述影响,并指导抗干扰能力因素和其他指标例如摆幅等的折中设计,以达到满意设计输出。

2.1 电荷注入效应的影响

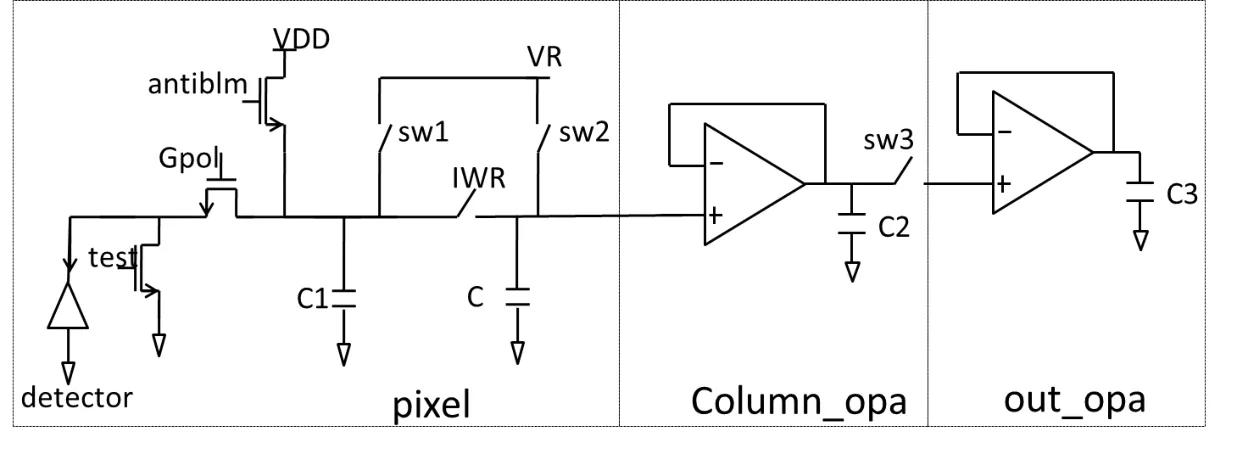

从图5可以看出,当Rst2 开关断开时,电荷从M1 沟道随机进入保持电容C上;当IWR 开关断开时,M2 与M3 沟道内电荷随机存入保持电容C上,引起保持电容电压变化。

图5 保持电容与开关连接图Fig.5 Connection diagram of holding capacitor and switch

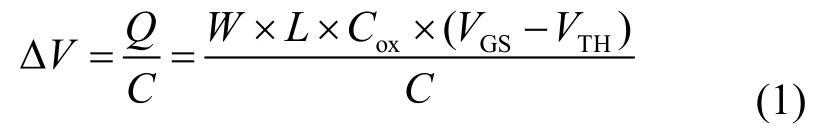

沟道电荷计算公式如(1)式所示:

式中:W与L为开关的宽和长;Cox为单位面积栅氧层电容;VGS为开关的栅源电压;VTH为阈值电压;C为保持电容。

在计算沟道效应前,将电路模型进行简化:

1)只考虑沟道电荷都注入保持电容上。根据模拟集成电路书[25]上的推论,沟道电荷注入的分配是比较复杂的过程,没有实际可用的预测经验,所以先以最坏的情况分析,即所有的沟道电荷都进入保持电容。

2)只考虑零光电流注入条件。M1 与M2 管都是PMOS,沟道电荷极性相同,电荷注入后电压叠加,而M3 是NMOS,电荷极性相反,电荷注入电压相反。定性分析时,只考虑最坏情况,即只考虑零光电流注入条件下,IWR 开关的沟道电荷注入。

下面计算沟道电荷注入,当电路工作条件如下:

式中:W/L为开关M1、M2 和M3 管宽长比;Cox为单位面积的栅氧电容;VGS为MOS 管栅源电压;VTH为MOS 管阈值电压。

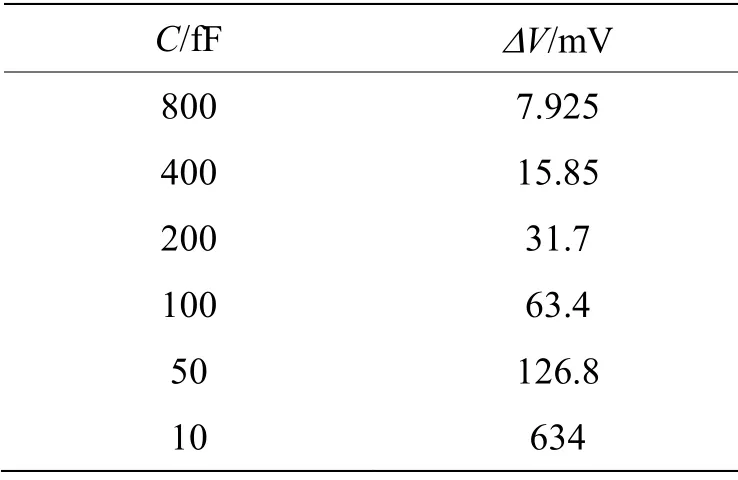

将上述条件代入(1)得:

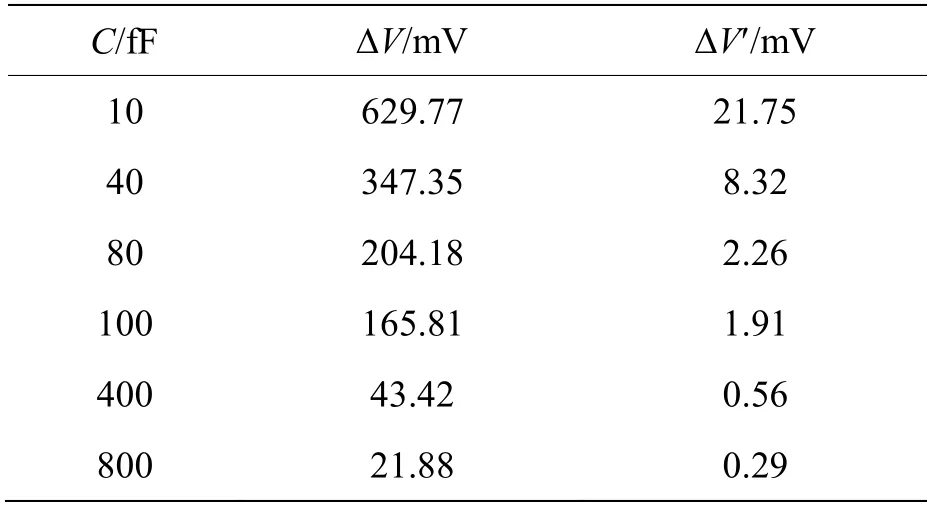

为方便比较,利用(2)式,将不同保持电容下引起的保持电容电压变化列表如表3所示,通过表3分析沟道电荷注入效应的影响。

表3是通过简单公式按照最坏可能计算出来的。从表3可以看出,小的保持电容对于沟道注入效应比较敏感,10 fF 电容下,沟道注入引起电压变化为0.6 V。

表3 沟道电荷注入效应引起的电压变化Table 3 Voltage change caused by channel charge injection effect

由于IWR 开关上的沟道电荷与像元电压有关,即与光注入有关,实际上每个像元的沟道电荷注入情况会不同,所以在小的保持电容下可能会引起成像后亮点和暗点的电荷注入效果不同。为了减小沟道电荷注入效应,应该将复位开关设计最小尺寸,尽量增加保持电容值。

2.2 列总线的影响

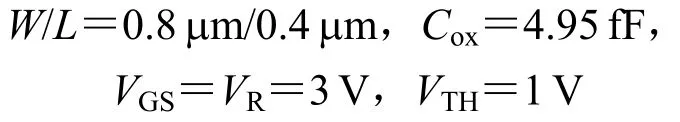

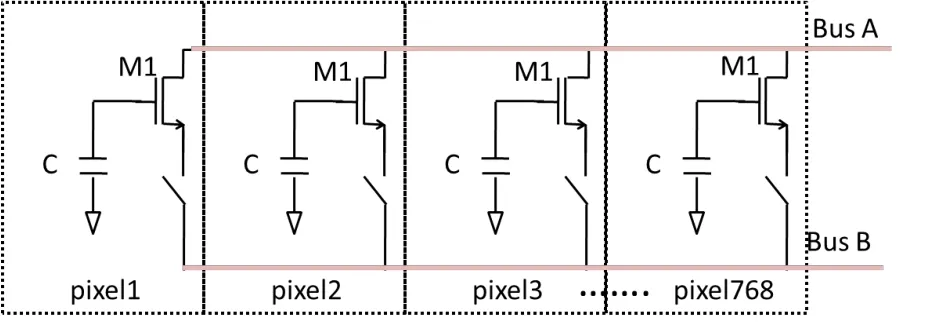

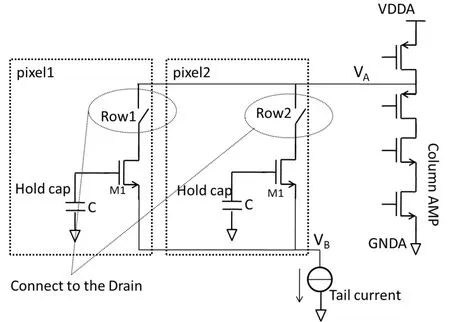

有两根长的信号导线从像元引出,如图6所示,接到列放大器,如所示的列总线A 和列总线B,768行共用一个列放大器,换行时,列放大器会根据像元电压的不同来调整列总线A 和列总线B 上的电压。通过M1 管的栅源电容的馈通作用,M1 管会将列总线上的电压变化引入到保持电容C上,引起像元电压变化。

图6 像元总线Fig.6 Pixel bus

下面通过行选开关的位置不同,定性地分析列总线的影响,然后通过仿真给出定量结果。

2.2.1 定性分析

行选开关的位置不同,列总线对保持电容的影响也不同,分两种情况分析:行选开关与M1 管漏极相连;行选开关与M1 管源极相连。

1)行选开关与M1 管漏极相连

这种连接方法对保持电容的影响相对较大。如图7所示,行选开关与列放大器输入管漏级相连。这种情况下,总线电压定性分析如下:

图7 行选开关位置1Fig.7 Location 1 of row selection switch

由于列放大器在换行时,VB总线可以有较大的变化,不考虑衬底偏置作用,最大变化可以为总的输出摆幅,并且VB与M1 管的源级相连,因此对保持电容影响大。

列总线对保持电容影响可由式(3)估计:

式中:W1与L1为M1 管的宽和长;Cox为单位面积栅氧层电容;∆VB为总线B 的电压变化。

2)行选开关与M1 管源极相连

这种连接方式,总线对保持电容的影响相对较小。如图8所示,行选开关与列放大器输入管漏极相连。在图8情况下,总线VB仍有较大幅度的变化,不同的是,M1 管的源极电压变化幅度小,只有VOD大小,通过式(4)估算列总线对保持电容影响:

图8 行选开关位置2Fig.8 Location 2 of row selection switch

由于VOD1远远小于∆VB,因此∆V′要远远小于式(3)中的∆V。

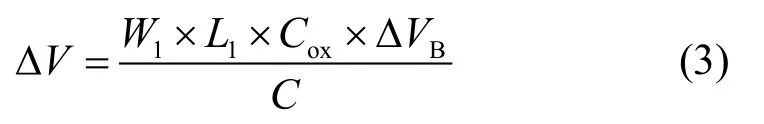

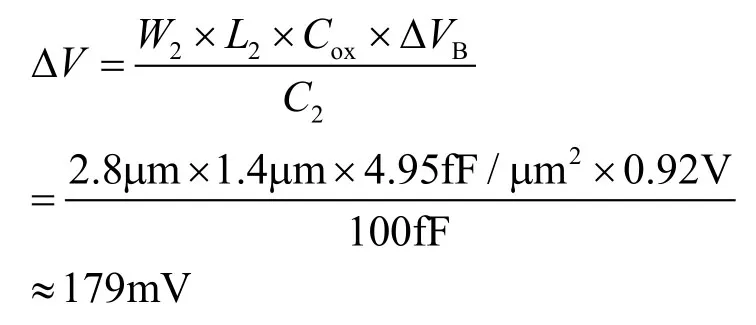

2.2.2 定量分析

通过仿真定量分析。仿真原理图如图9所示。仿真条件:

图9 列总线仿真原理图Fig.9 Schematic diagram of column bus simulation

1)保持电容C初始电压:VC1=2 V,VC2=3 V

2)(W/L)1=(W/L)2=2.8 μm/1.4 μm

3)Cox=4.95 fF/μm2

仿真时序如图10所示,初始状态为pixel 1 电容复位至2 V,pixel 2 电容复位至3 V,开关Row1打开,Row2 关闭。T2 时刻,切换行选开关,使Row2打开,Row1 关闭。通过仿真观察T2 时刻ΔV(pixel 2 保持电容跳变)的变化并记录结果。仿真结果如表4所示,当C=100 fF 时,行选开关连接至源极(∆V′=1.91 mV)比连接至漏极(∆V=165.81 mV)小约80 倍,因此从结果来看,行选开关连接在源极时影响远远小于连接在漏极的情况。

图10 馈通效应仿真时序Fig.10 Feed through effect simulation timing

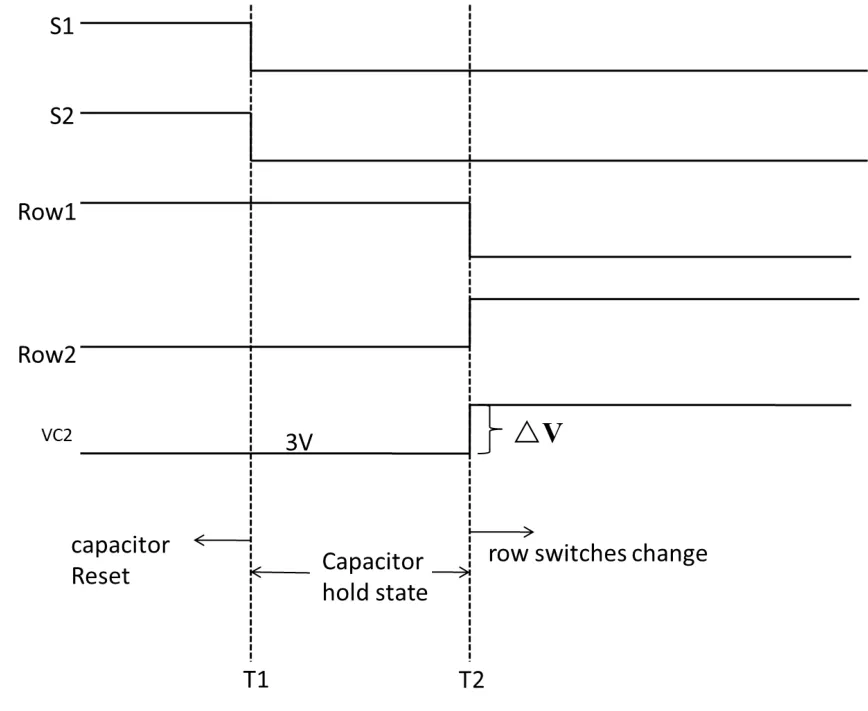

使用公式(3)计算开关位置1 时理论值,例如,当保持电容为100 fF,代入式(3),计算如下式所示:

仿真结果如表4为166 mV,比较接近,可以证明在400 fF、800 fF 时,公式计算值与仿真结果都比较接近,但是随着保持电容C的减小,很多小的寄生电容不能忽略,此时公式计算开始有偏差,公式计算只能粗略得到数量级正确的结果,准确结果需要仿真确认。

表4 列放大器对保持电容影响Table 4 Effect of column amplifier on holding capacitance

行选开关与M1 的源级相连,也有其折中考虑的地方。例如,频域分析时,行选开关工作在线性区,相当于在源级增加一个电阻,电阻上的压降会降低放大器的增益,而主极点是Rout×Vout不变,即带宽不变,从而导致增益带宽积降低,表现为仿真时放大器开环增益交点向原点移动的现象,此时放大器的相位裕度增加。但是由于增益带宽积的降低,当有阶跃信号输入时,放大器小信号响应时间也会增加。一般列放大器的速度为1 行数据读出的速率,60 kHz 左右,因此给放大器足够的响应时间,目前测试情况来看,没有看出列放大器响应时间引起的相关的问题。

对于保持电容在20 fF 以下的电路,除了上述分析,还应考虑保持电容在较长读出时间下的漏电问题,这个数据很难通过仿真准确得到,需要电路实际测试。

3 盲元拖尾及解决方法

3.1 拖尾现象分析

读出电路通过倒装焊工艺与碲镉汞芯片连接,由制冷机降温至77 K,进行性能验证。

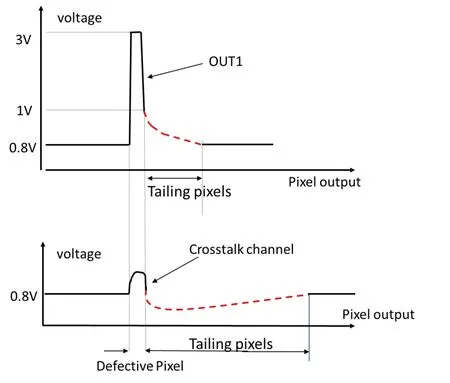

电路在测试时,灰度图上出现亮盲元拖尾现象。如图11(a)所示,当测试条件为ITR 模式,探测器器件有一个不会开启的盲元,探测器其余像元饱和,则不开启的盲元后续元存在拖尾现象。测试在IWR 模式下,没有盲元拖尾现象。

引起拖尾现象的原因:测试饱和值(0.8 V)超出输出放大器可处理范围,输出放大器电流驱动能力减小,不能及时响应,引起拖尾。

当抗晕管栅极电压调高时,增加饱和电压(调至1 V)亮盲元拖尾现象消失,如图11(b)所示。由于IWR模式下的摆幅1.2~3 V,因此这个摆幅范围内放大器工作正常,不会有拖尾现象。

图11 亮盲元拖尾现象Fig.11 Bright blind element tailing phenomenon

另外,从测试结果来看,拖尾不止一个通道,临近通道也被干扰,说明数据输出通道OUT1-OUT8 之间存在串扰;当某一通道电压大摆幅下降后,临近通道电压被拉黑(电压降低),而且随之几个输出周期都不能恢复,产生拖尾现象。

通过示波器可以看出,示意图如图12所示,输出放大器OUT1 从不开启的盲元电压(输出3 V),开始快速地下降到饱和电压值附近1 V 左右,然后很缓慢地降低到饱和电压值,拖尾现象是在电压缓慢降低时引起的。同时,被OUT1 串扰的其他通道也会下降,下降到饱和值以下,在缓慢上升过程中引起拖尾。图12中虚线区域为拖尾区域,此时运放处于接近截止的状态,电流驱动能力明显降低,不能快速响应变化,引起拖尾。

图12 拖尾现象分析Fig.12 Analysis of tailing phenomenon

3.2 抗晕管栅压设计

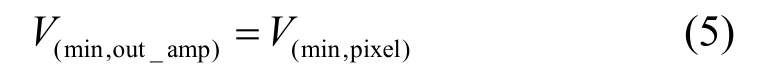

拖尾的原因是小于像元输出摆幅与输出运放所允许的摆幅不匹配所造成的,为了使输出放大器正常工作,并且不损失电路摆幅,设计应该保证:

式中:V(min,out_amp)为输出放大器允许的最小输入;V(min,pixel)为像元最小输出电压。

如图13所示,像元输出最小电压V(min,pixel)可以由抗晕管电压控制,抗晕管导通后像元电压为像元最小输出电压。设计目标转化为抗晕管栅极电压VA的设计,如图13所示,根据该图可以得出下式:

图13 抗晕管栅极电压设计示意图Fig.13 Schematic diagram of antiblooming voltage design

将(5)式代入(6)式得到:

式中:VGS2、VGS2、VOD3为M1、M2、M3 管的栅源电压和过驱动电压;VA为设计目标。

实际抗晕管电压产生电路如图14所示。M4 与M5 管交叉相连,M4 管的栅极接M5 管的漏级,M5管的栅极接M4 管的源级,VA为该模块输出电压,根据图14,可以得出式(8):

图14 抗晕管电压产生电路Fig.14 Antiblooming voltage generation circuit

设计保证(8)式与设计目标(7)式相等,设计思路如下:

1)VGS4=VGS1。设计使M4 管尺寸与像元抗晕管M1 管相同,M4 电流约等于(或稍大于)光电流,例如设计为Is=1 nA;

2)VGS5=VGS2。M5 管处在饱和区,M5 管尺寸与M2 相同,电流为输出放大器尾电流的一半,即电流值为Ia/2;

3)VDS6=VOD3。M6 管工作在线性区,M5 工作在饱和区,通过计算确定M6 管的宽长,使VDS6=VOD3成立。

根据上述描述,通过细化图各个MOS 管的尺寸,可以达到式(7)的设计目标,使像元输出电压摆幅等于输出放大器摆幅,以满足输出放大器的工作范围,避免拖尾现象。

4 电路测试及成像

1)中测杜瓦电路测试

在中测杜瓦内验证读出电路属于对电路的初步验证,电路验证包括IWR/ITR 时序、摆幅、功耗、输出数据的带宽、读出数据转化成灰度图的验证等。读出电路流片返回后,在中测杜瓦瓶内进行测试验证,利用液氮降温,通过读出电路测试系统来验证读出电路功能,像元注入由test 管完成,利用示波器波形来验证电路功能。通过实验验证,读出电路验证结果符合预期,测试结果如表5所示。

表5 读出电路测试结果Table 5 Read out circuit test result

2)探测器组件成像

探测器组件与图像处理电路和光学镜头集成,成像图15所示。

图15 小像元探测器组件成像图Fig.15 Imaging of small pixel detector assembly

5 结论

设计了一款小像元读出电路,阵列1024×768,像元间距10 μm。输入级采用直接注入结构,2 档增益可选,IWR/ITR 模式可选。实验表明:小像元条件下,设计ITR/IWR 模式可选,2 档增益,读出电路噪声为0.2 mV,帧频100 Hz,满足了大面阵、小像元探测器应用需求。本文重点分析了小电容的抗干扰能力、盲拖尾现象及改进方法,读出电路已经应用于中波1024×768 碲镉汞焦平面探测器,具备实用化的能力。同时,通过实测数据,将来可能以该款读出电路作为基础,制造出更大面阵更小像元尺寸的MCT 焦平面探测器阵列,满足小像元探测器的需求。