一种双速度传感器结合实现测速及定向的方法和实现

2021-09-26卡斯柯信号有限公司

卡斯柯信号有限公司 张 彬

本文介绍了一种列车测速系统及方法,列车测速系统包括两个同步运行的测速子系统,每一测速子系统包括速度传感器、可编程逻辑器件和CPU。通过冗余采样以及差异化的电路设计和信号处理方式,得到一个可靠测试结果。

在城市轨道交通应用中,列车对速度检测的要求越来越高,测速准确性和可靠性已经成为影响列车行车安全及运营性能的重要指标。列车本身的速度检测、闭塞区间控制、安全防护、制动控制、进站停车位置等功能都需要一个准确的测速结果。

1 整体设计方案

本文介绍的就是一种列车测速系统及方法,列车测速系统包括两个同步运行的测速子系统,每一测速子系统包括速度传感器、可编程逻辑器件和CPU。通过冗余采样以及差异化的电路设计和信号处理方式,得到一个可靠测试结果。

为了实现以上目的,本文介绍以下技术方案予以实现:

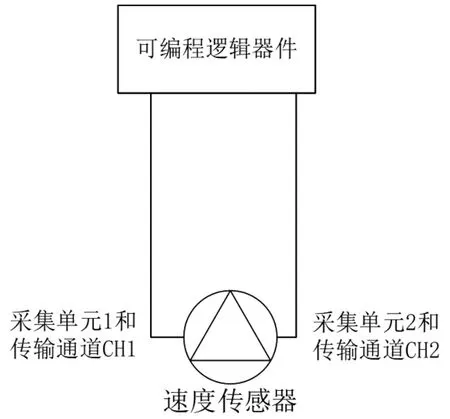

如图1所示,一种列车测速系统,包括两个同步运行的测速子系统,每一测速子系统包括速度传感器、可编程逻辑器件和CPU,所述速度传感器安装于列车车轮;

图1 列车测速系统的结构图

在每一测速子系统中,所述速度传感器用于采集车轮齿数并向所述可编程逻辑器件发送脉冲信号,所述可编程逻辑器件用于以第一预设频率采样所述脉冲信号以统计脉冲数量,并以第二预设频率对计数值进行锁存,所述CPU用于以所述第二预设频率获取所述可编程逻辑器件锁存的所述计数值,根据所述计数值计算所述列车的速度;

若在同一时刻两个所述CPU计算出的速度的误差在预设范围内,则判定测速结果无异常,并输出所述列车的速度。

为避免车轮打滑、空转、外部环境干扰等共因影响,两个速度传感器安装于列车的不同车轮上。并分别使用光电式速度传感器和霍尔式速度传感器。

在每一测速子系统中,速度传感器包括两个采集单元,分别通过独立传输通道向所述可编程逻辑器件发送脉冲信号,两个采集单元的脉冲相位差为90°之后可编程逻辑器件根据两路脉冲信号的脉冲相位差确定方向,正向则计数递增,逆向则计数递减。

可编程逻辑器件将每一路的计数值分别进行锁存,CPU获取可编程逻辑器件锁存的两个计数值。然后CPU将本次获取的计数值与上一次获取的计数值相比较,若计数值增大则判定列车为正向行驶,若计数值减小则判定列车为逆向行驶。

而在上述列车测速系统中,还需要对传输通道进行包括电磁兼容防护电路、滤波电路、比较电路、开关电路和隔离电路的设计:

(1)电磁兼容防护电路用于对所述采集单元送入的脉冲信号进行保护。

(2)滤波电路用于对所述脉冲信号中的毛刺和/或高频杂波进行过滤。

(3)比较电路用于对滤波后的所述脉冲信号进行比较。

(4)开关电路用于对比较后的所述脉冲信号开关控制。

(5)光耦隔离电路用于比较后的所述脉冲信号进行光耦隔离。

2 具体工作原理

一种列车测速系统包括两个同步运行的测速子系统,每一测速子系统包括速度传感器、可编程逻辑器件和CPU。如图1所示,测速子系统1包括速度传感器11、可编程逻辑器件12和CPU13,测速子系统2包括速度速度传感器21、可编程逻辑器件22和CPU23。

速度传感器11、12安装在列车车轮上,优选的安装于列车的不同车轮上,可以避免因单个车轮因出现空转、打滑等现象导致获取的速度与真实速度件产生较大偏差。速度传感器11、12是两种不同采集原理的传感器,例如分别为光电式和霍尔式,由于光电式传感器使用光感原理而霍尔式传感器使用磁敏原理,所以使用不同采集原理的传感器可避免由外部光或电磁干扰导致的两台速度传感器同时失效或误采集。

在测速子系统1中,速度传感器11用于采集车轮齿数并向可编程逻辑器件12发送脉冲信号,可编程逻辑器件12用于以第一预设频率A采样所述脉冲信号以统计脉冲数量,并以第二预设频率B对计数值进行锁存,CPU13用于以第二预设频率B获取可编程逻辑器件12锁存的所述计数值,根据计数值计算列车的速度;测速子系统2亦然,根据计数值计算列车的速度。若在同一时刻两个所述CPU计算出的速度的误差在预设范围内,则测速结果无异常,并输出列车的速度。

第一预设频率A与所述第二预设频率B比值大于等于1000。编程逻辑器件12、22分别向CPU13、23发送中断信号,通知CPU13、23进行处理。CPU13、23每2ms收到中断信号后,通过软件驱动分别从可编程逻辑器件12、22获得锁存的计数值,通过单位时间内的计数值来计算列车速度。CPU13、23的取值及清中断操作必须在1ms内完成,确保不会影响下一个2ms的中断信号通知。

由此,两个CPU13、23即可在同一时刻分别计算出列车的速度,进行相互比较,根据比较的差异结果进行分析,当比较误差在一定范围内时表示测速过程无异常,测速结果可接收使用。否则应采用要求重测、对外报警等措施,实施异常处理。

更进一步,速度传感器11具有两个采集单元分别采集齿数,两个采集单元的脉冲相位差优选为90°。图2示出了速度传感器的双通道连接图。可以理解的是,速度传感器中设置两个采集单元,可以实现冗余通道容错和纠错的目的。

图2 单个传感器的双传输通道

可编程逻辑器件12、22对两个采集单元发送的脉冲信号进行采样时,首先对两路脉冲信号的相位差进行解析,判断方向。由于两路脉冲信号的相位差φ固定,因此只要比较相位差φ是正还是负即可判断出方向,正向则计数递增,即计数值从0开始依次递增为正数,逆向则计数递减,即计数值从0开始依次递减为负数。然后,CPU13、23可分别将从可编程逻辑器件12、22获取的计数值与上一次获取的计数值相比较,若计数值增大则判定所述列车为正向行驶,若计数值减小则判定所述列车为逆向行驶。

传输通道包括电磁兼容防护电路、滤波电路、比较电路、开关电路和隔离电路;

采集单元送入的脉冲信号首先使用电磁兼容防护电路进行保护,通过使用以TVS管为主的电路连接采集信号和地信号,使得通过采集传输线缆直接注入和空间耦合注入的大能量冲击可及时泄放,对后级电路进行保护。

滤波电路可使用较为典型的LC滤波电路对输入脉冲信号中的毛刺和高频杂波进行过滤,便于后级使用。

在比较电路中,通过对15V的内部参考电压进行分压,将3.75V作为比较阈值,对滤波后的脉冲信号进行比较。脉冲信号送入反相输入端,参考电压3.75V送入同相输入端。当脉冲信号大于3.75V时比较电路输出0V,当脉冲信号小于3.75V时比较电路输出15V。

开关电路,使用NPN型三极管进行控制,比较器输出连接基级,三极管发射级接地,三极管集电极连接后级光耦的输入端负极。

光耦隔离电路,输入端正极连接15V的内部参考电压,输入端负极连接前级三极管的集电极,VCC和ENABLE均连接内部3.3V参考电压。因此在比较电路输出高电平时光耦输出0V,比较电路输出低电平时光耦输出3.3V。

最终送入编程逻辑器件的脉冲信号为3.3V内部脉冲信号。

采用上述速度传感器信号传输电路,可以对脉冲信号进行加强和隔离,增强信号容错性的同时,避免外部干扰通过传感器对内的传输线路引入设备内部。

结语:本文介绍的方法与现有技术相比具有以下优点:

(1)采用两个速度传感器结合各自的可编程逻辑器件及CPU组成两个测速子系统进行测速,将两个测速子系统的测速结果采用二取二原理进行比较,当两个测速结果的误差在预设范围内才表示测速结果无异常,如此可保证测速结果安全可靠。

(2)两台速度传感器分别为光电式和霍尔式,由于光电式传感器使用光感原理而霍尔式传感器使用磁敏原理,所以使用不同采集原理的传感器可避免由外部光或电磁干扰导致的两台速度传感器同时失效或误采集。

(3)两台速度传感器安装在两个不同车轮上,可以避免因单个车轮因出现空转打滑等现象导致获取的速度与真实速度间产生较大偏差。

(4)使用独立的速度传感器信号传输电路,对信号进行加强和隔离,增强信号容错性的同时,避免外部干扰通过传感器对内的传输线路引入设备内部。

(5)两个速度传感器的采集结果最终需要经过比较,当比较误差在一定范围内方可接收使用,否则应采用要求重测、对外报警等措施,实施异常处理。

(6)可编程逻辑器件可采用速度较低资源不多的CPLD或FPGA,CPU可以采用较低速度、低功耗的PowerPC或ARM系列CPU,整体方案价格便宜,且器件选择灵活度较高,成本低、实施便利度较高。