基于和图的电流型CMOS三变量通用逻辑门设计

2021-09-17姚茂群周传鑫李聪辉

姚茂群,周传鑫,李聪辉

基于和图的电流型CMOS三变量通用逻辑门设计

姚茂群,周传鑫,李聪辉

(杭州师范大学信息科学与技术学院,浙江 杭州 311121)

电流型电路具有高速、低功耗、带宽、设计方便、直观、易于实现多值逻辑电路等优点。阈算术代数系统的提出为电流型电路的设计提供了更符合电流信号运算特点的系统方法,而和图是将逻辑函数转化为阈算术函数的图形表示方法。本文在谱技术的基础上,提出了一种新的和图与谱系数图的转换方法,设计了一种基于和图的电流型CMOS三变量通用逻辑门,即三变量特征阈值逻辑门,可实现任意的三变量阈值函数。

和图;谱技术;三变量通用逻辑门;三变量特征阈值逻辑门

0 引言

阈值函数及实现相应运算的阈值逻辑门具有很强的逻辑功能和众多独特的优点,阈值逻辑门因与人工神经网络的基本单元——神经元具有相似的结构而广受关注[1-7]。

电流型电路以电流信号为参量,相比电压型电路,具有高速、带宽、失真小等优点。此外,电流信号易实现加、减等算术运算,在多值领域具有巨大潜力。通常,电流型电路的设计基于开关信号理论[8]、多值理论[9]、阈算术代数系统、和图[10-11]等,其中,基于阈算术代数系统及和图的方法更方便直观。

和图虽可用于电流型电路的设计,但缺少一种通用的逻辑门,通过改变其输入、输出的。本文在和图的基础上,通过对逻辑函数的探讨以及对通用逻辑门设计的研究,提出一种三变量特征阈值逻辑门设计方法,为电流型CMOS电路设计提供一种新的通用方法。

1 阈算术函数及图形表示

1.1 阈算术运算

阈算术代数运算包括阈算术运算、算术运算和非负运算[10⁃11]。阈算术运算的定义如下。

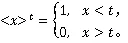

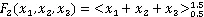

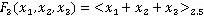

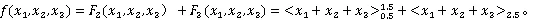

定义1 高阈算术运算:

定义2 低阈算术运算:

定义3 双阈算术运算:

另外,定义非负运算:

1.2 阈算术函数

阈算术代数系统的逻辑关系的解析表示称为阈算术函数。基于阈算术代数系统的基本运算可构成完备运算集。

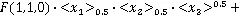

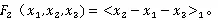

根据阈算术运算的定义,基值为2的三变量阈算术函数的规范展开为

1.3 和图

图1 三变量二值阈算术函数的和图

K图是和图的子集,其坐标与和图一致,不同的是和图在小格内,可填入除(0,1)外的其他自然数。通过和图进行阈算术函数运算,令电流型电路设计更加方便。

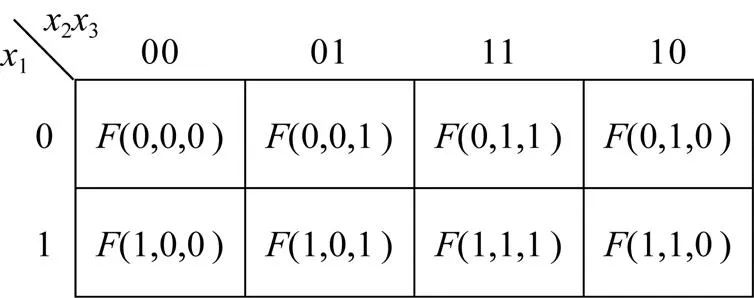

1.4 和图在电流型CMOS电路设计中的应用

图2 电流型CMOS电路的阈算术运算单元电路图

对应的和图分别如图3(c)和(d)所示。经和图间相互运算,可得

2 三变量特征阈值逻辑门设计

2.1 谱技术

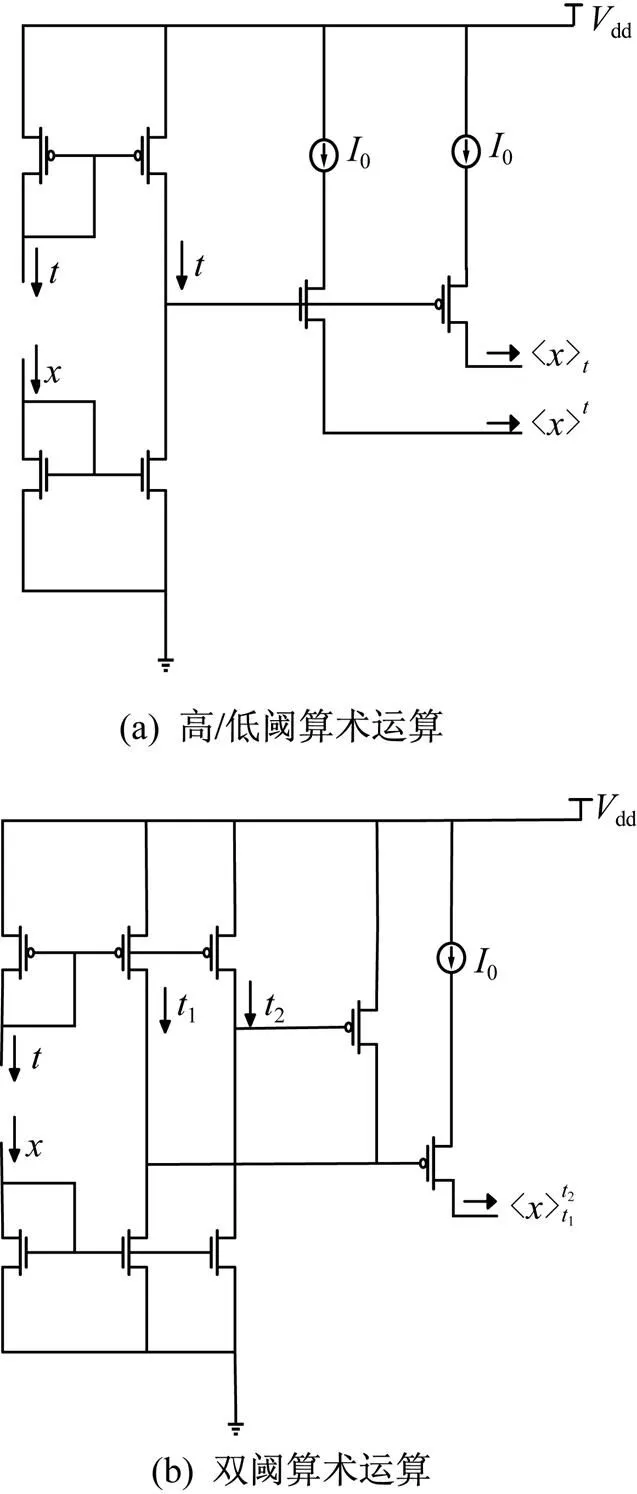

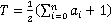

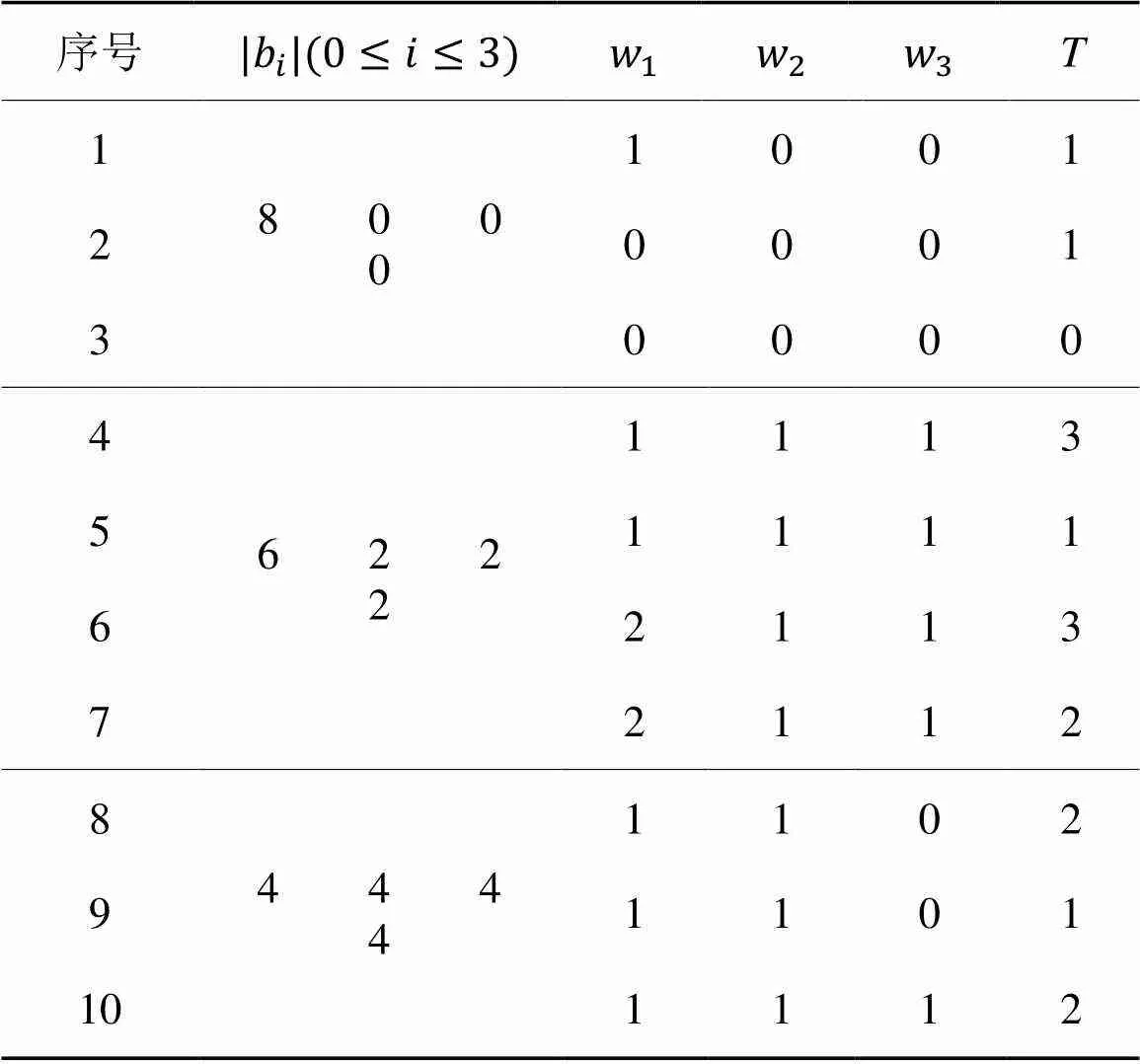

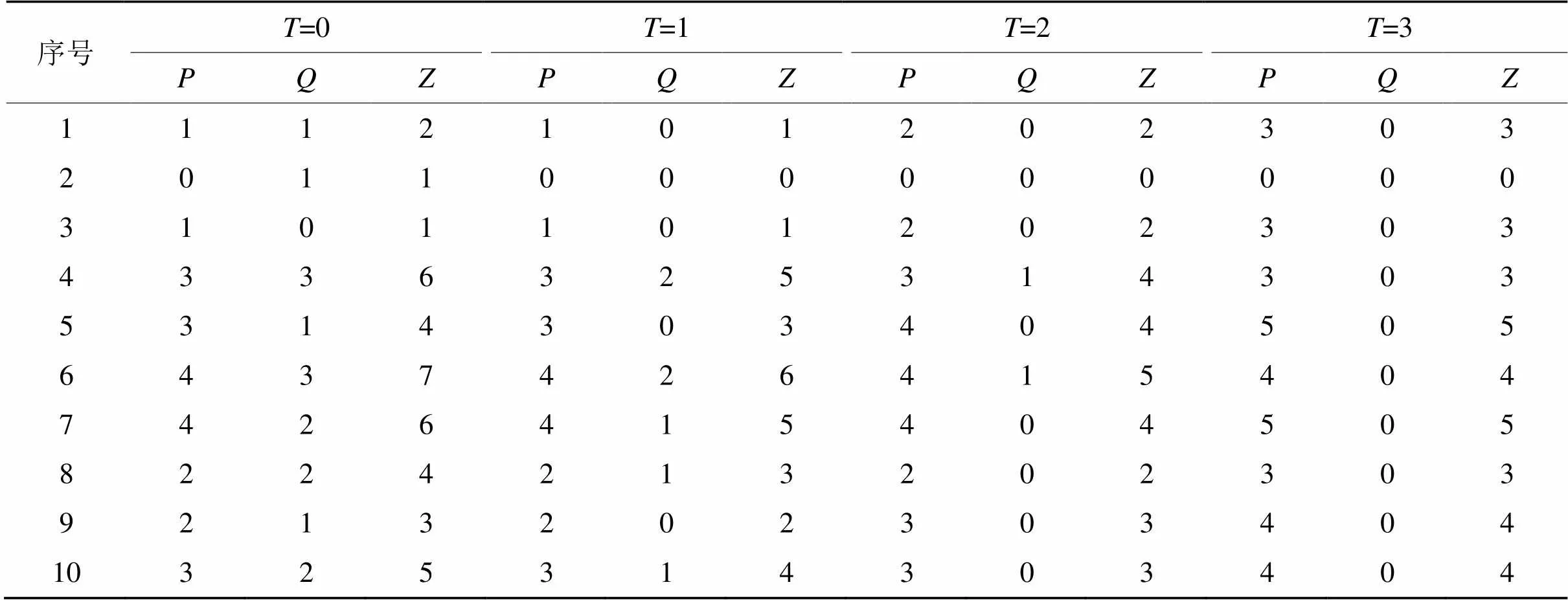

用谱系数对三变量逻辑函数进行分类,按逻辑函数谱系数的绝对值大小排序,若谱系数绝对值的最大值8或6出现在零次及一次谱系数上,或零次及一次谱系数的绝对值出现3个4,则该三变量逻辑函数为阈值逻辑函数[11,13]。表1为三变量逻辑函数按谱系数绝对值大小分类的结果,可分为3类。

图4 三变量逻辑函数的谱系数图

表1 三变量逻辑函数按谱系数分类

由文献[14]知,三变量逻辑函数按谱系数绝对值大小分类得到的三类函数中均包含阈值逻辑函数。

表2 系数与权值对照

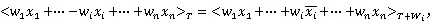

2.2 三变量特征阈值逻辑门

阈值逻辑门[11]是由个二值变量输入,单个二值变量输出组成的逻辑门,其输入、输出的关系可表示为

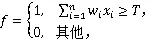

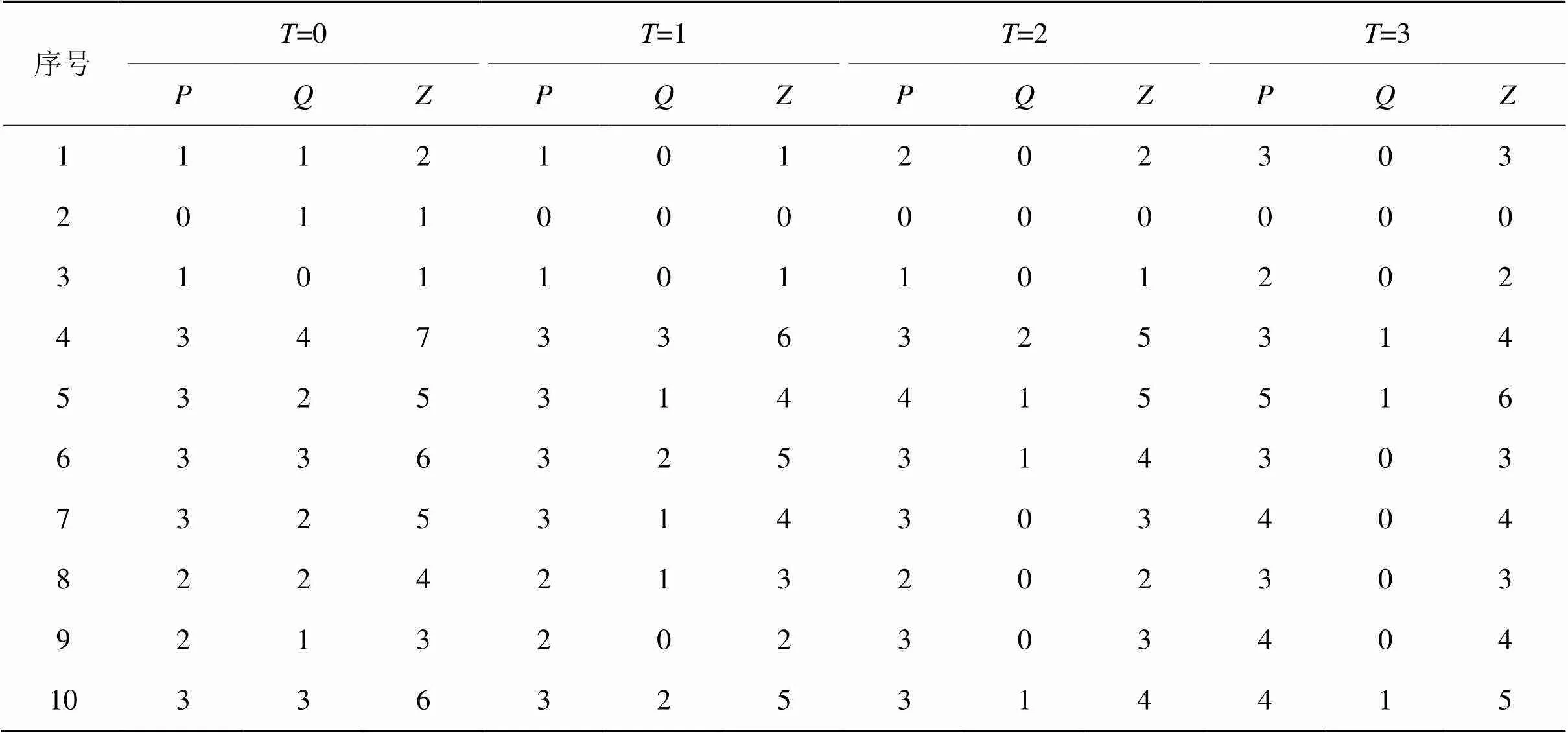

表3 三变量特征阈值逻辑函数

表4 当3个正权值输入端的权值为2,1,1时的输入端数量

表5 当3个正权值输入端的权值为1,1,1时的输入端数量

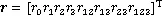

图5 三变量特征阈值逻辑门

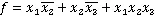

2.3 基于电流型CMOS三变量特征阈值逻辑门的三变量阈值电路设计

步骤如下:

步骤1根据所要设计电路的逻辑函数,作K图,即目标和图。

步骤2构造一个简单的高/低阈算术函数的和图,要求其含尽可能多的最小项,且尽可能趋向于目标和图。

步骤3再构造一个阈算术函数的和图,通过和图间的运算,使最终结果与目标和图相同。

步骤4将步骤3中阈算术函数和图的填入值做0→1,1→-1变换。

步骤6用谱技术求得相应的权值和阈值。

步骤7结合步骤3的图形运算过程及步骤6所得的权值和阈值,得到相应的阈值逻辑表达式。由基本阈算术单元电路,设计相应的电流型CMOS电路。

可得

所以

图6 电流型CMOS三变量特征阈值逻辑门

首先,利用卡诺图化简逻辑函数式,并变换为最简与非-与非表达式,得到

(3)净化过滤机。本项目通过消化、吸收、再创新,解决了通常管式过滤器钢衬胶骨架橡胶层弹性收缩易开裂等腐蚀问题,使得骨架寿命由半年左右延长至5年多,管式过滤器运行状况良好,综合性能指标大幅提升。其他类型过滤机各项技术指标良好,运行正常。

然后,画出逻辑电路图,如图7(a)所示。

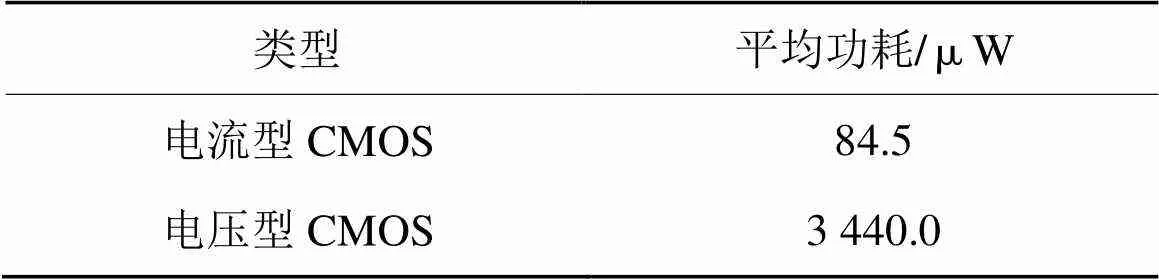

表6列出了2种不同类型CMOS电路的平均功耗。电流型CMOS电路的平均功耗为84.5 μW,相较于电压型CMOS电路的3 440 μW,具有更低功耗的优势。

表6 2类CMOS电路的性能比较

3 结论

给出了基于和图的电流型CMOS三变量特征阈值逻辑门设计,提供了一种和图与谱系数图的转化方法,给出了一种三变量通用逻辑门的设计方法,通过改变输入、输出接法,可实现任意的三变量阈值逻辑函数。同时,证明了电流型CMOS电路较电压型CMOS电路在功耗上具有显著优势。

[1]PANDEY N,GUPTA K,BHATIA G,et al. MOS current mode logic exclusive-OR gate using multi-threshold triple-tail cells[J]. Microelectronics Journal,2016,57(C):13-20.

[2]GHOSH A,JAIN A,SINGH N B,et al. Single electron threshold logic based Feynman gate implementation[C]// International Conference on Research in Computational Intelligence & Communication Networks. Kolkata:IEEE,2017:266-268.

[3]MAAN A K,JAYADEVI D A,JAMES A P. Supplementary material:A survey of memristive threshold logic circuits[J]. IEEE Transactions on Neural Networks & Learning Systems,2017,28(8):1734-1746. DOI:10.1109/TNNLS.2016.2547842

[4]FAN D. Ultra-low energy reconfigurable spintronic threshold logic gate[C]// Proceedings of the 26th Edition on Great Lakes Symposium on VLSI. Boston:IEEE,2016:385-388. DOI:10.1145/2902961. 290 2994

[5]DARA C B,HANIOTAKIS T,TRAGOUDAS S. Delay analysis for current mode threshold logic gate designs[J]. IEEE Transactions on Very Large Scale Integration Systems,2017(99):1-9.

[6]MAAN A K,JAMES A P. Voltage controlled memristor threshold logic gates[C]// 2016 IEEE Asia Pacific Conference on Circuits and Systems. Jeju:IEEE,2016,376-379. DOI:10.1109/APCCAS. 2016.7803980

[7]潘张鑫,马汝星,陈偕雄. 三变量通用阈值逻辑门的设计[J]. 浙江大学学报(理学版),2005,32(1):42-44. DOI:10.3785/j.issn.1008-9497.2005.01.011

PAN Z X,MA R X,CHEN X X. Design of three-variable universal-threshold-logic gates[J]. Journal of Zhejiang University (Science Edition),2005,32(1):42-44. DOI:10.3785/j.issn.1008-9497.2005. 01.011

[8]WU X,DENG X,YING S. Design of ternary current-mode CMOS circuits based on switch-signal theory[J]. Journal of Electronics,1993,10(3):193-202. DOI:10.1007/bf02684547

[9]TEMEL T,MORGUL A. Implementation of multi-valued logic gates using full current-mode CMOS circuits[J]. Analog Integrated Circuits & Signal Processing,2004,39(2):191-204. DOI:10.1023/b:alog.0000024066.66847.89

[10]张官志,姚茂群,施锦河. 和图及其在I2L电路设计中的应用[J]. 电路与系统学报,2011,16(6):94-98.

ZHANG G Z,YAO M Q,SHI J H. HE map and its application in the design of I2L circuits[J]. Journal of Circuits and Systems,2011,16(6):94-98.

[11]姚茂群,张官志,施锦河. 阈算术代数系统及多值电流型CMOS电路设计[J]. 电子与信息学报,2012,34(7): 1773-1778. DOI:10.3724/SP.J.1146.2011. 01185

YAO M Q,ZHANG G Z,SHI J H. Threshold-arithmetic algebraic system and design of multiple-valued CMOS circuits[J]. Journal of Electronics & Information Technology,2012,34(7):1773-1778. DOI:10.3724/SP.J.1146.2011.01185

CHEN X X,SHEN J Z. Modern Digital Theory[M]. Hangzhou:Zhejiang University Press,2001. DOI:10.1515/9783110506129

[13]姚茂群,沈继忠. 基于谱技术的电流型CMOS电路设计[J]. 杭州电子工业学院学报,2000(6):73-77.

YAO M Q,SHEN J Z. Design of current-mode cmos circuits based on spectral techniques[J]. Journal of Hangzhou Institute of Electronic Engineering,2000(6): 73-77.

[14]LU S L,ERCEGOVAC M. A novel CMOS implementation of double-edge-triggered flip-flops[J]. IEEE Journal of Solid-State Circuits,1990,25(4):1008-1010. DOI:10.1109/4.58294

Design of current-mode CMOS three-variable universal logic gates based on HE map

YAO Maoqun, ZHOU Chuanxin, LI Conghui

(311121)

Current-mode circuit has the advantages of high speed, low power consumption, wide bandwidth and easiness of realizing multi-value logic circuit. The design of the threshold-arithmetic algebraic system provides a systematic method for the design of current-mode circuit which accords with the operation characteristics of the current signal. HE map is a graphical representation of which transforms the logic function to the threshold arithmetic function, it is convenient and intuitive to use the map in the process of designing the current circuit. In this paper, based on the spectral technology, we present a new method to transform the HE map and spectral coefficient graph to design a three-variable universal logic gates: three-variable feature threshold logic gates about current-mode CMOS which realizes arbitrary three-variable threshold function.

HE map; spectral technology; three-variable universal logic gates; three-variable feature threshold logic gates

10.3785/j.issn.1008-9497.2021.05.007

TN 433

A

1008⁃9497(2021)05⁃565⁃08

2018⁃01⁃16.

国家自然科学基金资助项目(61771179).

姚茂群(1967—),ORCID:https://orcid.org/0000-0001-6484-4972,女,博士,教授,主要从事低功耗数字集成电路设计、智能控制、神经网络和模糊逻辑、物联网及应用研究,E-mail:yaomaoqun@163.com.