一款小型化高性能低通滤波器

2021-09-13陈依军

陈依军 袁 野

成都嘉纳海威科技有限责任公司 四川 成都 610097

滤波器是电路中一个重要的组成部分,尤其是在通信或是雷达系统中,对信号的频率选择性要求较高,如果滤波性能不佳,很容易导致信号串扰现象的发生,因此性能优异的滤波器可以改善整个系统的性能[1]。低通滤波器是容许低于截止频率的信号通过,但高于截止频率的信号不能通过的电子滤波装置。微带滤波器因其体积小、便于集成等优势,在现代微波通讯系统中被广泛使用,低通微波滤波器是雷达系统、通信系统、测量系统等必不可少的组成部分,一般被用来抑制器件产生的高次谐波和其它有源器件产生的高频噪音信号。文献[2]是基于切比雪夫函数原型,在微带短截线理论的基础上采用高低阻抗线方式设计的一款通带频率范围为0-6GHz的低通滤波器,通带内衰减小于3dB,在8GHz衰减大于20dB。该方法设计的滤波器一方面尺寸较大,过渡带较宽,另一方面由于相邻耦合线阻抗差距太大而导致不连续,带内插入损耗较大。文献[3]采用半圆型缺陷地结构单元和圆型阶梯阻抗并联枝节结构,设计出的宽阻带低通滤波器,3dB截止频率为2.7GHz,阻带为4-15GHz。该方法设计的滤波器在缩小尺寸的同时也提升了带外抑制性能,但设计加工较为复杂,对加工精度要求较高。文献[4]采用椭圆函数原型,设计了一款结构紧凑、插损小、过渡带陡峭的高低阻抗线微带低通滤波器,相比前面两款在尺寸和带外抑制性能上都有了不少提高。但是由于仍旧采用的是高低阻抗线方式,尺寸仍然相对较大,对目前越来越小型化的组件系统来说仍有很大弊端。

本文基于陶瓷薄膜工艺,采用7阶椭圆函数原型设计了一款结构紧凑的低通滤波器。陶瓷薄膜工艺采用Al2O3作为衬底基材,其介电常数达到了9.9,射频性能优异,尤其是温度系数很小,边带随高低温变化产生的温漂很小,非常适合现代微波射频器件应用。本文设计中将椭圆函数原型中的集总参数用分布参数直接代替,设计思路清晰明了。将串联电容、并联电容和并联电感用交指电容、平行板电容和细长微带线的物理结构分别替代,并进行全波仿真优化,最终设计了一款小型高性能该滤波器。通带频段为DC-3.5GHz,回波损耗<-16.5 dB,带内插损为<2.1dB,带外抑制度好,结构紧凑,尺寸仅为6.5×4.5mm2。

1 电路设计

滤波器的设计要求输入和输出阻抗均为50Ω,截止频率3.5GHz,通带波纹<0.2dB,阻带边带4.2GHz>35dBc。选取椭圆函数低通滤波器结构形式,要满足上述设计指标最少需采用7阶结构。7阶椭圆函数低通滤波器原型,如图1所示。查表获得椭圆函数低通滤波器的原型元件值:go=1.0,gL1=1.1726,gL2=0.6107,gL3=0.6906,gC1=0.9923,gC2=0.2380,gC3=1.2898,gC4=1.3153,gC5=1.0545,gC6=0.9385,gC7=0.5937。根据阻抗变换和频率变换,可得到实际LC原件值:C1=0.877p F,C2=0.211p F,C3=1.14p F,C4=1.163p F,C5=0.932p F,C6=0.83p F,C7=0.525p F,L1=2.592n H,L2=1.35n H,L3=1.527n H。

我们使用仿真软件ADS设计优化电路原理图,根据计算得到的L和C的理论值,经过仿真优化确定最终合适的数值,在此基础上着手建立分布参数模型。

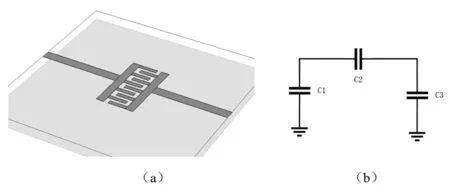

1.1 串联电容的设计 串联电容采用交指电容,如图2(a)所示,选用0.254mm厚度的Al2O3作为衬底基材,介电常数为9.9,损耗角正切为0.002,考虑到加工的可实现性,最小线宽设置为60um,最小线间距设置为60um。改变电容的方式主要有两种:(1)通过改变交指枝节的数目;(2)通过改变交指枝节的长度。采用电磁场仿真软件可以方便的计算出模型的电容值,但由于两边微带线寄生参数的缘故,其对地会寄生出到地电容,其等效π模型如图2(b)所示。以下图2(b)中C2电容为例,其两边的到地电容C1和电容C3就是由于结构本身的寄生参数引起的。通过观察图1低通滤波器原型可以发现,串联电容两边恰好有两个到地电容存在,寄生电容刚好可以作为两边到地电容的一部分存在。这种寄生电容的存在反而方便了电路本身的设计,可以减小两边电容的容值。

图1 椭圆函数低通滤波器原理图

图2 (a)交指电容模型;(b)交指电容等效电路

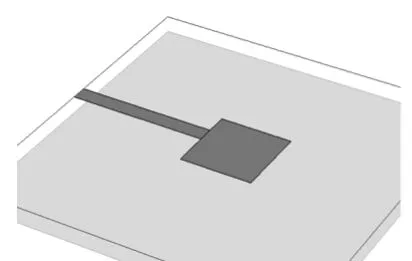

1.2 并联电容的设计 并联电容采用图3所示的平行板到地电容模型,由于衬底基材底部镀金,可与基板上表面的金属板形成并联到地电容。在4GHz以下由于边缘寄生影响较小,可以直接忽略,完全等效为一个到地电容。

图3 平行板到地电容模型

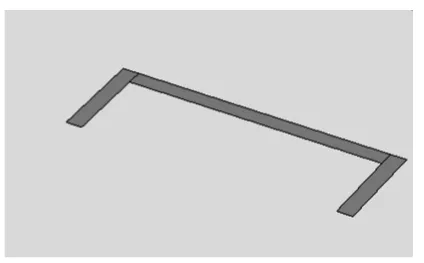

1.3 并联电感的设计 观察图1中低通滤波器原型中的电感值,发现其电感值很小,最大只有2.592n H。此种情况下电感可以直接等效为一段细的微带线。其模型如果4所示,通过电磁场仿真软件可以方便的得到所需的电感值。

图4 微带线电感模型

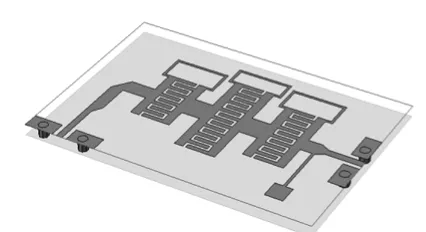

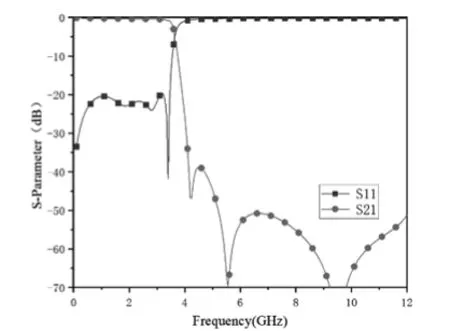

根据上述对串联电容、并联电容和串联电感物理模型的分析,可以方便得到各个原件的初值。但是从实际设计角度考虑,首先应该从中间电路元件开始,将C4的分布结构物理模型代入到ADS的滤波器模型中,然后重新进行优化。采用逐个元件进行替换的思路,这样才能保证设计的准确性和便捷性。采用此设计方法最终得到如图5所示的低通滤波器模型。图1原理图中的C1、C3和C5因为串联电容寄生到地电容的原因在优化中被直接省去。滤波器仿真结果如图6所示,滤波器的回波损耗都在-20dB以下,满足设计指标要求。

图5 陶瓷低通滤波器模型

图6 陶瓷低通滤波器模型仿真结果

2 低通滤波器的实物与测试结果

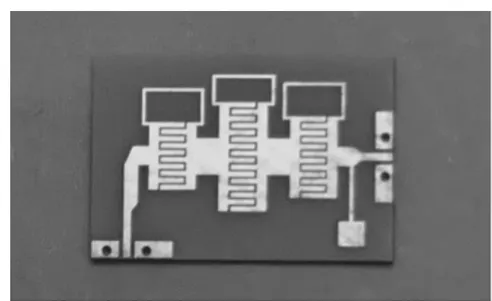

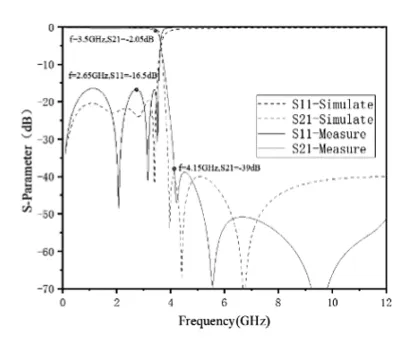

采用厚度为0.254mm的Al2O3陶瓷基板进行实物加工,其介电常数为9.9,损耗角正切为0.002,最终的实物加工图如图7所示。其测试结果如图8所示,在DC-3.5GHz通带内,回波损耗<-16.5dB,边带插入损耗<2.1 dB,带外抑制效果好,在4.15GHz>35 dBc,测试和仿真结果吻合的很好,满足设计指标的要求,滤波器结构紧凑,尺寸仅为6.5 mm×4.5 mm。

图7 低通滤波器实物图

图8 低通滤波器测试结果

3 结论

本文采用椭圆函数低通原型,基于陶瓷薄膜工艺设计了一款DC-3.5GHz小型化高性能低通滤波器,针对原理图首先给出了分布参数模型电容和电感的设计方法,通过采用交指电容、平行板电容和细微带传输线的方式分别实现串联电容、并联电容和并联电感结构,并重点分析了串联电容的π模型参数。在此结构中π模型两边寄生到地电容不仅影响整个电路的设计复杂度,而是可以直接等效到原型中的到地电容中去,有利于电路尺寸的设计减小。其次给出了整体电路模型的优化设计思路,应该首先从中间元件可以进行逐一替代,每替换一个元件都要对电路进行优化仿真,这样才能保证设计的准确性和便捷性。最后加工了实物,通过测试发现实物加工图的测试结果与仿真结果非常吻合,证明了设计思路的准确性。该滤波器结构紧凑、性能优良,具有很高的工程实践价值。