一种高效动态存储方法

2021-09-08余金清章伟王帆

余金清 章伟 王帆

【摘要】 在无线通信领域,处理器需要处理的数据量非常大,这给数据处理及相应的存储带来了很高的要求,特别是在基带领域,数据量能达到几十Gbps甚至更高,对存储提岀了更髙的要求。本文描述一种新型数据存储方式,能够有效缓解片外数据存储带宽需求,同时进一步提升数据传输效率并降低设备功耗。

【关键词】 动态存储 L3 Cache 共享缓存

一、问题提出

随着无线通信技术的发展,数据传输及处理的量越来越大。特别是在无线基带领域,在接收端,接收机(或基站)接收的无线信号,经过处理后,变成软比特数据,译码器( Turbo、LDPC)需要软比特数据译码成硬比特数据;这个数据量达到几十Gbps甚至上百Gbps,这给数据存储带来了很高的要求。特别是在数据译码错误情况下,需要进行HARQ重传然后再进行译码。在重传数据完成前,需要对之前译码错误的数据先存起来,然后和新接收的重传数据合并后再进行译码,译码完成后,再将硬比特数据回写到存储器中。如果译码不成功,需要再次重传,然后将新的译码错误数据和重传数据合并再译码。

如图1所示,考虑设计性能最大化,我们需要提供大量片外存储空间及带宽来满足一些极端场景,这就对硬件设计、成本、功耗提出了更高的要求。

二、解决思路

片内共享存储區( Share store:SST,以下简称SST),主要完成 modem数据的存储以及 PHY CPU与 PS CPU交互数据存储;其操作场景如下图2所示。

SST实现的是类L3 Cache功能,可以通过软件配置为 cache模式、RAM模式或者 cache和RAM同时支持的模式。在配置为 cache模式时, SST Cache实现与DDR内存空间的映射,modem硬件或者CPU软件通过AXI总线直接访问DDR内存空间,如果 cache hit,则 SST Cache完成DDR内存空间映射;否则cache miss,modem硬件或者CPU软件直接访问DDR若SST配置为RAM模式, modem硬件可以通过直连线接口或者AⅪ总线接口,软件通过AXI总线接口访问 SST RAM;RAM的地址空间由软件分配, modem硬件或者软件下发的地址为软件配置的RAM空间时,则操作到 SST RAM中,否则操作指令 bypass到DDR中实践情况。

三、实践情况

3.1实践框架

SST主要包括SST接口仲裁控制、 Cache控制管理以及存储管理等功能,系统划分如图3所示。

下面分别介绍各个模块和功能:

1. SST接口仲裁控制

将AXI总线送过来的操作进行接口适配处理,将AXI总线接口转换成内部自定义读写请求接口,然后在送给仲裁处理模块。通过AⅪ总线过来的操作模块包括PHY、CPU、 PS CPU、DMA、EDCP以及 modem硬件等。

仲裁处理,选择优先级较高的一个请求优先进行处理,优先级高低由软件配置下发,支持通过 AXI ID和地址空间两种优先级定义。

完成AⅪ端口仲裁处理后,完成不同子系统从AXI总线过来的读写处理操作的cache以及RAM操作模式判断;cache和RAM操作模式通过访问地址来判断,并给出每个地址空间的属性。

2. Cache控制管理 SST cache

SST cache完成 cache访问操作,该操作不支持写操作的 cache miss时,将现有 cache空间内的数据踢到DDR,并替换当前数据操作;支持读操作的 cache miss时,将从DDR中读出数据返回给源端请求的同时,将现有 cache优先级底的数据踢到DDR中。

如果判断该笔访问是需要 bypass到DDR,则直接将访问通过AXI总线发给DDR。

3. RAM存储管理 SST store

完成AXI总线过来的 cache、RAM访问的到对应RAM颗粒的读写选通操作。

完成自定义总线过来的RAM访问到对应RAM颗粒的读写选通操作。

3.2实践思路

1. Cache组相连映射关系

Cache与物理地址的映射关系,采用组相连的映射关系。

其中,W定义 Cache Line大小;U为 Cache的组号(Set);Ⅴ确定了 Cache有多少Way。

Cache的映射,就是S与Ⅴ之间的映射。

映射过程是,使用U查TAG表,得到多个Way的数据,每个Way内有S的值。

使用DDR地址的S数据,与TAG表内的多个way的S值比较,如果有相等的,就是命中,得到这个Way的I,作为V的值,组成 Cache的地址。

如果不命中,就涉及分配策略等。

2. 16Way的情况

SST的 Cache特性:

1) Cache为16Way,则V为4bit;

2) Cache Line为64Byte,W为6bit;

3)Cache Size为256 Kbyte,则U+V+W=18Bit,则U为8bit;

4)DDR物理地址空间为30bit,则S+U+W=30,S为16bit。

Cache的命中表,深度为256(使用U8bit为地址),宽度为16*16=256bit。命中检测使用U作为索引,一次读出256bit的数据,同时分析16个Way看是否包含有S的数值,如果有,则表示相同S的Way存贮该地址的数据。

四、效果评价

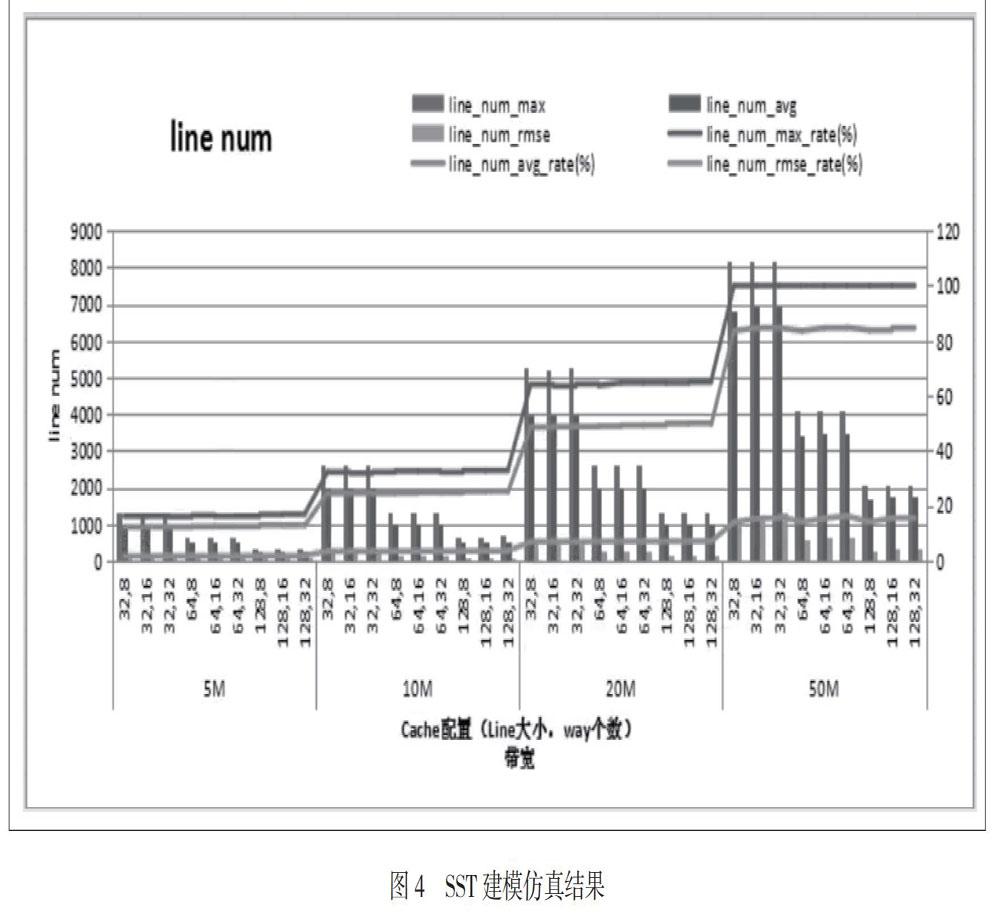

如图4所示,通过设置不同的流量模型,并对比在不同的line大小以及way数量后进行行为级仿真建模可知,SST功能能够有效减少数据对DDR的访问,从而减少处理器功耗提升能效比性能。