基于特高频传感器局部放电监测系统的FPGA设计

2021-09-07代少升赖智颖刘小兵

代少升,赖智颖,刘小兵,任 忠

(1.重庆邮电大学通信与信息工程学院,重庆 400065;2.重庆市信号与信息处理重点实验室,重庆 400065)

0 引言

在高压电设备中,由于绝缘老化等问题会伴随着放电现象,不加以预防,严重时会导致短路[1-3]。局部放电是反映高压绝缘设备故障的重要依据[4-5],局部放电检测方法有超声波检测、特高频检测、脉冲电流检测等,特高频检测法应用广泛[6-8]。特高频检测法和其他局部放电检测方法相比,具有检测频段宽、对噪声不敏感等优点[9-10]。在检测到的局部放电信号中,常会被各种噪声干扰[11-12],包括周期噪声、脉冲噪声和白噪声,其中白噪声最常见[13-14]。清华大学、重庆大学、西安交通大学等分别用不同的传感器和降噪分离方法研制出局部放电在线监测系统。随着各项技术的发展,对局部放电在线监测系统的实时性、准确性等要求越来越高。

本文基于特高频局部放电信号的在线监测系统的硬件实现,FPGA通过高速AD采集特高频局部放电信号,在FPGA上实现提升小波变换,将采集的信号进行滤波和提取脉冲信号,对脉冲波形提取特征量。FPGA具有并行处理、灵活性高等优点,适合高速数据采集及处理。提升小波变换具有计算量小、原位计算、易于硬件实现等特点。本文选取峰度偏度法对脉冲信号进行分离。这两种方法在脉冲波形上有统计特性并且易于计算,最终将特征值通过网口上传给上位机,上位机通过DBSCAN有效将不同类型的脉冲信号聚类分离。本系统充分利用FPGA的高速性能,将降噪和特征提取算法在FPGA上实现,有效提高上位机的实时性且能将不同脉冲类型分类。

1 监测系统

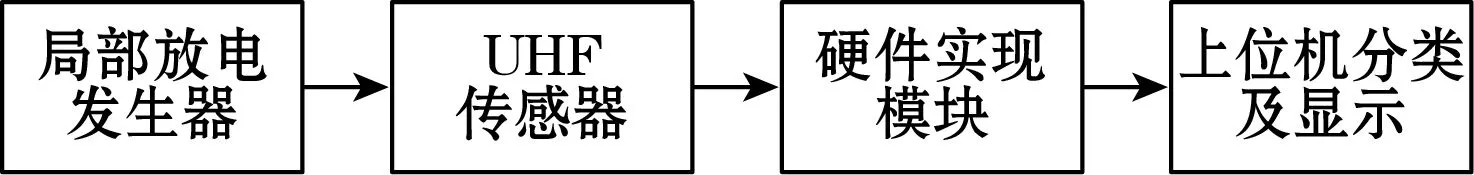

特高频局部放电监测系统主要由局部放电发生器、硬件实现模块以及上位机分类及显示模块组成,监测系统如图1所示。

图1 监测系统

局部放电发生器通过自制的绝缘缺陷模拟真实局部放电的发生,特高频传感器将接收的信号传给硬件实现模块。硬件实现模块主要由FPGA控制,AD采集数据后滤波和特征提取,将提取的特征通过网口发送给上位机,上位机通过DBSCAN分类算法对特征值进行聚类分离,将不同类别的脉冲分别显示PRPD (phase resolved partial discharge)图谱。

2 硬件实现模块

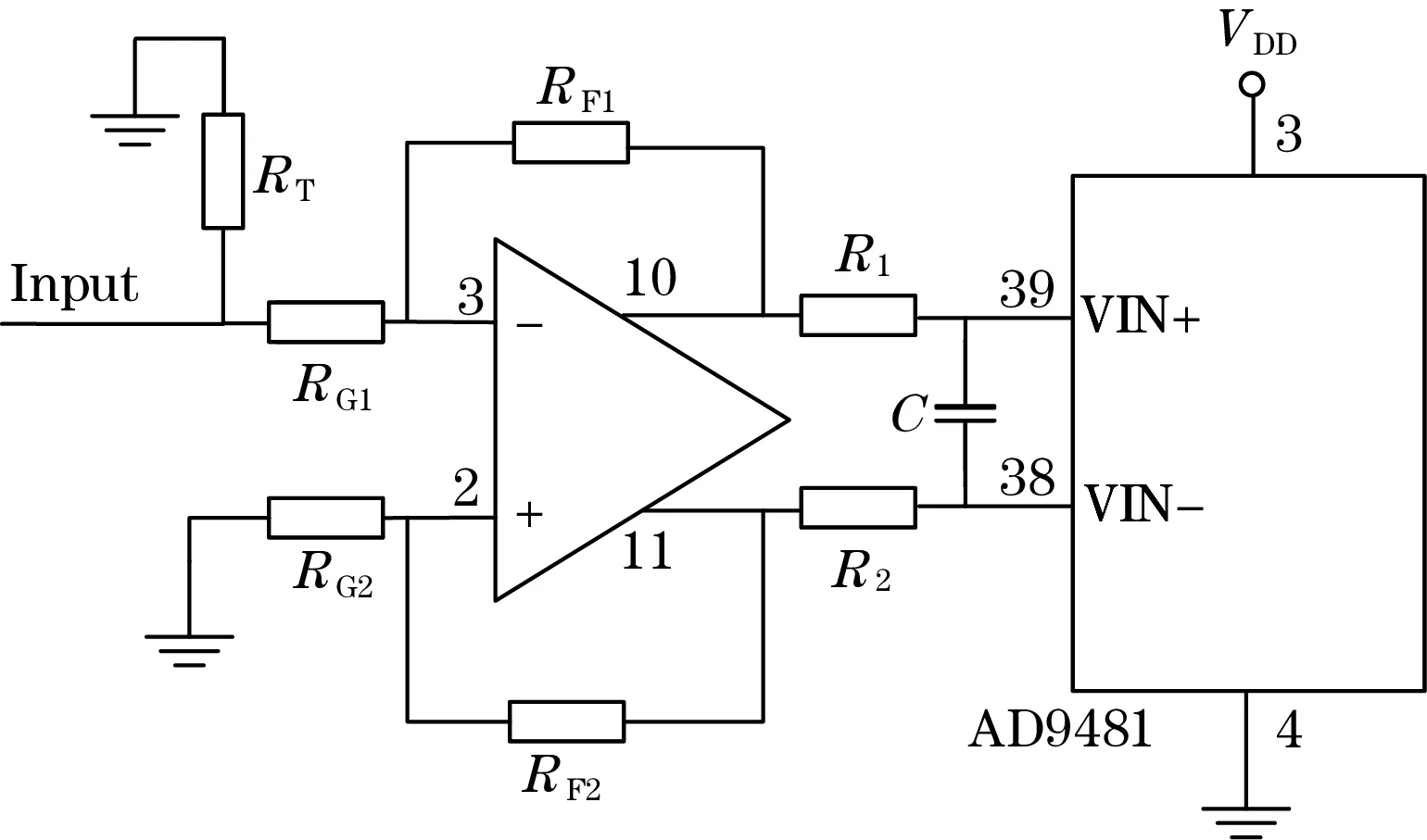

2.1 信号调理单元

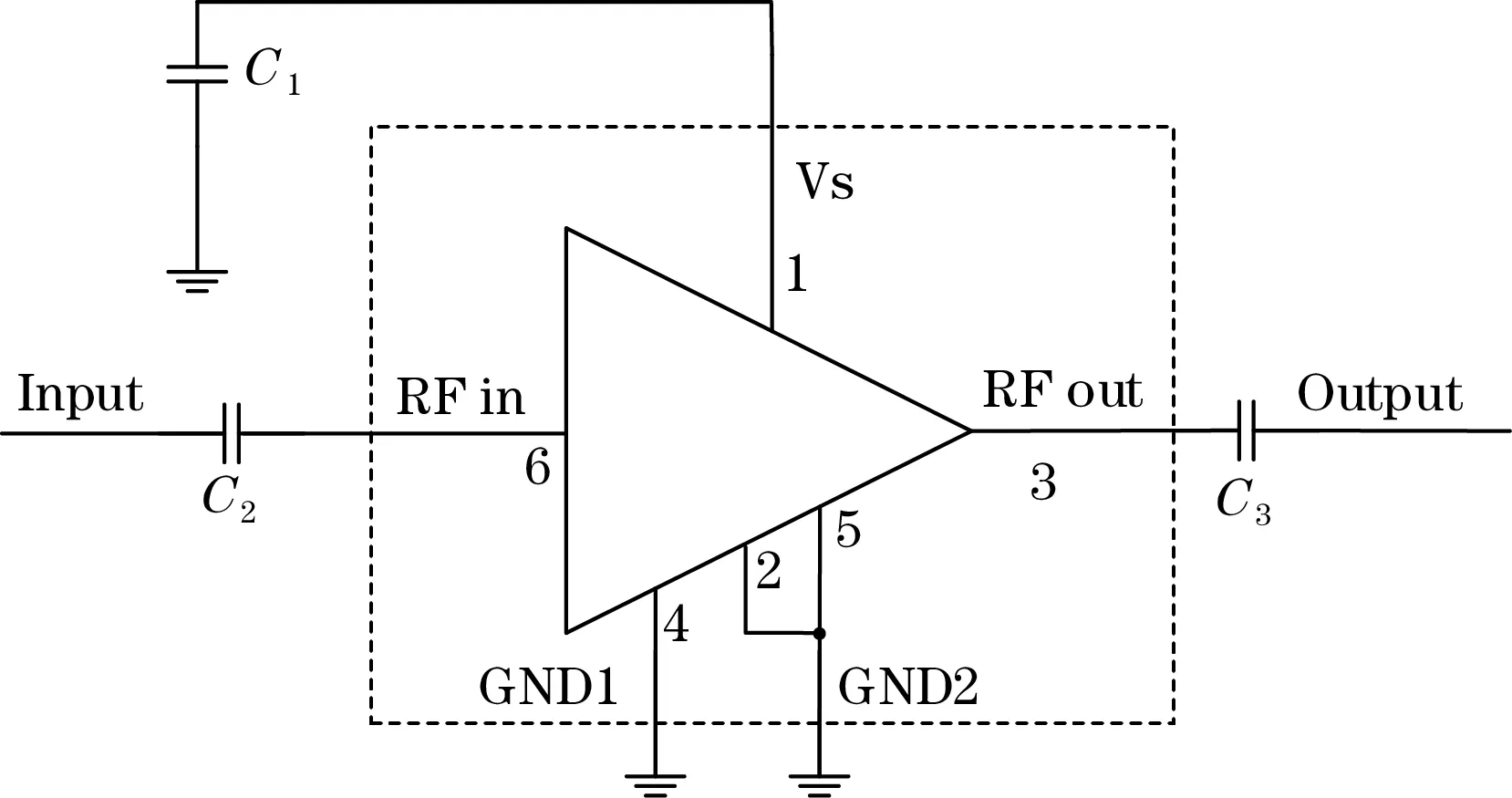

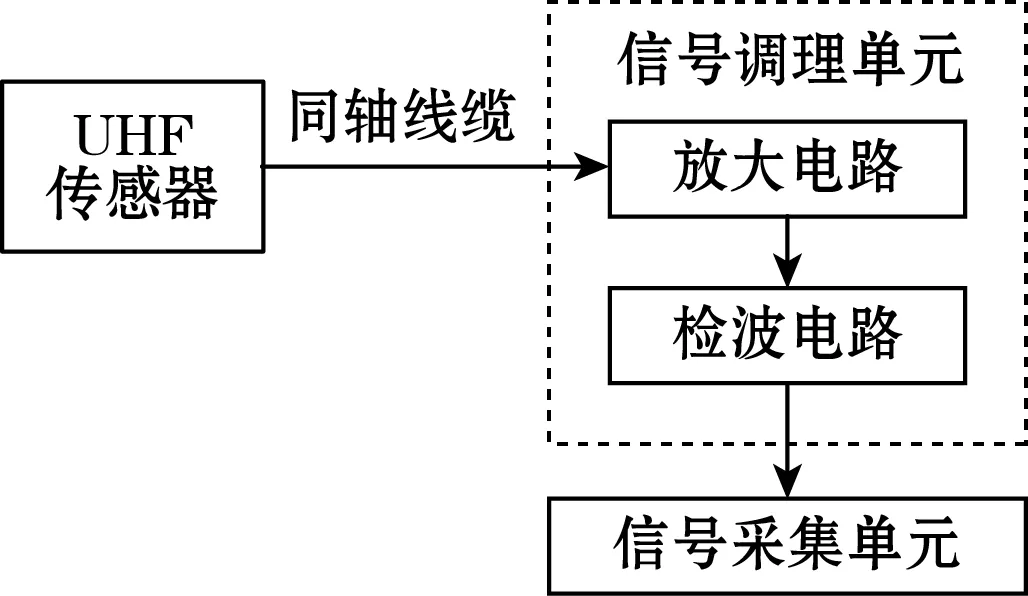

局部放电是一种短时微弱的信号,特高频传感器接收的频率范围为300~1 500 MHz,需要经过一定的处理,使接收信号分别经过放大电路、检波电路后进入信号采集单元进行采样。放大电路使用3 GHz的宽频放大器,外围电路如图2所示。检波电路将传感器接收的高频信号进行降频处理,使之能被AD不失真地采样。信号预处理单元框如图3所示。

图2 宽频放大电路

图3 信号调理单元

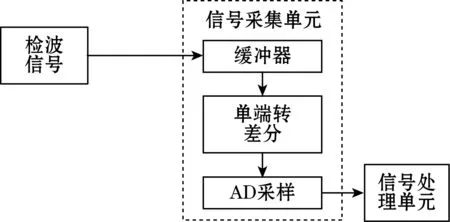

2.2 信号采集单元

信号采集单元如图4所示。为了得到更精确的特征值,使用较高采样率的AD。AD9481是一个8位精度的差分模数转换芯片,能达到250 MHz的采样率,输入范围为1 V。信号经过电压跟随器作为缓冲,为了使AD工作在最佳性能,采取差分输入的方式,缓冲信号进入单端转差分芯片再进入AD采样。为了使信号进入单端转差分芯片后具有较高的信噪比,要求单端到差分的增益为1,输入电阻RL为50 Ω。反馈电阻RF和增益电阻RG为200 Ω,根据式(1)得出单端输入电阻RIN为267 Ω。由式(2)得到当并联电阻RT等于61.5 Ω时,RL才能降为50 Ω。输入电阻AD9481的电路图如图5所示。

图4 信号采集单元

图5 AD9481电路图

(1)

(2)

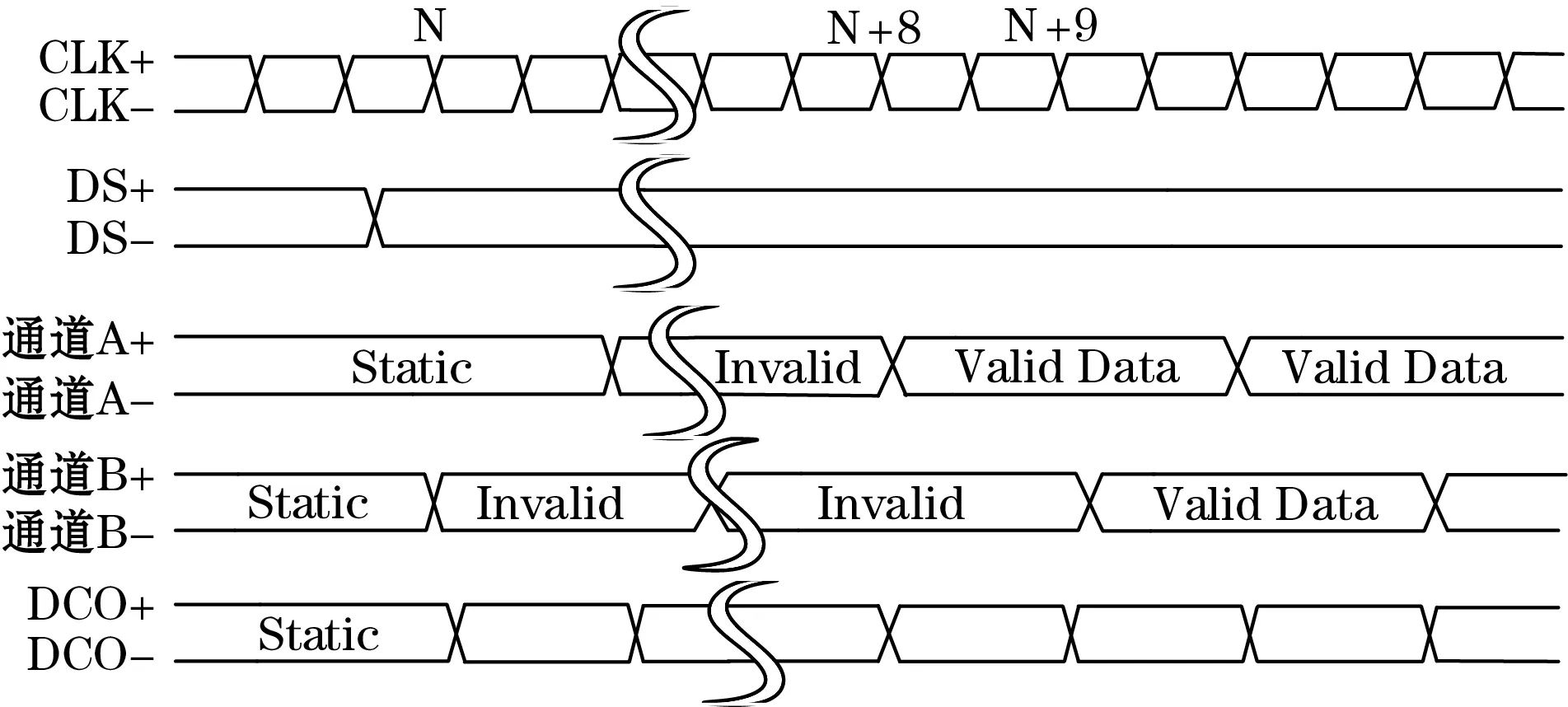

FPGA提供250 MHz的时钟给AD9481。AD9481的时序图如图6所示,DS+为高电平,DS-为低电平时,数据输出和DCO输出都保持静态。DS+的下降沿,即DS-的上升沿出现8个CLK后A通道输出数据,9个CLK后B通道输出数据。DCO的频率是CLK的一半,DCO+和DCO-相位相差180°,AB两通道跟随信号DCO交叉输出。

图6 AD9481时序图

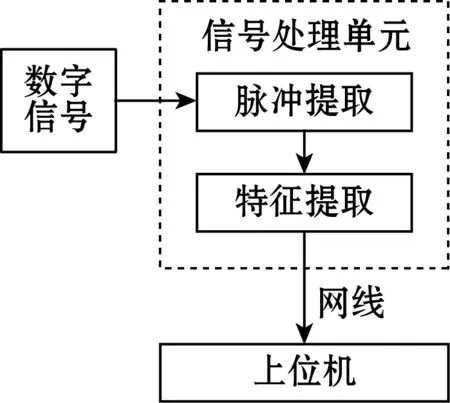

2.3 信号处理单元

为了满足三相局部放电信号同时采样处理所需资源,选取Kintex 7系列的FPGA。FPGA将采集的信号分别经过脉冲提取和特征提取,最终将特征值通过网口发送给上位机。信号处理单元如图7所示。

图7 信号处理单元

小波变换的提升实现由分解、预测、更新组成。小波变换系数受母小波的影响,通过比较波形相似系数选择合适的母小波,波形相似度越大表示母小波和信号越相似,分解的小波系数的值越大。波形相似系数如式(3)所示。

(3)

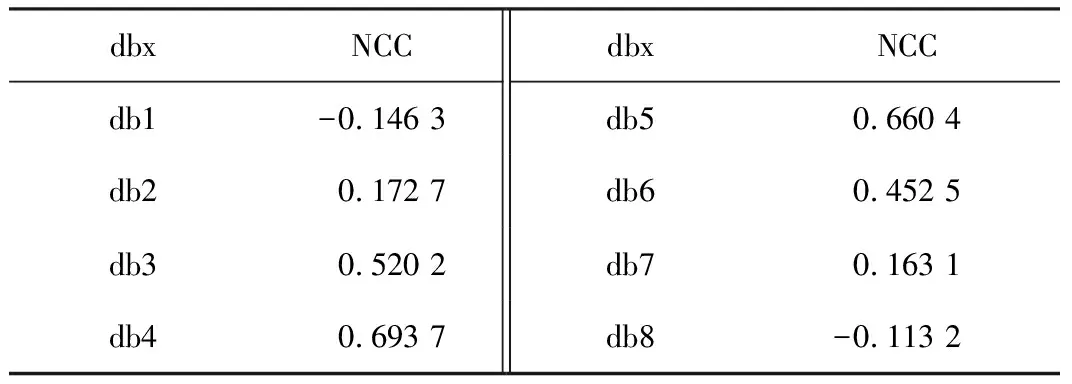

采集的局部放电脉冲波形和Daubcheis系列母小波函数的波形相似系数如表1所示。

表1 相似系数

由表1可知,db4和局部放电脉冲波形的相似系数最大,所以选择db4作为母小波。db4的多相位矩阵的其中一种分解方法如式(4)所示。

(4)

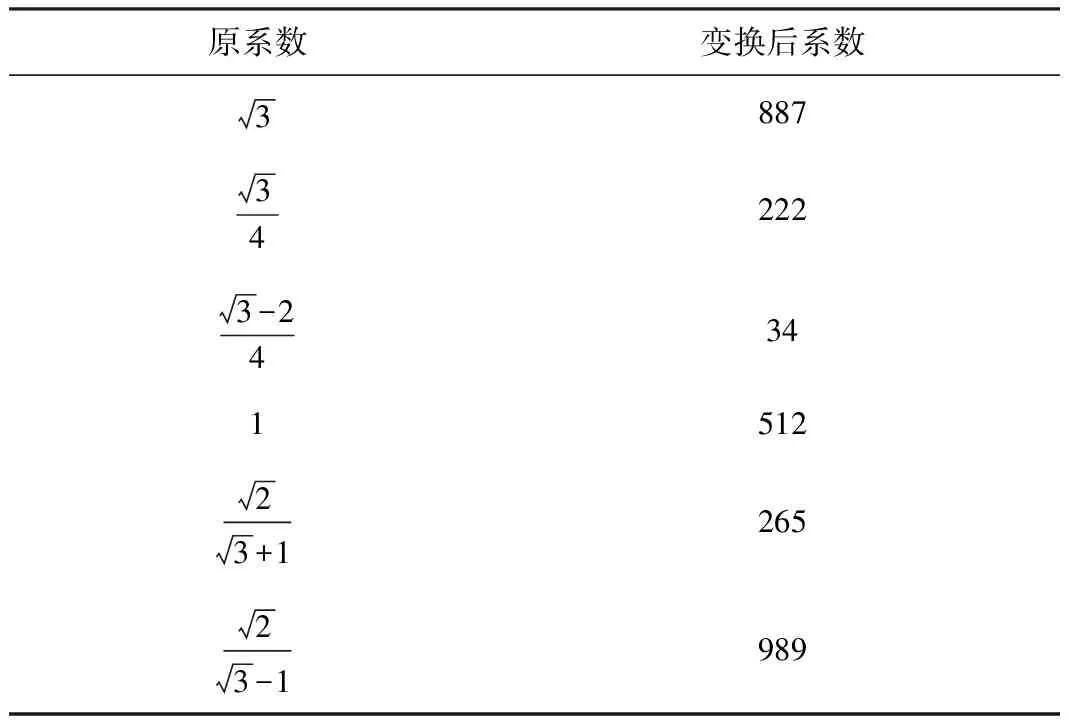

为了方便FPGA的计算,将各系数变换左移9位避免小数的运算,系数变换表2所示。

表2 系数变换

提升小波变换通过流水线的形式将信号分解为4层。流水线设计为4层,第1层为将数据进行奇偶分离,分别用2个寄存器将奇偶数据暂存。第2层预测数据,用之前暂存的数据以及变换后的系数预测相应的奇偶序列并得到预测误差。第3层更新数据,用预测误差更新数据。第4层比例变换。用时序电路保存输入数据及中间数据,由组合电路实现四则运算。

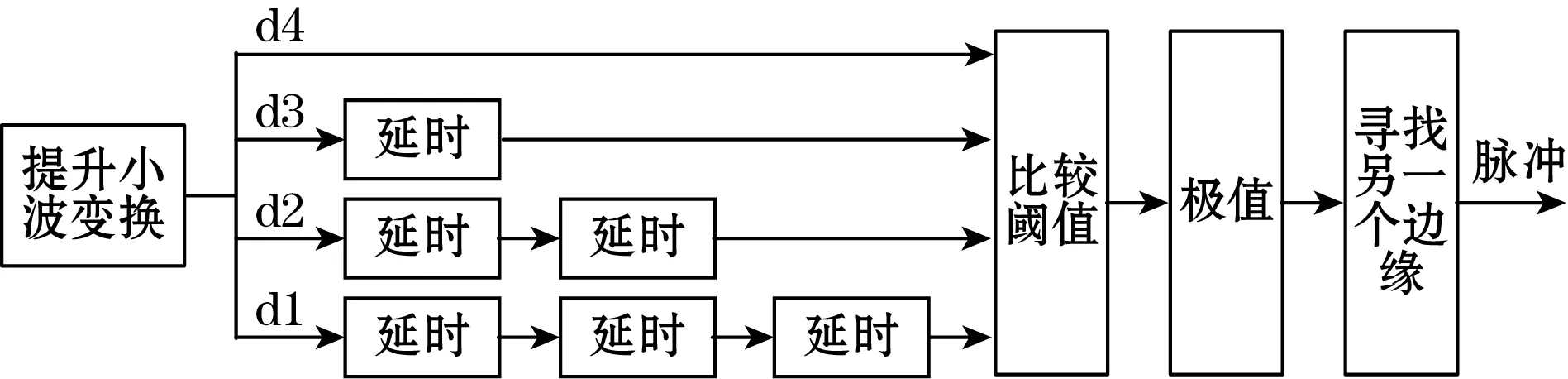

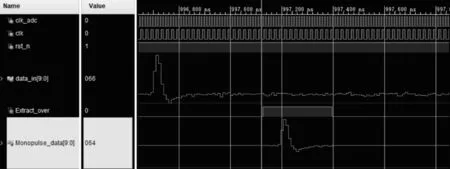

判断每层小波系数的局部极值,每层小波系数同时为极值且极值大于设定的阈值表示该点为脉冲的边缘。沿着边缘向后寻找脉冲的另一个边缘。为了保证4层小波系数输出为同一时刻的信号,使用延迟元素将数据同步。FPGA的脉冲提取模块如图8所示。通过vivado的ila显示的最终提取结果如图9所示。

图8 脉冲提取模块

图9 脉冲提取结果

偏度是用来衡量数据相对于正态分布的对称性或倾斜程度的度量,正态分布的偏度为零。偏度为负值表示向左倾斜,为正值表示向右倾斜的数据,如式(5)所示。

(5)

峰度是衡量数据尖锐程度的指标,如果数据相对于正态分布具有相同的锐度,峰度为零,峰度为负值表示数据比正态分布平坦,为正值表示更尖锐,如式(6)所示。

(6)

3 实验结果

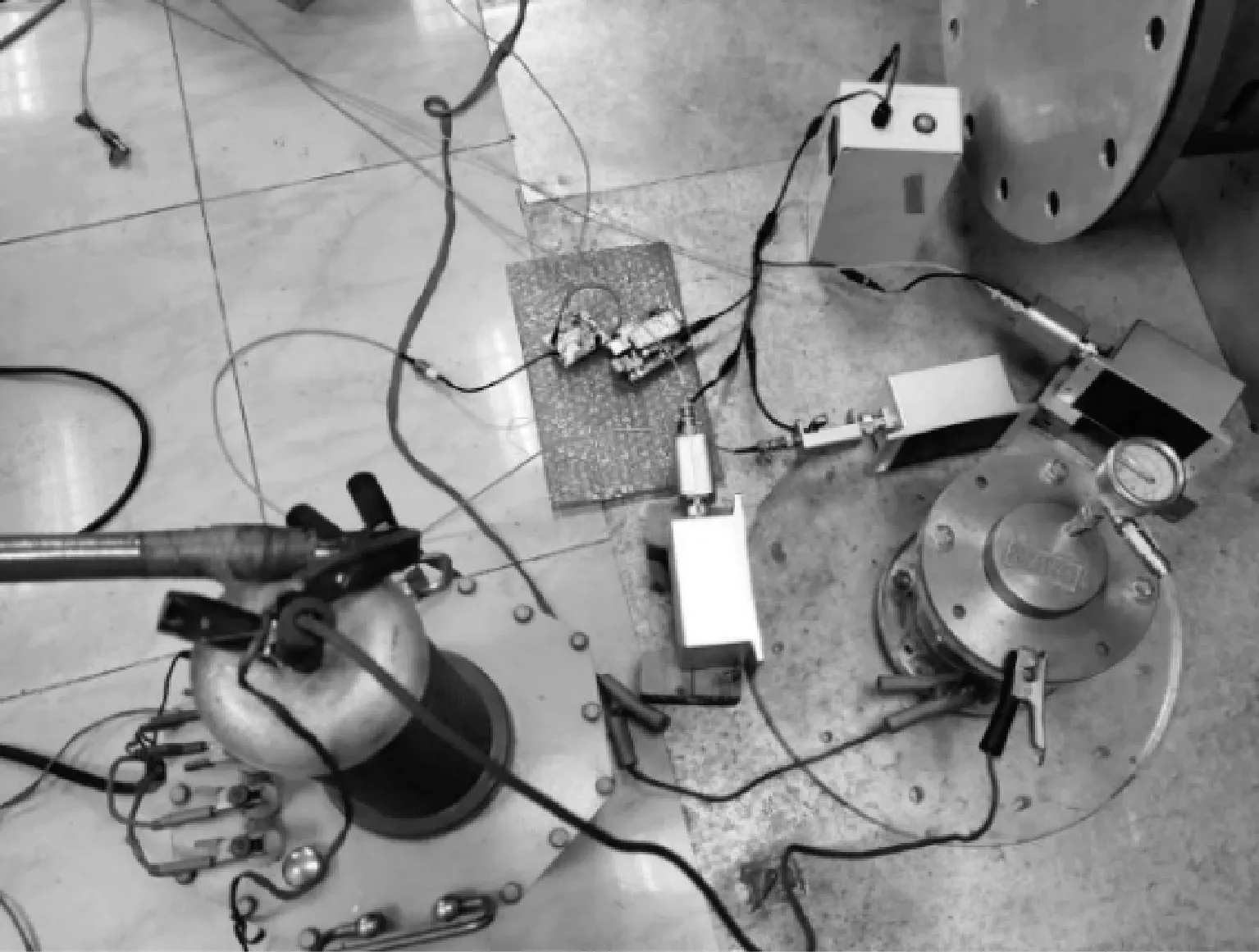

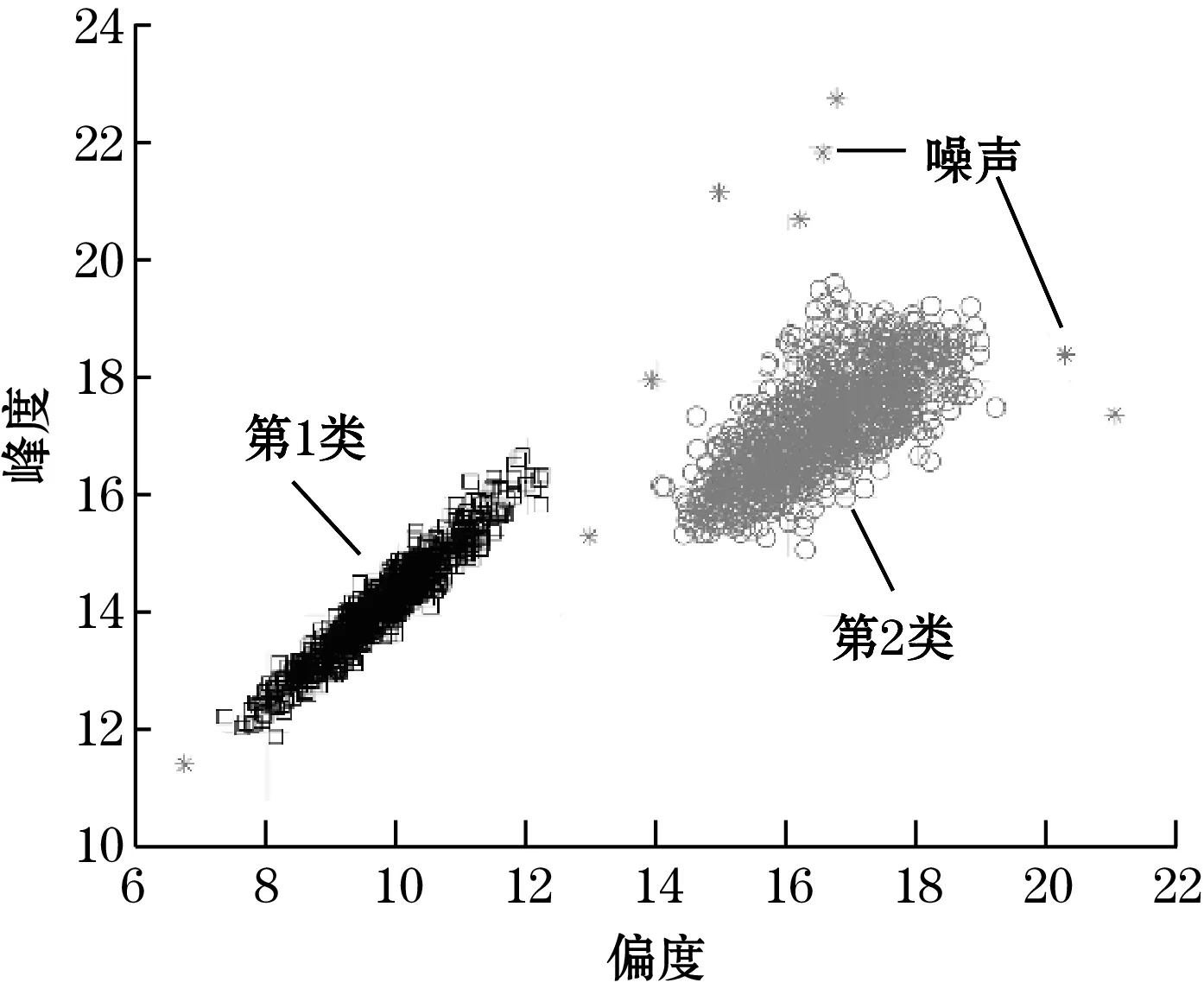

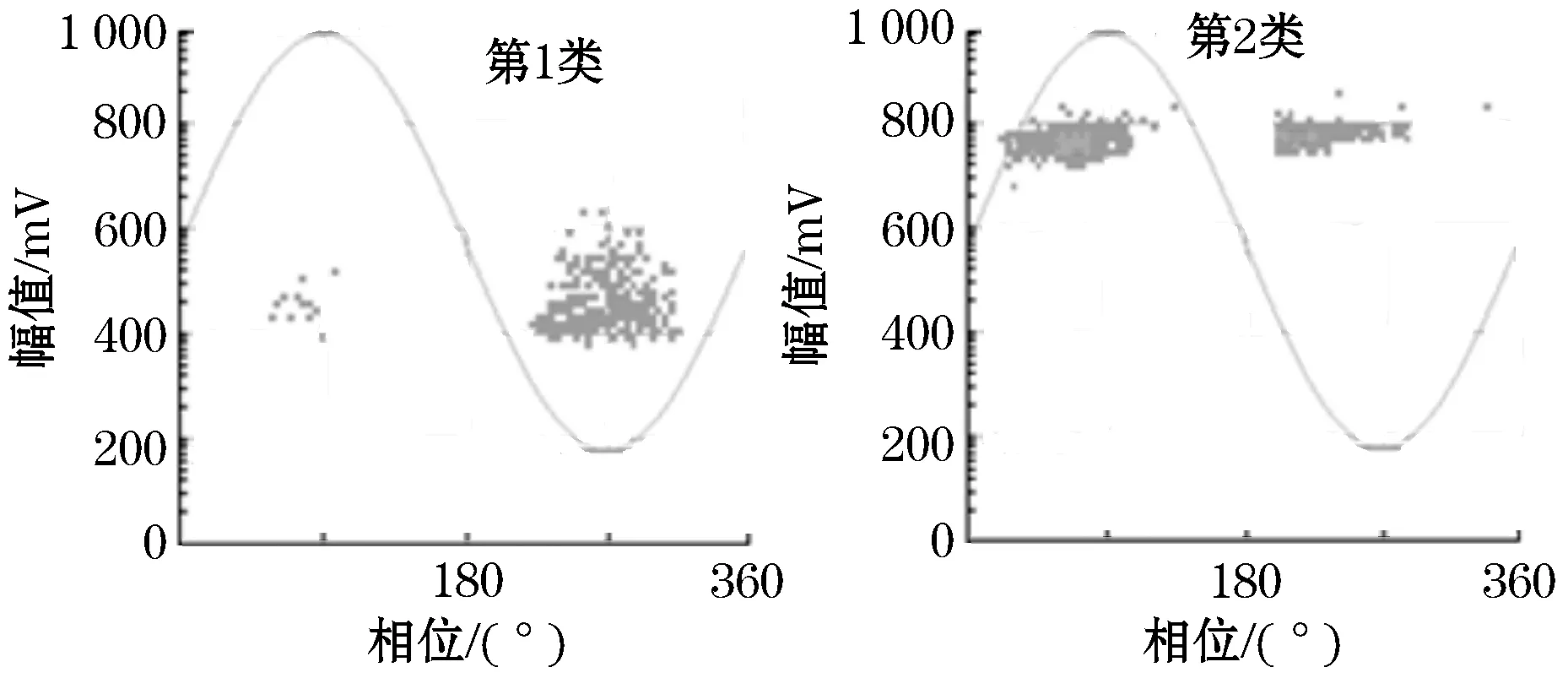

为了验证硬件实现模块的局部放电脉冲提取和特征提取效果,将局部放电发生器接上2个不同类型的局部放电类型绝缘缺陷,如图10所示。同时采集2种不同放电类型的局部放电信号,经过硬件实现模块后上传到上位机进行聚类分离和显示,聚类分离的效果如图11所示,PRPD显示结果如图12所示。

图10 模拟局部放电

图11 聚类效果图

图12 PRPD图谱

4 结束语

本系统通过特高频传感器采集局部放电信号,充分利用FPGA的并行性和灵活性,构建出高速采集和数据处理硬件实现模块。利用提升小波变换易于硬件实现的特点提取脉冲信号,计算脉冲信号的偏度和峰度2个特征,通过网口将这2个特征以及幅值和相位发送给上位机,上位机根据2个特征对脉冲进行分离,分离后的每一类脉冲由幅值和相位绘制出PRPD图谱,用于下一步的识别。由模拟的局部放电信号证明了本系统的可操作性,为局部放电采集系统提供一种基于FPGA的硬件实现方法。