一种基于改进型全通网络版图结构的UWB GaAs移相器*

2021-08-30唐聪

唐 聪

(中国西南电子技术研究所,成都610036)

0 引 言

移相器是相控阵系统中的一个关键器件,它常被用于波束的形成和扫描。近些年来,为满足在大扫面范围、宽带和精准辐射方面的需求,科研工作者在具有宽工作频带、大相移、低插损和较小的相位波动特性等这些方向付出了大量的努力。全通网络由于其本身具有良好的端口匹配特性,常常被用于移相器的设计中以便拓展其工作带宽。文献[1-3]通过将几个具有交错谐振频率的全通网络级联排列,实现了一个具有宽带移相特性的移相器。但是,这些全通网络中的电感之间没有相互耦合,否则移相器的带宽可以做得更宽。并且,在这些移相器中电容和电感值非常大,以至于不能采用单片微波集成电路(Monolithic Microwave Integrated Circuit,MMIC)实现。文献[4-6]基于磁耦合的全通网络被应用于移相器的设计中,通过理论分析证明了全通网络中两个电感之间采用负耦合系数可以展宽移相器的工作带宽,正耦合系数可以实现较大范围的移相但带宽较窄。根据文献[5,7]中的设计公式,全通网络中的各个元素的理论值可以计算得到。文献[5]基于奇偶模分析,推导出了完备形式的电感、电容和互耦系数设计公式。另外在电路设计时,根据理论公式计算的结果还需要进一步优化,因为公式的推导并未将电感线圈之间的耦合电容和基板的寄生参数考虑在内。然而,在实际的电路设计中,为了在较宽带宽范围内实现所需要的参数值,全通网络的版图需要一轮又一轮的电磁仿真迭代。这个过程是非常耗时的,特别是当电路面积较大时这一点将非常明显。如何快速高效地获得满足电路指标需求的电路版图,这是电路设计师经常面对的问题。

本文设计了一个改进型磁耦合全通网络版图,在该全通网络的版图结构中,在输入输出端口之间增加一个电容用于调谐电感之间耦合系数。同时,该电容的引入还可以进一步改善全通网络在超宽频带内的阻抗匹配特性。另外,由于该电容可以作为一个自由设计变量,因此该全通网络的设计灵活度大大增加了。

1 电路工作原理

1.1 改进型全通网络

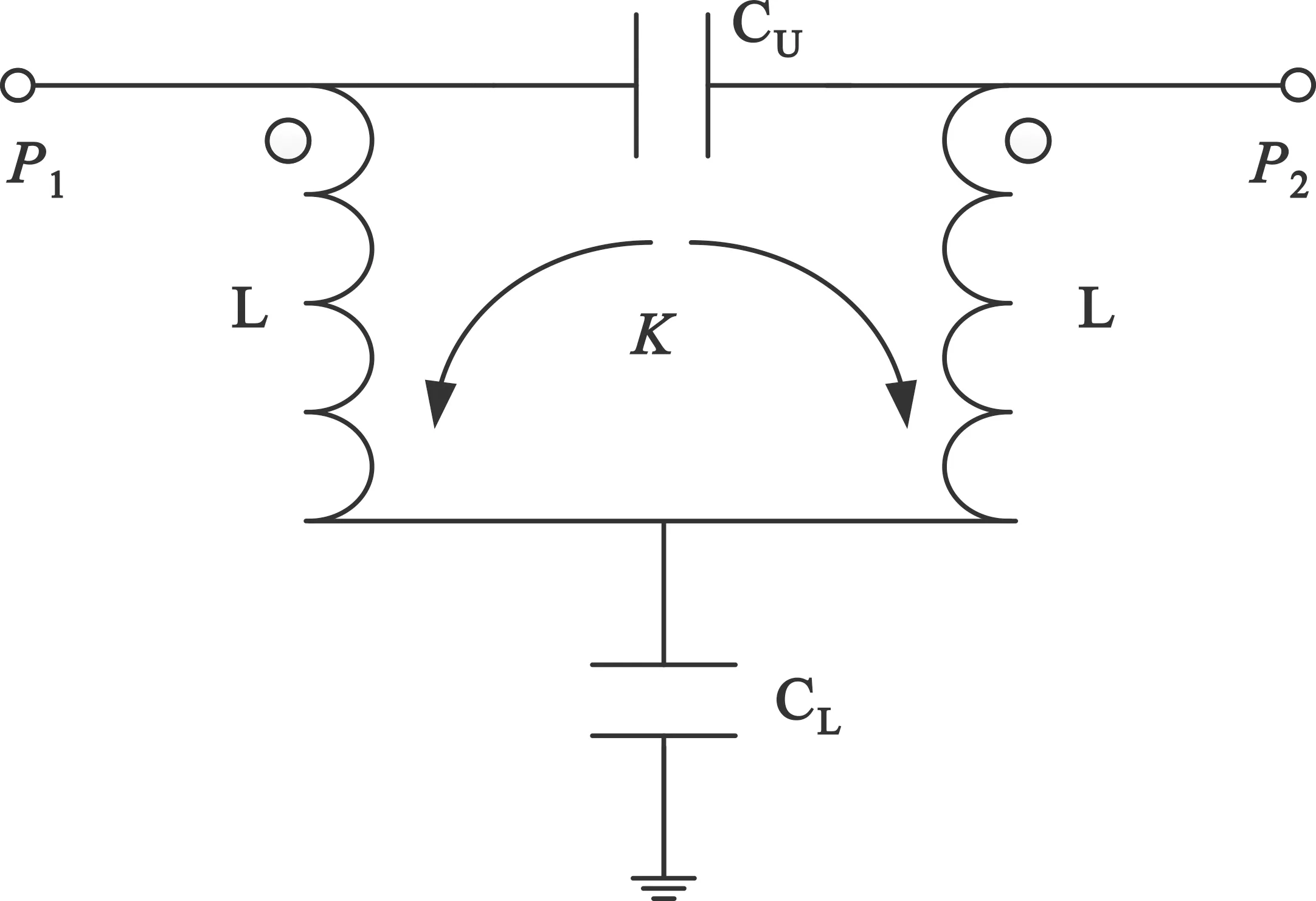

图1中的全通网络可以看作是公共端接电容的两个互耦电感组成的双端口1∶1变压器网络。由文献[8]可知,电感线圈有同向缠绕和反向缠绕两种,同向缠绕时,两个电感之间的耦合系数是正值;而反向缠绕时,两个电感之间的耦合系数是负值。由文献[5]可知,正耦合系数可以获得较大的移相度,而负耦合系数可以获得较大的工作带宽。本文为了获得较大工作带宽,采用负耦合系数。在实际的版图设计中,为了实现电路的对称以及负耦合系数,两个电感反方向缠绕。

图1 基于磁耦合的全通网络原理图

由文献[9]可知,全通网络的带宽受限于其寄生参数,减小线圈间的绕组电容以及基板的寄生参数可以拓展全通网络的工作带宽。基板的寄生参数主要受加工工艺的影响,并且不容易改变,而线圈之间的绕组电容则可以通过控制相邻线圈之间的间距改变。因此,为了拓展全通网络的工作带宽,最直接的办法就是增加线圈之间的间距从而减小绕组电容。然而,一味增加线圈之间的间距也不可取:一方面,增加线圈之间的间距会使整个全通网络的尺寸增大;另一方面,增加线间距也会减小两个电感之间的磁耦合系数k。k的计算公式如下[7]:

(1)

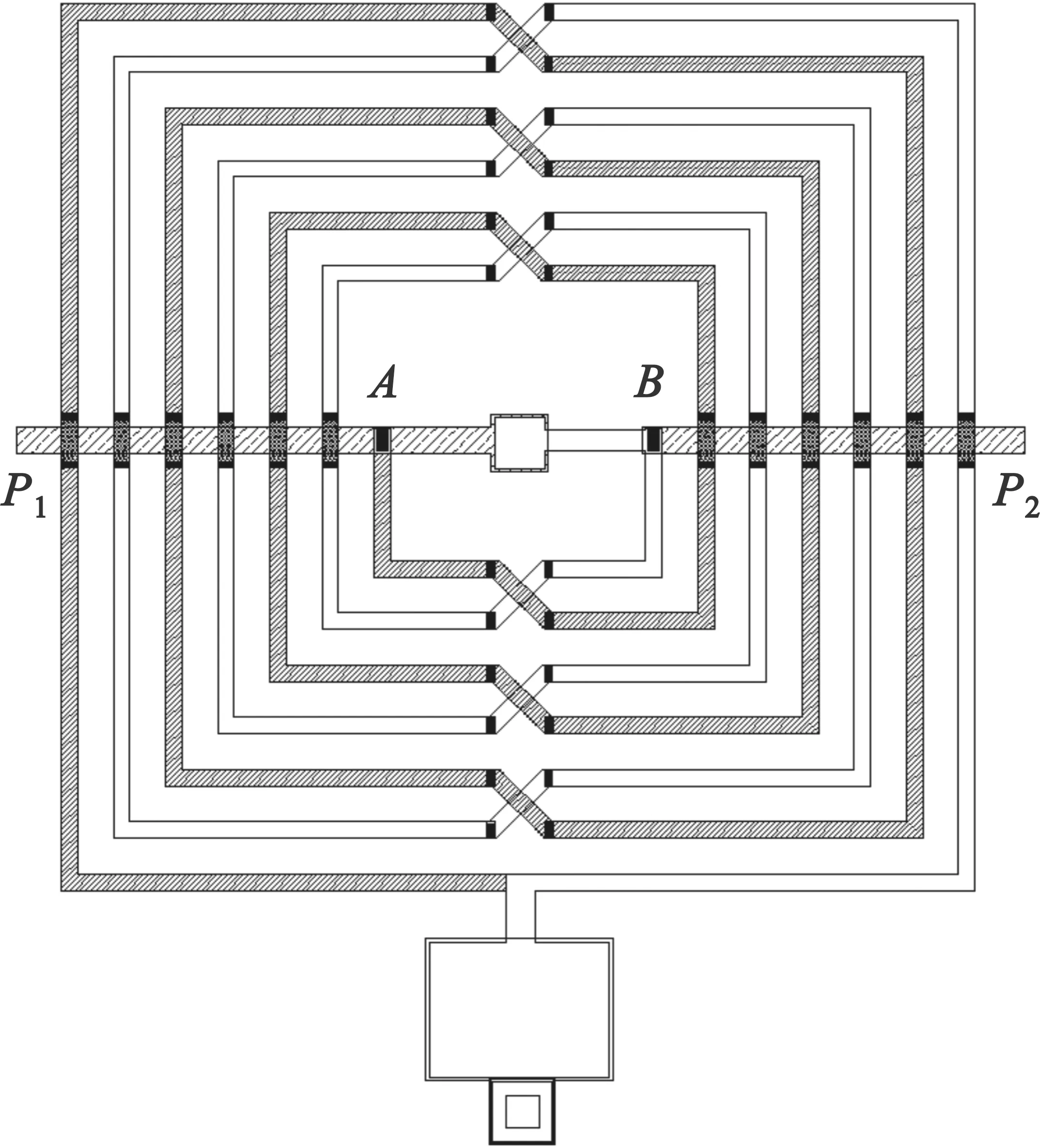

随着磁耦合系数的减小,全通网络的带宽将变窄,高频频率响应首先受到恶化。为了弥补全通网络的高频频率响应,本文设计了一种改进型版图结构,如图2所示,其原理框图与图1所示的传统全通网络框图一致。图2中,在A点和B点之间串联一个电容,该电容并联于全通网络的输入输出端口之间,其频率响应是高通型,允许高频率的信号通过而阻止低频率的信号传输。因此,该电容可以弥补由于线圈间距增加所导致磁耦合系数减小进而引起的高频频率响应恶化的问题。

图2 本文提出的基于磁耦合的全通网络版图

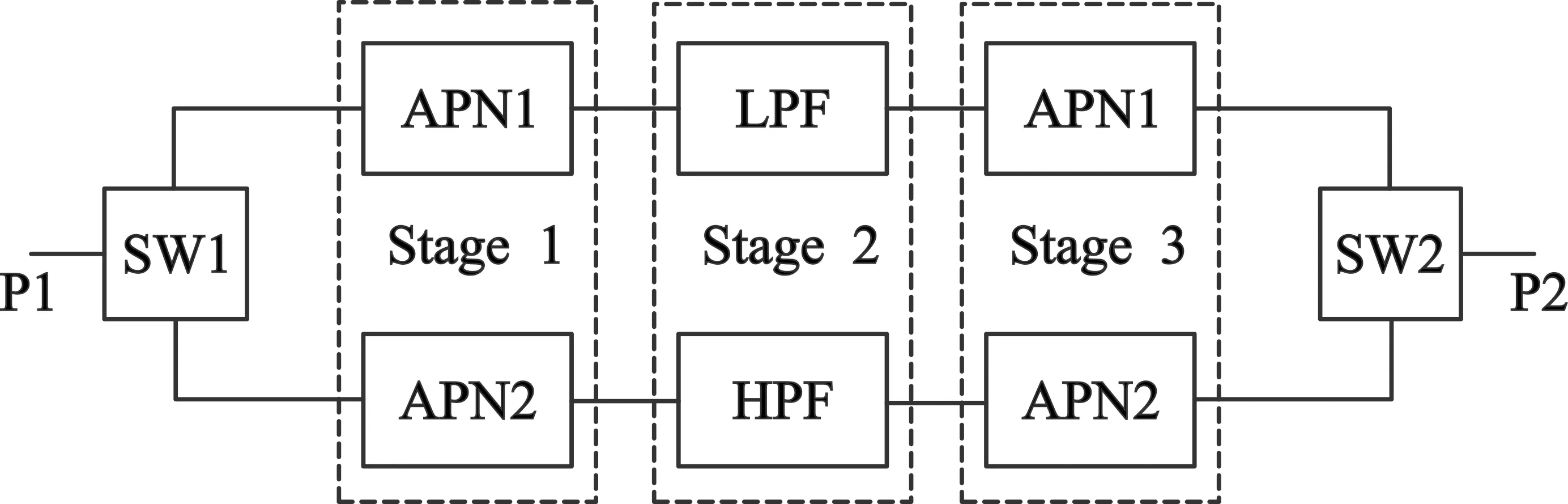

1.2 超宽带移相器设计

为了验证所设计的改进型全通网络版图的正确性,本文在此结构的基础上仿真、设计、加工了两个超宽带移相器并进行了测试。两个移相器的原理框图相同,如图3所示,它由三级移相网络和两个单刀双掷开关组成。当两个单刀双掷开关同时切换到上半边支路时,信号在该支路传输,并且产生随着频率线性变化(理想情况下)的相位φ1,此时可以作为移相器的基态。同理,当两个单刀双掷开关切换到下半边支路时,信号在下半边支路传输,产生随着频率线性变化的相位φ2,此时可以作为移相器的移相态。于是,在开关由上半边支路切换到下半边支路后,整个移相器产生的相对相移可以表示为

图3 180° 和 90°移相器原理图

Δφ=φlower-φupper。

(2)

于是,整个移相器设计关键就转化到设计超宽带移相网络上来。本文所设计的超宽带移相器是通过三级移相网络级联的方式实现超宽带工作,并且第一级与第三级的结构相同,分别位于输入端口和输出端口。为了提升移相器在较低频率处的移相特性,在第一级与第三级之间插入由低通网络和高通网络组成第二级移相网络,并且低通和高通网络均采用T型拓扑结构,因此整个移相器电路关于中心左右对称,具有良好的对称性。

第一级移相网络采用前文提出的改进型全通网络版图结构,通过设计两个具有不同转换频率的APN1和APN2,便可在较宽范围内实现移相。整个移相器的表达式为

(3)

式中:φ1代表第一级移相网络之间的相位差,φ2代表第二级移相网络之间的相位差。φ1和φ2的表达式可以表示为

(4)

(5)

式(4)~(5)中:p1代表图3第一级移相网络中APN1和APN2两个全通网络的转换频率比[3],X和B分别代表高低通网络中的电抗和电纳[10]。

2 实验验证

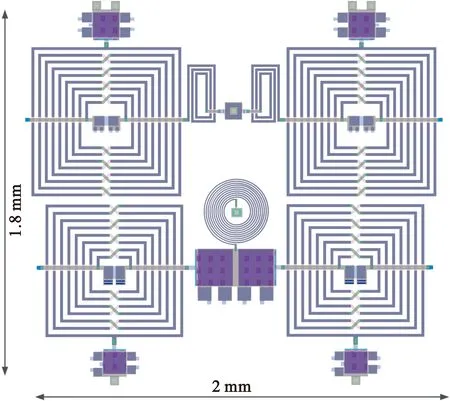

由式(2)可知,为了达到所需要的移相目标值,φ1和φ2有很多的组合。但为了兼顾良好的端口匹配特性,φ1和φ2的可选范围就缩小了很多。通过选取合适的φ1和φ2值,便可以同时实现宽带移相以及良好端口匹配特性。整个移相器的数学理论推导过程较复杂[1],为了提升设计效率,快速得到图3中各个元器件的理论初值,可以采用商用软件ADS自带的优化工具,优化目标是移相度和端口回波损耗。在得到各个器件的理论值之后(如表1所示),将其在电磁仿真软件中转换为版图并进行电路全波电磁仿真。经过几轮迭代修改满足指标要求之后,进行电路的加工。所设计的180°和90°两个超宽带移相器采用0.15 μm GaAs pHEMT工艺,工作频率范围是0.3~2 GHz。电路的尺寸分别是1.7 mm×1.4 mm和2 mm×1.8 mm,版图如图4所示。

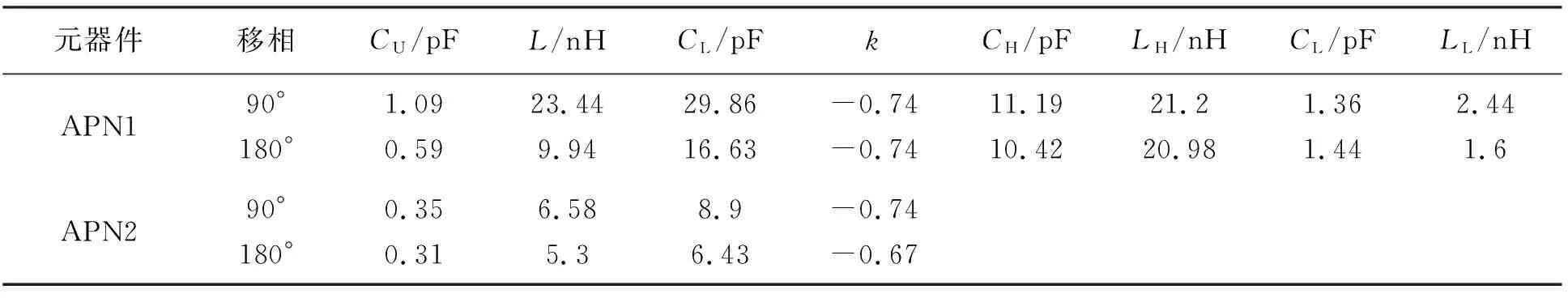

表1 移相电路中各个元器件的理论值

(a)180°

(b)90°图4 移相器版图

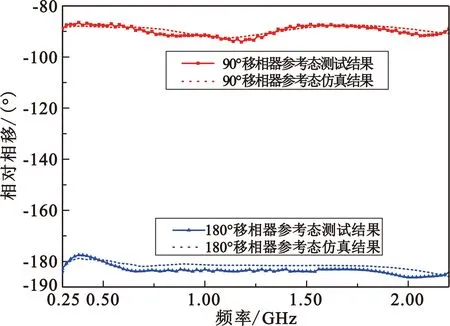

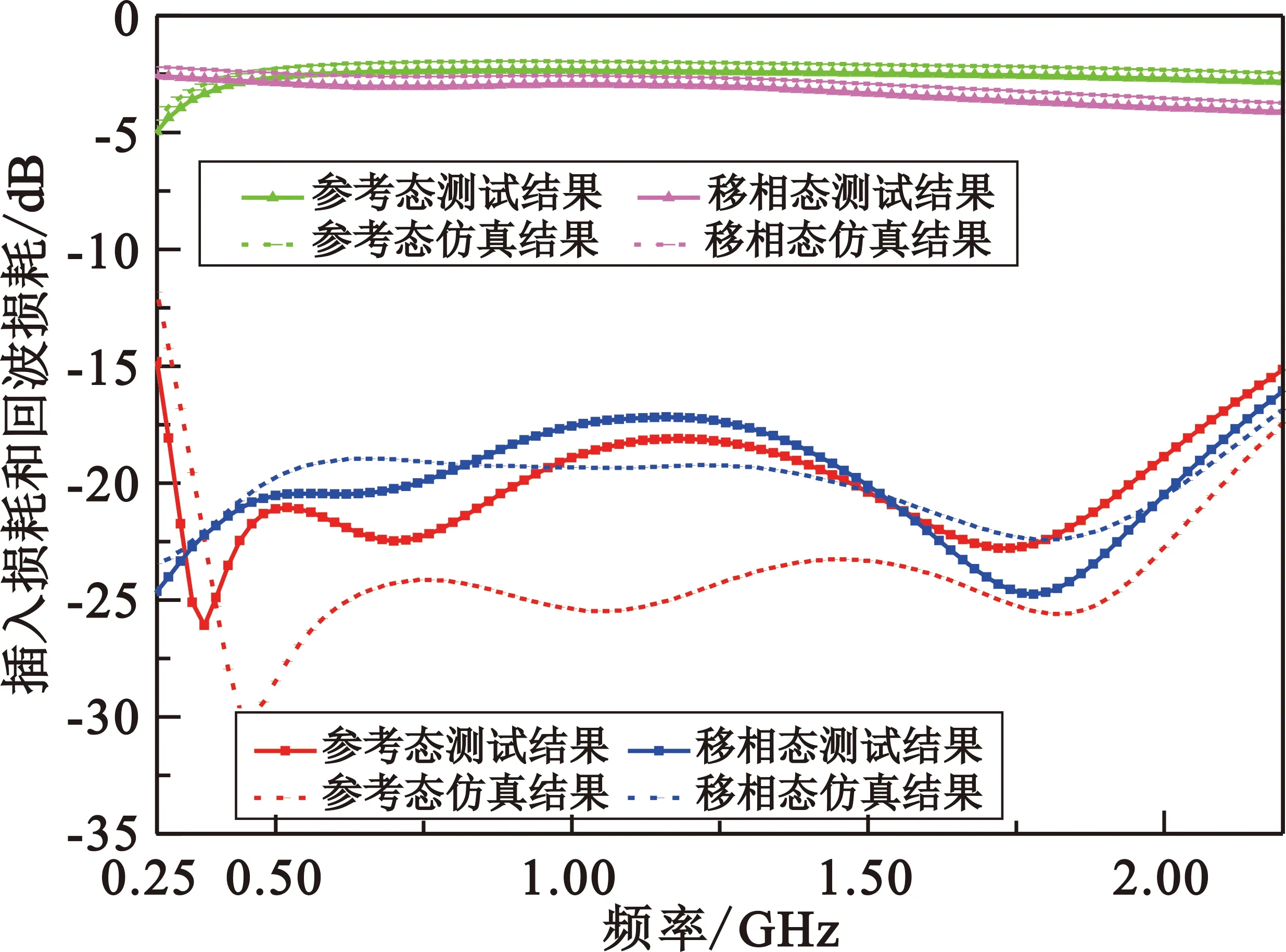

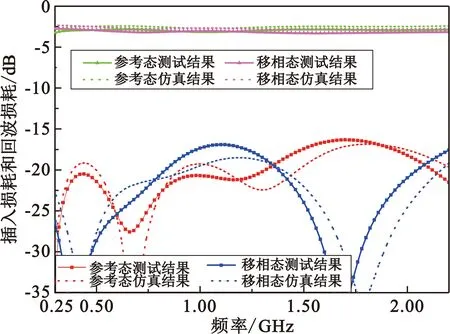

图5给出了两个超宽带移相器的测试与仿真结果,总的来说,测试结果与仿真结果两者吻合得很好。在0.3~2 GHz(相对带宽为152%)范围内,90°和180°移相测试结果分别是-86.5°~-94.2°和-178.2°~ -186°,相应的移相误差分别是4.2°和6°,小于移相目标值的4.2%。180°和90°移相器的带内回波损耗分别优于14.8 dB和16.3 dB。对于180°移相器,基态的带内插损在2.2~4.9 dB范围内,移相态的带内插损在2.2~3.7 dB范围内。类似地,对于90°移相器,基态的带内插损在2.8~3.2 dB范围内,移相态的带内插损在2.7~3.1 dB范围内。可以发现在较低频率处基态的插损比移相态大,这是由于为了改善较低频率处的移相特性而引入高通滤波器的缘故。

(a)移相值

(b)180°移相器的插损与回波损耗

(c)90°移相器的插损与回波损耗图5 移相器的仿真与测试结果

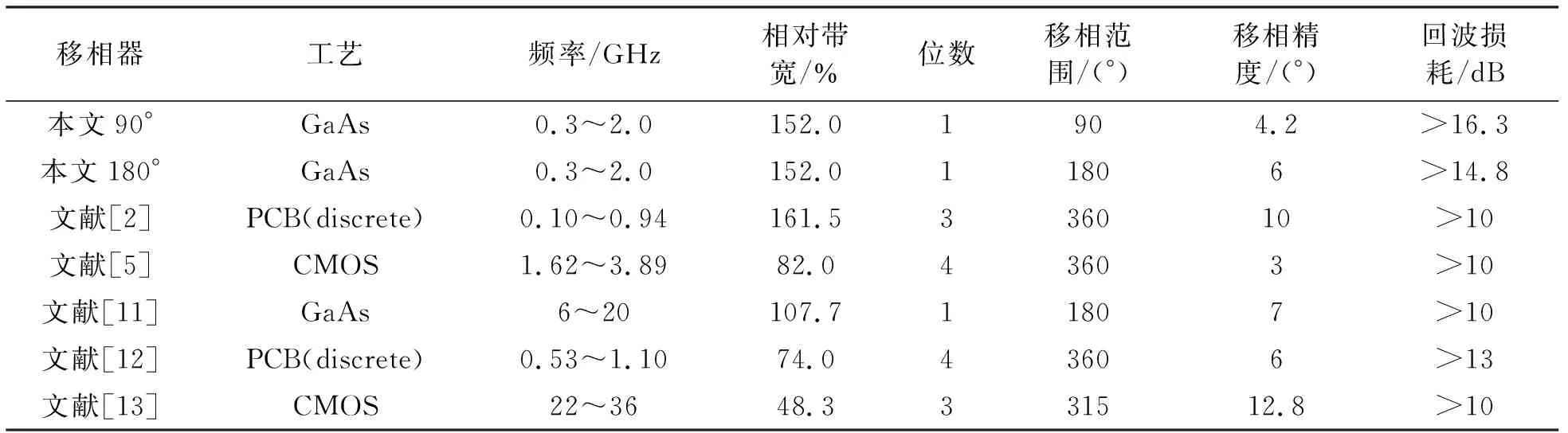

表2列出了本文所设计的移相器与目前公开报道的一些无源移相器之间的性能对比,可以发现,与之前文献[5,12-14]报道的移相器相比,本文所设计的移相器具有良好的回波损耗、大移相度、宽工作带宽和较低的移相误差等优良特性。除文献[2]外,本文所设计的移相器具有最宽的工作带宽。但文献[2]中的电路是采用离散器件制作而成,因此电路尺寸较大。另外,文献[2]中的元器件值特别大,以至于无法采用MMIC工艺实现该电路。因此,与本文所提出的设计方法相比,文献[2]的应用场合受限。

表2 与其他超宽带移相器之间的性能对比

3 结束语

本文提出并通过实验验证了一种超宽带移相器。该移相器基于改进型全通网络结构,该结构在实现超宽带移相的同时可以提高移相器的设计灵活度。通过在全通网络结构的输入输出端口之间增加一个电容,可以很方便地控制全通网络中两个电感的互偶系数。此外,该电容的引入还为输入输出端口之间增加了一个高频信号直接传输的路径,从而有利于拓展高频段的工作通带。为了验证该设计思路的正确性,本文加工了两个宽带移相器。测试结果表明,该移相器具有良好的回波损耗、大移相范围和较低的移相误差特性。下一步将重点考虑电路的进一步小型化和低插损问题。