基于龙芯2K1000 PCI Express 链路重定向的FPGA 逻辑资源动态加载配置机制设计*

2021-08-30付国楷解永亮房利国

付国楷,解永亮,房利国

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引言

随着国产高性能多核处理器的快速发展,高速串行总线技术正取代传统并行总线成为系统级和板级互联设计主要技术。PCI Express 简称PCIE,作为用来互联设备的第三代高性能IO 总线,具有速度快和点对点串行传输的特点,目前已成为微机系统和板级系统中的主流互联总线,在处理器和外围设备的高速IO 接口设计中应用广泛。

当前密码通信和保密安全领域,高性能通信服务设备中的高速数据处理单元普遍基于FPGA 逻辑实现系统业务功能,采用PCIE 总线与处理器进行IO 数据交互。基于PCIE 总线特征,PCIE 设备功能必须在操作系统引导运行前配置固化。当平台引导固件完成PCI 总线扫描或操作系统完成引导后,PCIE 设备就无法实现在线替换或动态加载逻辑资源,也不具备系统实时在线更新、扩充以及升级等功能。在某些高安全级别应用场景,系统正常运行时,基于FPGA 逻辑实现的PCIE 设备功能若需动态实现扩展或升级,则必须暂停或者重启系统。这种操作流程会给系统稳定性、实时性以及可靠性带来较大影响。

本文将简单介绍目前主流国产龙芯2K1000 处理器PCIE 控制器的配置访问方式,设计出一种基于龙芯2K1000 PCIE 链路重定向的FPGA 逻辑资源动态加载配置机制,并结合工程应用实例,重点分析动态加载机制设计要点。

1 PCIE 系统架构

1.1 架构层次

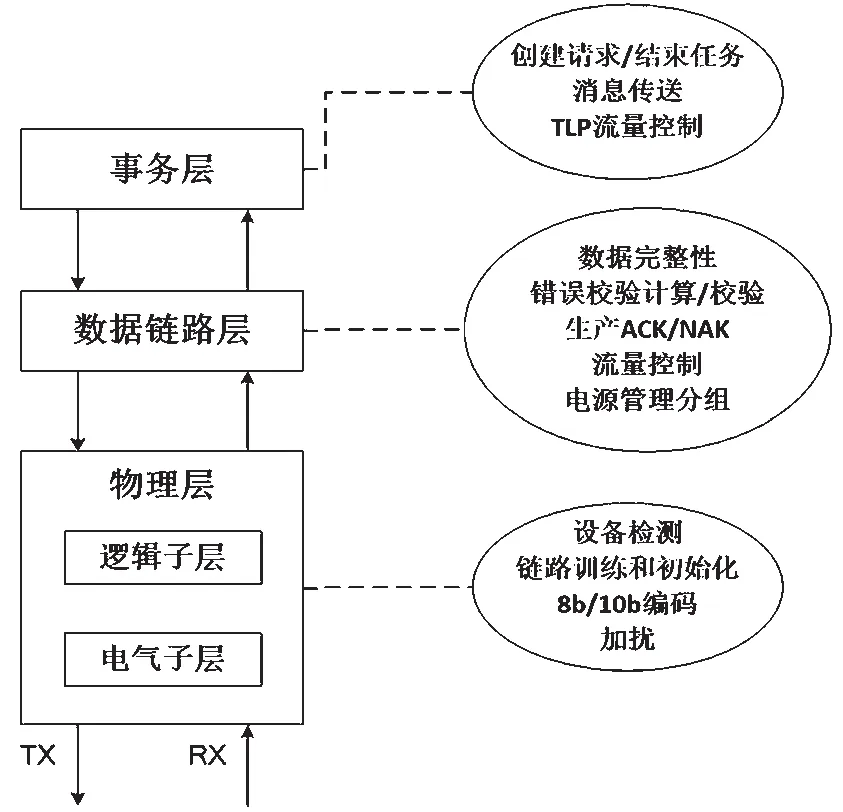

PCIE 有3 层结构,如图1 所示,从上到下依次为事务层、数据链路层和物理层。

图1 PCIE 的3 层架构

事务层负责请求/结束事务结构、TLP 流量控制和消息传送。数据链路层负责保证链路上发送的数据正确,同时负责保证在链路上可靠传送分组。物理层分成逻辑子层和电气子层两个子层。逻辑子层负责数据加扰、8b/10b 编码和分组分帧。电气子层负责收发链路电气信号。所有链路训练均在逻辑子层内部完成[1]。

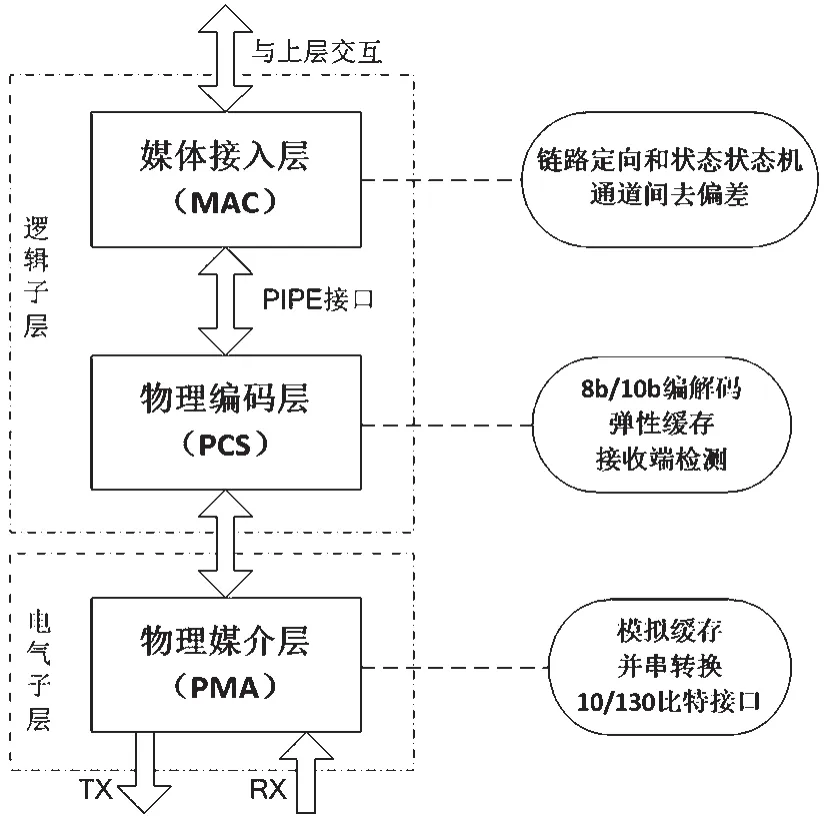

1.2 物理层架构

如图2 所示,物理层分为逻辑子层和电气子层。逻辑子层包括媒体接入层(Media Access Layer,MAC)和物理编码层(Physical Coding Sublayer,PCS)。MAC 和PCS 之间用PIPE 接口连接。电气子层主要包括物理媒介层(Physical Media Attachment layer,PMA)部分。链路训练位于MAC 中[2-3]。

图2 物理层架构

1.3 LTSSM

链路训练状态机(Link Training and Status State Machine,LTSSM)主要负责链路训练和初始化过程。LTSSM 是配置和初始化设备物理层、端口和相关链路的物理层控制过程,使链路可以传送正常的数据包流量。它主要负责配置链路宽度、通路反排、极性颠倒、协商速率、位锁定、符号锁定以及通路间去偏差。

LTSSM 主要包括Detect、Polling、Configuration、Recovery、L0、L0s、L1、L2、HotReset、Loopback和Disabled 共11 个大状态,各个状态又分别由子状态机实现。

1.4 链路初始化和定向

链路初始化和定向是配置和初始化设备物理层、端口和相关链路的物理层控制过程,使链路可传送正常的数据包流量。系统设备复位后即自动发起该过程。LTSSM 在链路定向和初始化过程期间主要完成创建并设置链路宽度、在多通道设备端口上进行通道反转或极性倒置、链路数据速率协商设置、比特锁定、符号锁定以及通道到通道的相位补偿等配置[4]。

2 2K1000 PCIE 控制器

龙芯2K1000 处理器有两个PCIE 控制器,其中一个控制器包含0 号端口~3 号端口,另一个控制器仅包含0 号端口和1 号端口,共6 个PCIE 端口。

2.1 访问地址

龙芯2K1000 处理器对应的端口均有自己独立的PCI 地址空间,采用独立的配置头地址访问,其访问地址和端口BAR0 基地址如表1 所示[5]。

表1 控制器端口地址

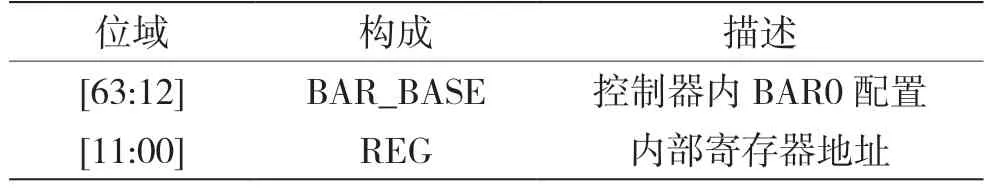

2.2 配置头内部寄存器访问

基于龙芯处理器架构,访问PCIE 控制器各个端口内部寄存器的物理地址采用64 位模式,其构成如表2 所示[5]。

表2 端口内部寄存器地址构成

PCIE 控制器端口都有自己的内部寄存器。访问每个端口内部寄存器时,需选择各自的BAR0基地址。

2.3 配置头空间寄存器访问

基于龙芯处理器架构,对控制器配置头空间寄存器访问采取type1 类型格式,格式如图3 所示。

图3 type1 类型访问格式

PCIE 控制器端口的设备号(Device Number)分别为0x9、0xa、0xb、0xc、0xd 和0xe。根据设备号及所要访问的寄存器偏移地址(Offset),即可得到对应寄存器的物理地址。当寄存器偏移地址offset 大于8 位地址,需将偏移地址高4 位填到bit24~bit27。功能号(Function Number)为1 时,访问配置头空间寄存器[5]。

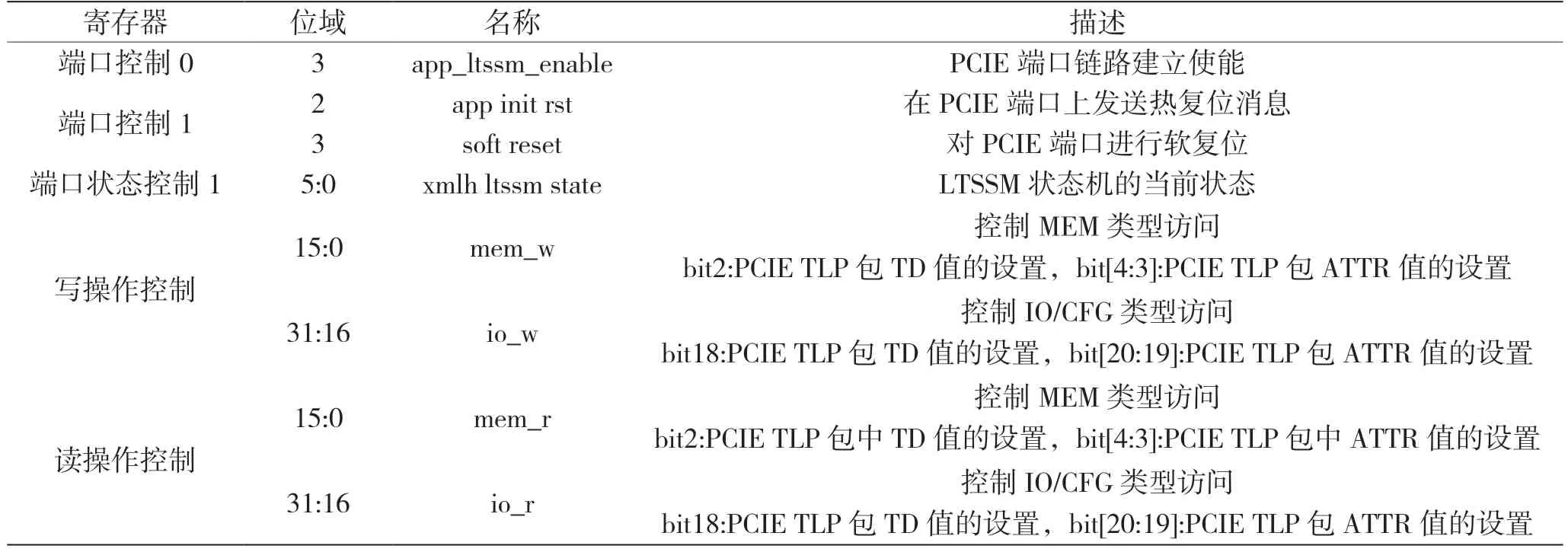

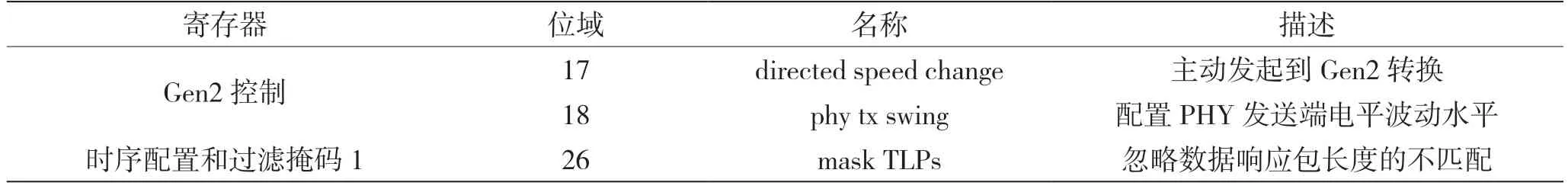

2.4 配置头内部寄存器

通过访问龙芯处理器PCIE 控制器端口内部寄存器,可实现对端口状态的配置管理。重要寄存器相关位域配置参数如表3 所示[5]。

表3 配置头内部寄存器

2.5 配置头空间寄存器

通过访问龙芯处理器PCIE 控制器配置头空间寄存器,可实现对PCIE 链路状态进行配置。重要寄存器相关位域配置参数如表4 所示[5]。

表4 配置头空间寄存器

3 逻辑资源加载

3.1 配置模式

主流FPGA 芯片可以使用以下模式进行逻辑资源加载配置:

(1)使用专用加载配置器件;

(2)被动串行模式(Passive Serial,PS),使用处理器串行同步接口;

(3)被动并行同步模式(Passive Parallel Synchronous,PPS),使用处理器并行同步接口;

(4)被动并行异步模式(Passive Parallel Asynchronous,PPA),使用处理器并行异步接口;

(5)边界扫描模式(Joint Test Action Group,JTAG),使用专用JTAG 下载电缆。

3.2 加载时序

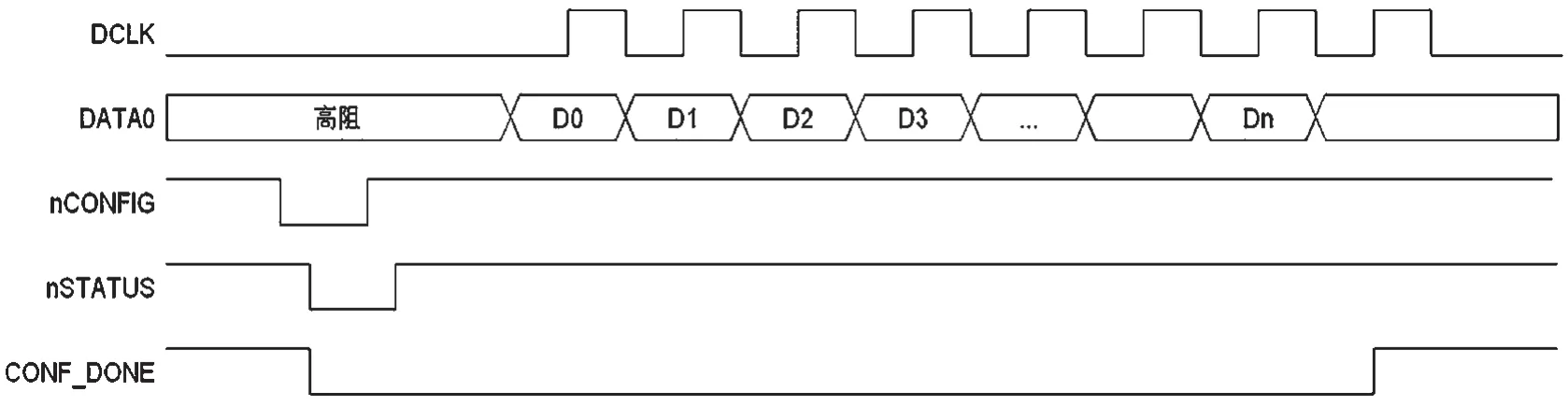

本设计采用被动PS 模式进行逻辑资源加载。处理器将配置数据以串行比特流方式送给FPGA 芯片,模拟配置时钟驱动,完成资源加载。

PS模式采用5根信号线对FPGA芯片进行配置,其配置时序如图4 所示。配置时将信号线接至处理器I/O 口上,其中nCONFIG、DCLK、DATA0 信号线设置成输出状态,nSTATUS、CONF_DONE 信号线设置成输入状态。

图4 加载时序

处理器首先在nCONFIG 信号上产生一个宽度大于8 μs 的负脉冲,然后检测nSTATUS 信号的状态。FPGA 芯片检测到nCONFIG 信号的下降沿后会将nSTATUS 和CONF_DONE 信号拉低,且在nCONFIG 信号重新拉高前保持为低电平。nCONFIG信号拉高后,nSTATUS 将在1 μs 之内随之拉高。处理器检测到此变化后,认为FPGA 芯片做好准备可以开始配置。

配置数据需与配置时钟的上升沿保持同步,处理器在配置时钟的上升沿来之前将1 bit 配置数据反馈在DATA0 信号线上,按先低位后高位的顺序将配置数据从DATA0 信号线上送出。当数据全部配置后,CONF_DONE 信号将被拉高,表明配置结束。处理器检测到CONF_DONE 信号拉高,结束配置过程。如果配置过程中出错,FPGA 芯片将拉低nSTATUS 信号,通知处理器进行错误处理。

4 设计实现

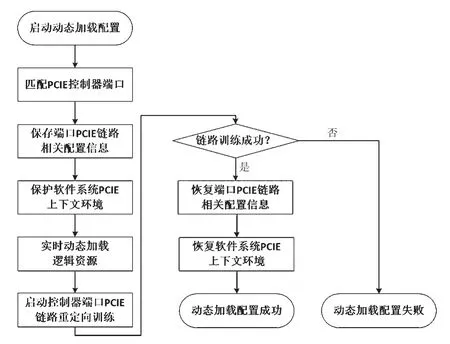

4.1 方案原理

本机制可运行在龙芯2K1000 处理器系统引导固件或操作系统里,接受业务应用需求控制。它的主要功能分为保存系统PCIE 上下文环境、实时动态加载逻辑资源、PCIE 链路重定向以及恢复系统PCIE 上下文环境。方案原理框图如图5 所示。

图5 处理流程

依据PCIE 总线连接关系,本机制首先匹配与FPGA 芯片连接的处理器PCIE 控制器端口,访问控制器端口配置头空间和内部寄存器,保存系统PCIE 上下文环境。

机制随即利用动态可配置技术,依据FPGA 芯片的加载信号,遵循加载规范,模拟加载时序,实时动态加载FPGA 芯片逻辑资源,复位PCIE 控制器端口。

机制依次配置处理器PCIE 控制器端口内部寄存器,启动PCIE 控制器端口链路定向状态训练,触发控制器端口与FPGA 芯片进行PCIE 总线协议握手协商,重新建立PCIE 链路,实现PCIE 链路重定向。

最后,机制利用已记录存储的相关信息,重新配置、恢复处理器PCIE 控制器端口配置头空间相关寄存器配置信息,恢复软件系统相关上下文环境,完成FPGA 逻辑资源的在线动态加载配置。

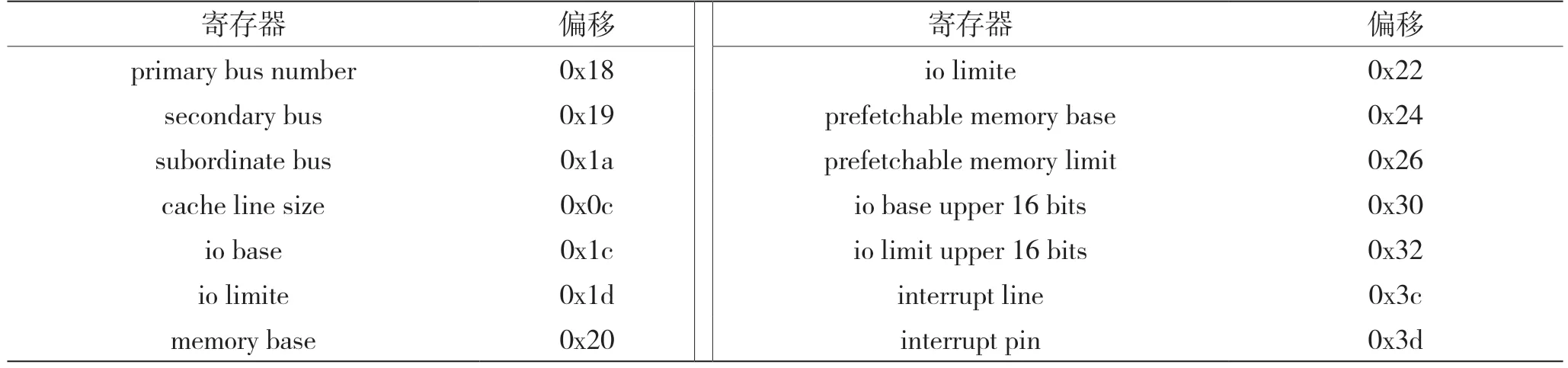

4.2 保存系统PCIE 上下文环境

本功能模块依据PCIE 总线连接关系,匹配FPGA 芯片所连接的处理器PCIE 控制器端口,确定所使用的控制器端口号和配置头访问首地址。

模块随即采用type1 类型访问格式,访问对应的控制器端口配置头空间寄存器,记录存储配置头空间寄存器数值。相关寄存器信息如表5 所示。

表5 存储寄存器信息

确定PCIE 控制器对应端口BAR0 基地址后,模块依次实现对PCIE 控制器端口内部寄存器的读写访问,记录端口BAR0 基地址寄存器所配置数值。

最后,模块负责保护软件相关上下文环境,停止对FPGA 逻辑设计的系统调用,卸载FPGA 逻辑设计相关设备驱动程序。

4.3 实时动态加载逻辑资源

本功能模块利用动态可配置能力技术,采用被动PS 运行加载模式,遵从FPGA 芯片PS 模式加载时序要求,设置处理器互联配置管脚,模拟加载时序,动态加载FPGA 芯片全部逻辑资源。

模块等待资源加载完成,立即检测到PCIE 控制器端口链路链接状态为断开。

模块随即配置使能PCIE 控制寄存器,复位PCIE 控制器端口,完成端口初始化。

4.4 PCIE 链路重定向

本功能模块依据所使用的PCIE控制器端口号,选择对应的配置头访问首地址。

模块首先采用64 位地址方式,访问控制器配置头内部寄存器,设置控制器配置头内部Gen2 控制寄存器的Directed Speed Change(bit17)数据位为1,PHY Tx Swing(bit18)数据位为0。寄存器偏移地址大于8 位地址,需将高4 位填到地址格式中的bit24~bit27[6]。

模块采用64 位地址方式,继续访问控制器配置头内部寄存器,设置控制器配置头内部时序配置和过滤掩码1 寄存器的bit26 数据位为1,设置控制器忽略数据响应包长度的不匹配情况,当接收到与请求长度不匹配的数据包时,控制器不丢弃。

模块依据所匹配的PCIE 控制器端口,选择端口BAR0 基地址,重新配置端口BAR0 基地址,恢复已记录的端口BAR0 基地址寄存器所配置数值。

模块随即访问处理器PCIE 控制器端口内部寄存器,设置端口内部PCIE 写操作控制寄存器、PCIE 读操作控制寄存器的bit[2-4]数据位与bit[18:20]数据位为0,设置控制器端口MEM 和IO/CFG 类型访问中PCIE TLP 包中TD、ATTR 的值为0。

模块根据所使用的PCIE 控制器端口BAR0 基地址,通过MEM 访问设置PCIE 控制器内部PCIE端口控制器0 寄存器的app_ltssm_enable(bit[3])数据位为1,启动PCIE 控制器端口链路初始化,开始链路重定向训练。

模块延时等待,通过MEM 方式访问PCIE 控制器内部寄存器PCIE 端口状态控制器1 寄存器,判断寄存器xmlh_ltssm_state(bit[0:5])数据位值是否为0x11。如果若该字段变成0x11,则表示PCIE 链路重定向训练完成,PCIE 链路重新协商建立成功。

4.5 恢复系统PCIE 上下文环境

本功能模块等待PCIE 控制器端口链路重定向训练成功,链路恢复到正常运行状态便立即更新配置头空间寄存器中的primary bus number、secondary bus、subordinate bus 寄存器,回写为之前存储记录的数值,恢复主总线号、二级总线号配置。

模块根据之前步骤所记录存储的配置头空间寄存器数值,更新配置头空间对应寄存器,恢复最初配置。

模块随即重新扫描系统PCIE 总线,插入FPGA逻辑设计设备驱动程序,启用对新加载的FPGA 逻辑设计的系统调用,恢复软件系统相关上下文环境,即可完成FPGA 逻辑资源的在线动态加载配置。

5 工程应用

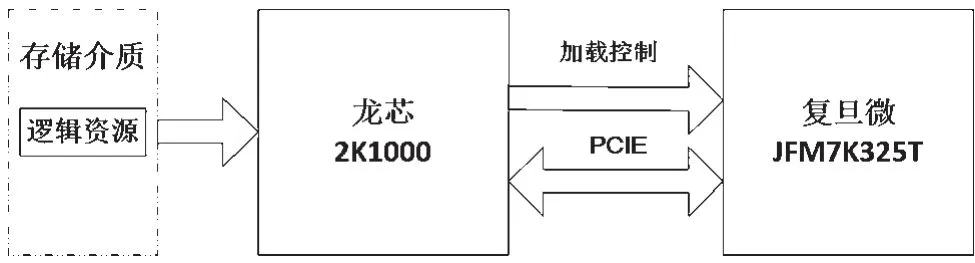

在工程实现中,依托龙芯2K1000 处理器平台,利用动态可配置能力技术,采用PCIE 链路重定向技术,成功实现了对复旦微JFM7K325T 型号的FPGA 芯片逻辑资源的动态加载配置。动态加载配置机制应用示意如图6 所示。

图6 动态加载配置机制应用

经过工程试验验证,该动态加载配置机制运行稳定可靠、灵活性高、实时性强,可保障加载过程中设备系统无需重启,满足各种应用场景下不同安全级别要求,给系统升级与功能完善带来了更大的灵活性。

6 结语

本文提供了一种基于龙芯2K1000 PCIE 链路重定向的FPGA 逻辑资源动态加载配置机制。该机制充分发挥软件化的灵活性,在保障设备系统正常运行状态下,不需暂停或重启系统,通过构建系统PCIE 上下文环境保存/恢复机制,采用可加载配置技术,利用PCIE 链路重定向技术,完成PCIE 控制器端口链路状态重定向训练,在系统运行状态下快速实现设备功能的切换和扩展。

本机制在保障设备系统正常运行状态下,可动态加载不同的FPGA 逻辑资源,实现了各种应用场景所需的系统功能,具有更强的灵活性;可实时加载配置不同安全级别的FPGA 逻辑资源,满足各种应用场景下的不同安全级别要求;可实现功能在线切换与扩展,给系统升级与功能完善带来了更大的灵活性,可保证系统长时间可靠运转,提升了系统可靠性,延长了系统生命周期,具有良好的应用前景。