SiC MOSFET栅源回路参数的串联扰动研究

2021-08-25张宇李先允王书征唐昕杰袁宇卢乙

张宇,李先允,王书征,唐昕杰,袁宇,卢乙

(南京工程学院 电力工程学院,江苏 南京 211167)

现如今,新能源发电、电动汽车以及开关电源等领域的发展趋向于高效率、高转化率以及高可靠性。这使得以碳化硅(silicon carbide,SiC)器件为首的宽禁带半导体器件以其高开关频率、低开关损耗、低散热需求等优点得到越来越多的关注[1-3]。SiC材料的热导系数是Si材料的2.5倍,饱和电子漂移率是Si的2倍,所以SiC器件能在更高的频率、更高的开断速度下工作。现如今对SiC器件的研究主要集中在SiC MOSFET,与传统Si MOSFET相比,SiC MOSFET具有更快的开断速度,更高的功率密度,更高的正向耐压,更低的散热需求[4-6],并且栅源两端具有良好的反向耐压能力(第一代SiC MOSFET可承受-5V,第二代SiC MOSFET可承受-10V)[2],由于其卓越的性能,SiC MOSFET在中、高压领域出现了代替Si IGBT的趋势[7-8]。但是随着电压水平和开关速度的提升,电路中寄生参数所带来的扰动现象将更加严重,这将威胁系统的安全运行[9-10]。虽然依靠新的PCB制作工艺以及封装技术可以有效地减少寄生参数的大小,但是SiC MOSFET也依然面临着串联扰动以及电磁干扰和电磁应力的风险[11],这些负面效应会在一定程度上加速器件老化,严重时甚至造成器件损坏。串联扰动现象主要存在于换流器上、下桥臂结构中,当上桥臂开通时,过高的du/dt作用在下桥臂器件寄生电容上会产生正压尖峰,正压尖峰超过阈值电压时会造成器件的误导通,这将影响系统整体的安全性[12-14]。当上桥臂关断时,积累在寄生电容中的能量得到释放会产生负压尖峰,负压尖峰小于器件栅极耐受值时,会造成器件的损坏。

综上所述,基于栅源回路参数的调控,对器件串联扰动现象进行分析研究[15],得到串联扰动的影响因素,这对SiC MOSFET的工程应用具有极大的意义。本文首先基于串联回路中的单个桥臂进行驱动回路简化分析,建立数学模型,得到影响串联扰动的各个因素,然后搭建平台进行实验验证,最后对实验波形进行进一步分析。

1 简化建模分析

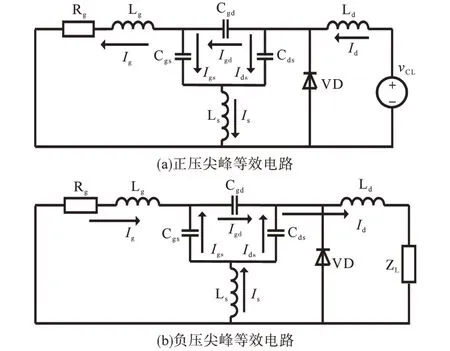

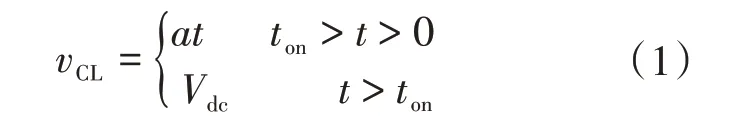

图1为典型同步Buck电路。图1中,上、下桥臂功率开关器件QH,QL均为SiC MOSFET;Cgs,Cgd,Cds为SiC MOSFET封装寄生电容;Cdc为滤波电容;Ld,Lg,Ls,Lloop为杂散电感;ZL为负载;Rg为栅极电阻,由驱动电阻和栅源回路寄生电阻组成;Cg为外加栅极电容,用于栅源电容Cgs的调控,理论分析时不参与讨论;Vq为驱动电压;Vdc为母线电压。本文通过研究上桥臂SiC器件快速开断时,下桥臂器件栅源两端产生的电压尖峰来研究串联扰动现象,文中将串联扰动分为两个阶段分析,其中,第一阶段产生正压尖峰,第二阶段产生负压尖峰。图2为串联扰动等效电路,图3为对应的简化等效电路。

图1 同步Buck电路Fig.1 Synchronous Buck circuit

图2 串联扰动等效电路Fig.2 Series disturbance equivalent circuit

图3 简化等效电路Fig.3 Simplified equivalent circuit

1.1 栅源回路参数对正压尖峰的影响

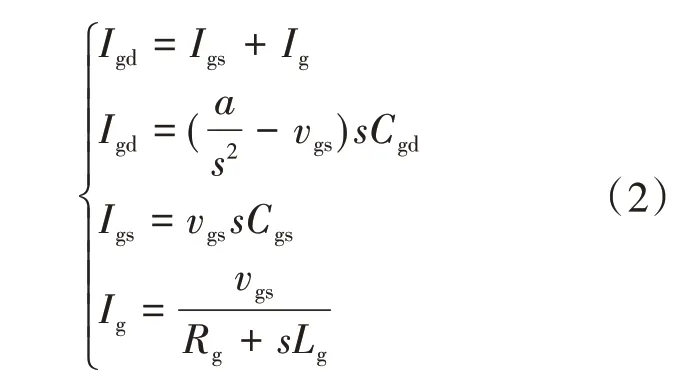

当QH快速导通时,QL漏源两端电压vds瞬间由0升高至母线电压Vdc,过高的du/dt作用在Cgd上将产生漏电流Igd,并对Cgs进行充电,使Cgs上形成一个正的电压尖峰,正压尖峰等效电路具体如图2a所示。其中,Igd,Igs,Ids分别为电容Cgd,Cgs和Cds上的电流;Ig,Id,Is分别为器件栅、漏、源极流过的电流;vCL等效为上桥臂开通瞬间作用在下桥臂器件漏源两端的电压(不考虑器件导通电阻的变化),由上桥臂开断速度和母线电压Vdc共同决定,可近似等效为

其中

a=Vdc/ton

式中:ton为下桥臂漏源电压上升时间。

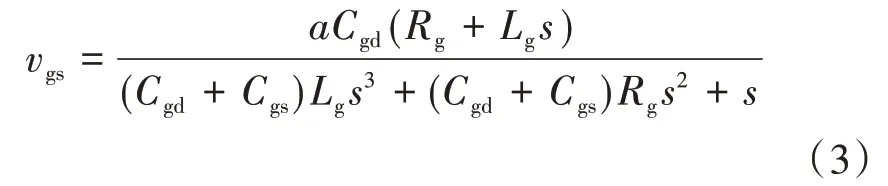

根据基尔霍夫定律对图3a进行节点电压方程的列写:

点G,S分别为器件栅、源极,解得:

进行Laplace逆变换,并假设:

解得:

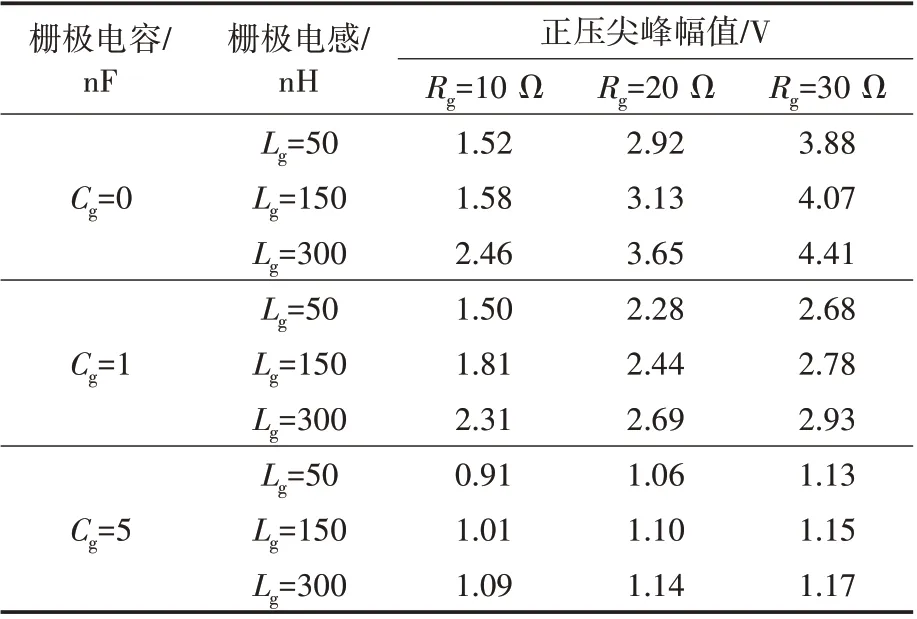

以SiC MOSFET器件C2M0080120D为例,输入电容Ciss=950 pF且随vds变化较小,栅漏电容电容Cgd随着vds的增大迅速降低,取Cgd=15 pF。当器件工作电压Vdc=500 V时,假设栅源电压上升时间为49 ns,串扰等效电源的系数a=1.53×107V/s,驱动电压为+20/-5 V,改变栅源回路参数得到正压尖峰幅值如表1所示。

表1 不同栅源回路参数下的正压尖峰幅值Tab.1 Spike amplitude of positive pressure under different grid-source loop parameters

由表1分析可得,当上桥臂开断速度和母线电压不变,即a为定值时,正压尖峰幅值随着驱动电阻Rg、杂散电感Lg的增大而增大,随着寄生电容Cgs增大而减小,其中Cgs可以通过栅极电容Cg进行调控。

1.2 栅源回路参数对负压尖峰的影响

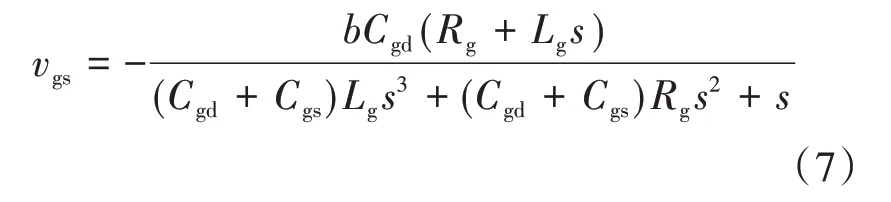

当QH快速关断时,QL漏源两端电压vds由母线电压Vdc迅速降为0,积累在电容Cgd上的能量开始释放并形成漏电流Igd,当漏电流流经Cgs时将在栅源电容上形成一个负的电压尖峰,具体如图2b所示。图2b为负压尖峰等效电路,其中ZL为负载,IL为流过负载的电流。由于Cds放电过程中电流Ids不经过电容Cgs,讨论vgs的时候可以忽略。杂散电感Ls仅为引脚杂散电感,其值过小,近似计算时可以省略。Cgd放电时二极管VD反向截止,仅在放电结束时为Ld提供续流通道,当忽略负载ZL以及线路杂散电感的影响,仅针对栅源回路对正压尖峰等效电路进行简化以及Laplace变换,具体如图3b所示。其中,系数b=Vdc/toff,下桥臂漏源电压下降时间toff由上桥臂关断速度决定,现假设系数b为定值。根据基尔霍夫定律对图3b进行节点电压方程的列写:

对式(6)进行求解,得:

联立式(4)对式(7)进行Laplace逆变换,得:

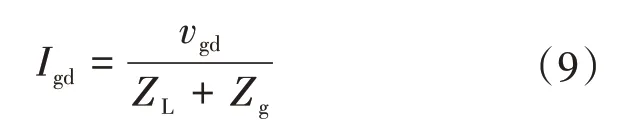

当器件工作电压Vdc=500 V时,假设器件关断速度为40 ns,理想状态下栅漏电容放电系数b=1.87×107V/s,改变栅源回路参数得到负压尖峰幅值如表2所示。

表2 不同栅源回路参数下的负压尖峰幅值Tab.2 Spike amplitude of negative pressure under different grid-source loop parameters

由表2可知,当系数b为定值时,vgs负压尖峰幅值随栅极电阻Rg、栅极电感Lg的增大而增大,栅极电容Cg增大,即栅源电容Cgs增大时,负压尖峰幅值变化减小。

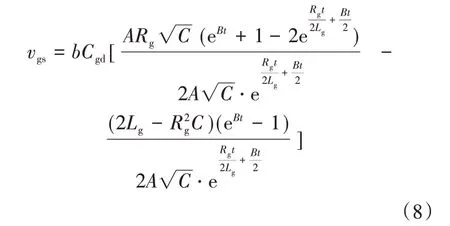

1.3 负载电阻对负压尖峰的影响

当不考虑负载电阻时,vds的下降时间toff主要由上桥臂器件的关断速度决定,具体如1.2节所述。但由图2b可知,在同步Buck电路中,负压尖峰阶段Cgd释放能量时将会经过负载电阻ZL,假设电容Cgd放电初始为恒压源,有:

式中:Zg为栅源回路阻抗。

当ZL增大时,Igd随之下降,由Qgd=CgdVdc=Igdtoff可知,当电容两端电压和储存电荷不变时,Cgd的放电时间toff将会随之增大(toff≥tf,tf为上桥臂器件关断时间),电容Cgd放电转为自由放电,电压下降速度不再由tf决定,此时负压尖峰简化电路如图3c所示。由于图中标记部分端口结构未发生变化,输入电流Igd减小会使负压尖峰幅值降低,toff增大使负压尖峰持续时间增大,同时两者共同作用使得调控寄生电感Lg对负压尖峰幅值的影响降低。本文主要讨论栅源回路对串联扰动的影响,故对负载的影响不做深入研究。

2 实验验证

搭建如图4所示的同步Buck电路实验平台进行电压尖峰观察及上述推导的实验验证。实验采用Tektronix公司生产的DPO4054B示波器及其配套电压探头TPP0500和P5205A,SiC MOS⁃FET采用CREE公司的C2M0080120D,续流二极管为SiC肖特基二极管C4D20120D,触发脉冲由Firstack公司生产的脉冲触发仪提供。图5为电压尖峰实验波形,由于负载电阻的存在,负压尖峰幅值较小,实验波形同时也证实本次实验平台的正确性。

图4 实验平台Fig.4 Experiment platform

图5 电压尖峰Fig.5 Voltage spike

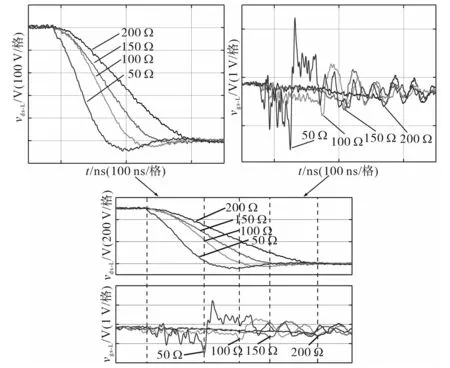

对上述理论分析进行实验验证,为了保护器件安全运行,基础测试电压Vdc选为500 V,驱动电阻Rg为5 Ω,栅极电容Cg为1 nF,栅极电感Lg为0,负载电阻ZL为50 Ω。图6为改变栅源回路参数时的电压尖峰波形,为了清晰地表达波形变化,仅展示部分参数,其中左图均为正压尖峰波形,右侧均为负压尖峰波形。图6a为驱动电阻分别为0 Ω,7.5 Ω,12.5 Ω,20 Ω时的电压尖峰波形。由图6a可得,当驱动电阻增大时,正、负压尖峰均增大,负压尖峰震荡变小,这是由于驱动电阻与栅极电容形成RC滤波,降低震荡。图6b为栅极电容分别为0 nF,0.5 nF,1 nF,10 nF时的电压尖峰波形,由图6b可得,当栅极电容增大时,正、负压尖峰均变小,负压尖峰震荡也变小。图6c为栅极电感分别为23 nH,81 nH,257 nH时的电压尖峰波形,由图6c可得,当栅极杂散电感增大时,正压尖峰变大,负压尖峰基本不变,负压尖峰震荡变大。

图6 改变栅源回路参数时的电压尖峰Fig.6 Voltage spike with different gate-source loop parameters

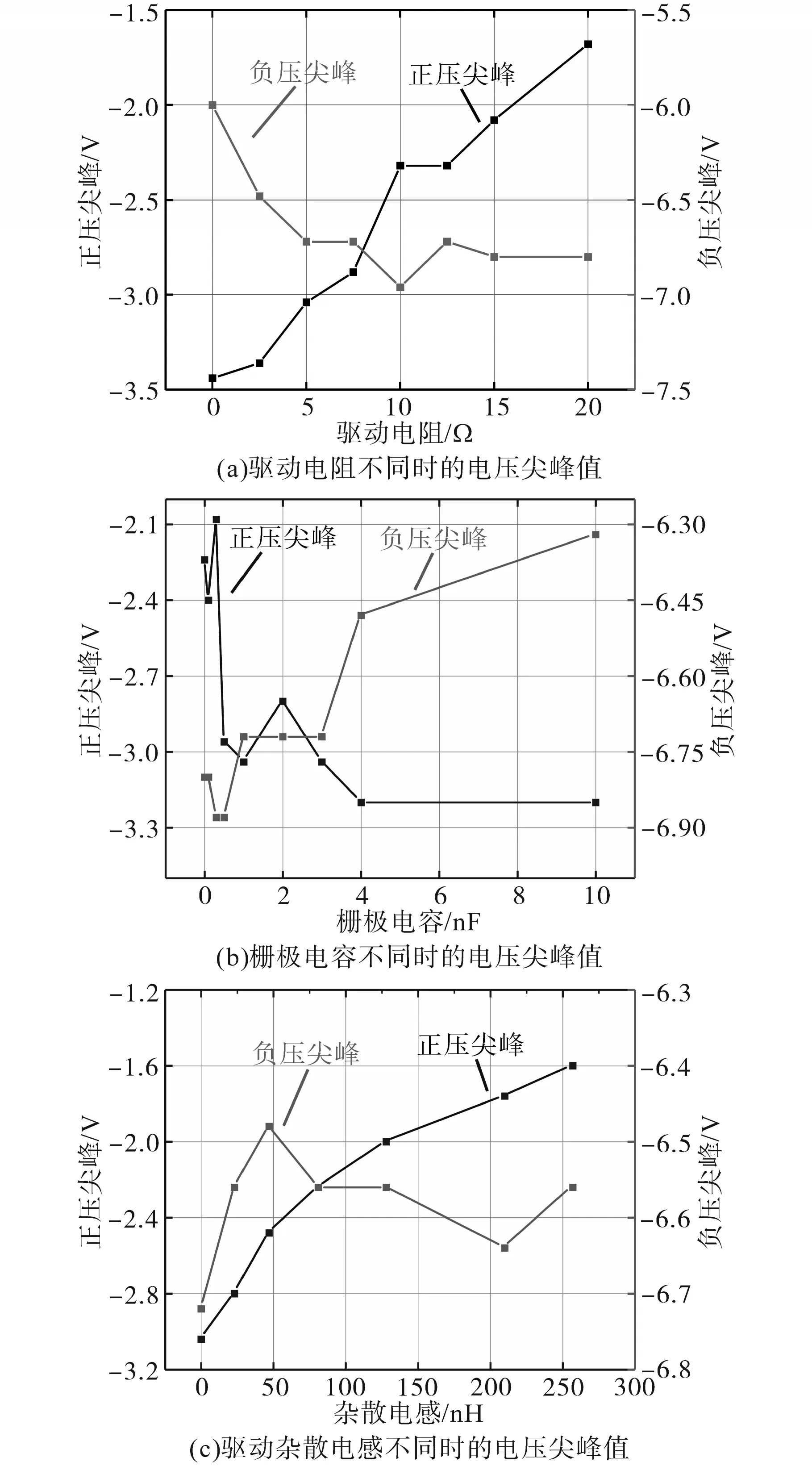

图7为不同栅源回路参数的电压尖峰值,统计了改变栅源回路参数时的所有实验结果。由图7可得,当驱动电阻为0~20 Ω,仅驱动电阻增大其他条件不变时,正、负压尖峰均增大。栅极电容为0~10 nF时,随着栅极电容的增大,正、负压尖峰均减小。栅极电感为0~300 nH时,栅极杂散电感增大,正压尖峰增大,负压尖峰基本不变。其中,正压尖峰幅值变化较大,负压尖峰幅值变化较小,这与负载电阻的接入有关。

图7 不同栅源回路参数的电压尖峰值Fig.7 Voltage spikes of different gate-source loop parameters

由1.3节推导可知,当其它条件不变时,负载电阻的大小会影响负压尖峰幅值的大小和持续时间,现通过实验进行验证。不同负载电阻时,器件漏源电压vds及负压尖峰之间的关系如图8所示,由图8可见,当负载电阻增大时,vds下降时间也增大,同时负压尖峰持续时间正比于vds下降时间,幅值大小正比于dvds/dtoff。

图8 不同负载电阻的负压尖峰Fig.8 Negative voltage spikes with different load resistances

对上述实验分析可得,通过对栅源回路参数的调控可以达到调节电压尖峰的目的,与前文理论分析结果一致。为了同时满足SiC MOSFET驱动的快速性与安全性,驱动回路设计时PCB布局注意降低寄生参数,驱动参数选择时,建议降低驱动电阻的大小,利用增大栅极电容来降低器件高速开断过程中的过冲与震荡现象。以Buck电路为例,负载的大小会影响负压尖峰幅值以及持续时间,换流器正常运行时建议工作在满载状态。

3 总结

本文基于栅源回路参数调控对SiC器件串联扰动现象进行分析研究并进行实验验证,结果表明:

1)器件所受的串联扰动现象是器件高速开断形成的du/dt作用在相邻器件封装寄生电容上引起的,可以通过栅源回路参数和负载阻抗进行调控。

2)电压尖峰随着驱动电阻、杂散电感的增大而增大,随着栅极电容的增大而减小,较大的负载电阻有利于降低负压尖峰。驱动电路设计中应该降低驱动电阻的大小,通过提高栅极电容来抑制开关震荡。

3)伴随电压尖峰出现的尖峰震荡也对器件安全产生威胁,还需进一步研究。