基于ZYNQ的全冗余高速箭地通信装置设计

2021-08-04王有春平佳伟韩雨桐王晓林向四桂

王有春,徐 昕,谢 芳,平佳伟,韩雨桐,王晓林,向四桂

(1.上海航天电子技术研究所,上海 201109;2.北京宇航系统工程研究所,北京 100076;3.航天系统工程研究所,北京 100048)

0 引言

随着航天运载领域的不断发展,新技术不断应用,新型的低温燃料运载火箭不断立项并入列执行任务,运载火箭作为航天探索领域的基础[1],在总装、总测和发射前都需要与后端地面测发控系统进行通信,进行功能和性能的全面检查和确认。箭地通信装置是连接运载火箭箭上单机和后端地面测发控系统的关键通信设备,其通信质量的好坏将直接影响箭上与地面系统通信的稳定性、可靠性和安全性。

箭地通信装置通过LVDS/RS422电缆与箭上系统通信,通过网络与后端测发控进行通信,同时需要具备信号处理以及数据分析的功能。传统运载火箭的箭地通信多采用工控机和功能板卡的形式,以工控机为核心进行数据分析,以功能办卡为外设实现信号处理和通信,这种方式具有板卡更换方便、软件开发方便的优点,但是同时带来了体积大、重量大、可靠性低、价格昂贵等缺点。

目前,基于ZYNQ架构的FPGA+ARM技术逐渐成熟,在民用市场已经得到广泛应用,也逐渐进入航天领域,针对箭地通信装置的需求以及传统方式缺点的深入分析和研究后,本文采用ZYNQ架构研制了一套以ARM为主控核心进行资源调度以及网络通信控制、以FPGA作为逻辑控制核心进行信号处理及高速LVDS/RS422通信控制的高速箭地通信装置,同时通过双机热备份实现全冗余。该方案相比传统方案具有通用性强、可靠性高、传输距离远、集成度高的特点,是箭地通信的一种新的解决方案,也符合高性能、低成本、通用性的航天产品研发理念。

1 系统结构及原理

通信装置主要需要满足与箭上通信、与地面测发控系统通信、本地逻辑处理等功能。

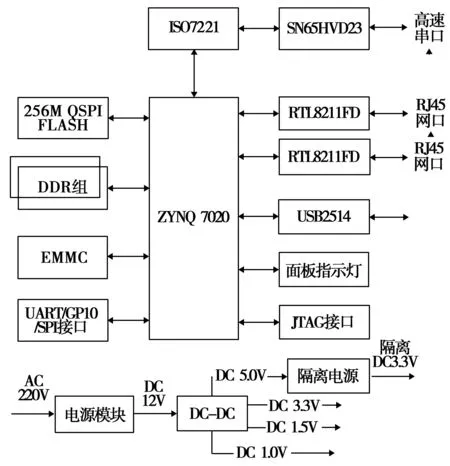

根据使用需求,将通信装置进行功能层次划分,主要分为软件层、硬件实现层、接口层。系统组成框图如图1所示。

图1 系统组成框图

软件层,运行在Linux系统上,由网络通信、数据存储、DMA(direct memory access,直接存储器访问)通信、自检及状态监测、数据解析5个功能模块组成。主要完成上行邮箱数据的网络接收、数据解析、DMA总线发送,下行邮箱数据和总线数据的DMA总线接收、数据解析、网络转发,信息流的存储,装置自检及状态监测。

硬件实现层,主要包括AXI_DMA传输控制、数据存储控制、数据采集及输出、数据组帧以及ARM单元的生成。硬件实现层通过对需求深入分析,按功能进行分割,进行模块化设计,包括总线及邮箱数据采集单元的逻辑设计,邮箱输出单元的逻辑设计、数据8B/10B编解码的逻辑设计以及组帧拆帧的逻辑设计,最终实现了功能的一体化集成。

接口层,主要包括网络接口和高速串行总线接口。网络接口实现双网口绑定并与后端测发控系统的连接,高速串行总线接口完成与箭上设备的连接,包括节点、通道的分配,输入输出电平的匹配。

2 系统硬件设计

2.1 原理设计

通信装置采用分体式模块设计,结构尺寸设计为1U标准机箱,硬件结构如图2所示。各个模块通过内部接口连接到一起,同时可以通过背板扩展出更多模块。

图2 硬件结构图

通信装置根据功能可将内部划分为主制模块、背板模块、接口通信模块以及电源模块等。

主控模块内部集成处理器,DDR3高速缓存、大容量FLASH、RTC实时时钟以及网络控制器,主要完成系统控制、数据处理、以及与后端地面系统的数据通信工作。

背板互联模块主要提供系统内部电源分配、模块之间数据交互、机箱风扇以及指示灯的接口。

接口通信模块主要功能是完成设备LVDS/RS422接口的隔离和驱动电路[2-3]。

实现与箭上系统的通信,通过LVDS/RS422接口接收箭上总线数据和邮箱数据,向箭上发送邮箱数据,满足箭地之间150米的传输距离,10 Mbps波特率带宽下的可靠传输。

通信装置的功能框图如图3所示。

图3 功能框图

2.2 主要元器件选型

1)FPGA芯片:

FPGA采用XC7Z020芯片,该芯片主要分为PS和PL两部分,PS部分为处理器系统,包含双核ARM Cortex A9,运行频率776 MHz,有丰富的外设接口,例如CAN、UART、I2C、SPI、USB、SDIO、EMMC等;PL部分为可编程逻辑系统,带有CLB、Block RAM等资源。PS和PL之间通过AXI接口进行通讯[4]。

2)存储模块:

存储模块由2片DDR3、1片EMMC和1片QSPI FLASH组成。其中DDR3的型号为MT41J256M16HA-125IT,容量为1 GB、位宽为32 BIT,最大速率1 600 MHz,用于操作系统内存。EMMC的型号为THGBMBG8D4KBAIR,容量为8 GB,用于操作系统文件存储。QSPI FLASH,型号为S25FL128SAGMFIR01,容量为256 MBIT,用于存储FPGA代码。

3)接口通信模块:

接口通信模块主要由隔离芯片和RS422接口芯片组成,隔离芯片采用TI公司的ISO7221C,该芯片内部采用电容隔离方式,传输速率可达25 Mbps,该芯片主要用于保护设备间通信安全,防止一方设备故障时损坏另一方设备。RS422接口芯片采用TI公司的SN65HVD23,该芯片主要用于长距离线缆传输的驱动。

2.3 系统资源分配

通信装置需要兼顾ARM运行LINUX操作系统进行网络数据解析处理以及FPGA端进行接口数据的时序处理的需求,需要合理分配ZYNQ内部公用资源[5],搭建芯片的内部系统硬件平台为操作系统提供运行环境,同时也为内部ARM与FPGA之间建立AXI总线通信通道。

为通信装置分配了两个以太网控制器用于双网口通信、两个串口控制器用于系统配置参数交互、两个DMA控制器用于FPGA与ARM之间的双向数据传输、一个EMMC控制器用于系统文件存储、一个DDR3控制器用于操作系统缓存、一个USB控制器用于系统调试、若干个GPIO用于状态指示和风扇控制。

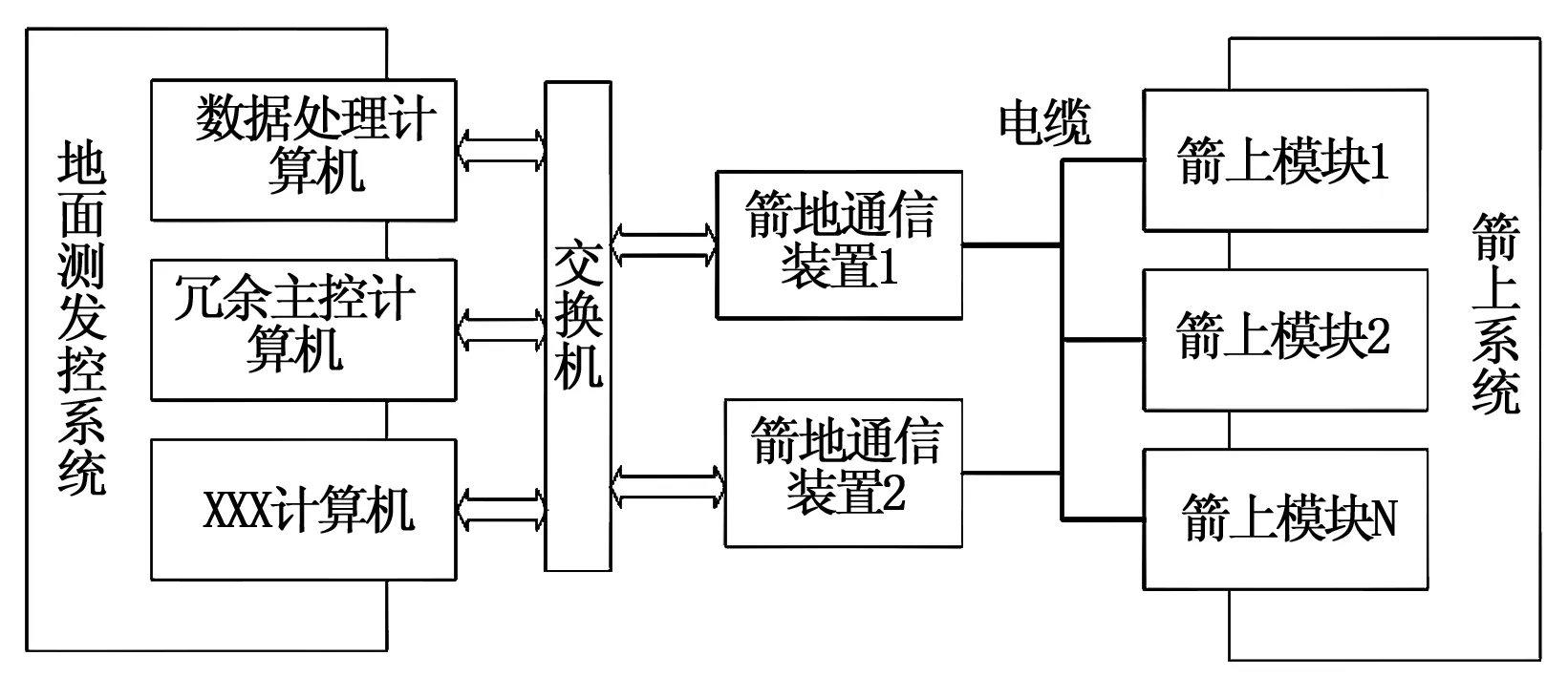

2.4 双机冗余备份设计

双机冗余备份是硬件设计中的技术难点和关键技术,在硬件设计时综合考虑后端地面系统和前端箭上系统的需求,采用两台硬件完全相同的通信装置构建整个系统。

通过在通信装置1和通信装置2之间的电缆互连,实现对箭上系统的全冗余,两台装置可以同时接收箭上下行的数据。

同时两台通信装置都处于正常工作状态,将收到的数据解析后同时发送给后端地面系统,实现对地面系统的全冗余,后端地面系统根据当班状态选取其中一路数据。

图4 主控软件设计

3 系统软件设计

3.1 ARM主控软件设计

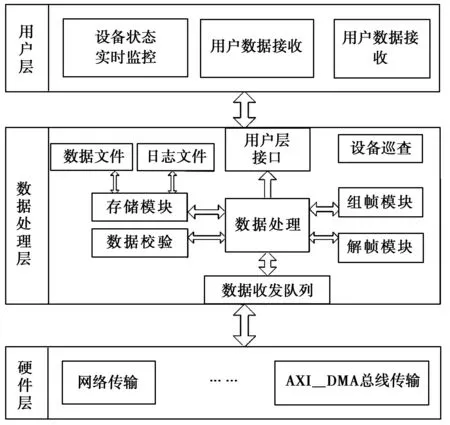

主控软件运行在Linux系统上,为了实现主控软件的通用性以及扩展性,开发时采用了多层次的软件架构[6],采用模块化设计,多层次接口标准开放,便于迭代开发和重构,应用于不同的场合,软件架构如图5所示。

图5 主控软件设计

主控软件作为设备运行核心,实现了设备上电后自启动,实时监测设备的自身状态以及链路接口的状态,通过网络与系统内其它软件进行通信,通过AXI总线与硬件层交互,对接收的指令及数据进行存储,实现网络数据通信及内部总线通信等关键功能,信息流如图6所示。

图6 主控软件信息流

3.2 FPGA软件设计

根据功能,对FPGA软件进行模块化设计[7]。其中串行通信模块进行高速串行通信接口的时序控制、根据高速串行通信协议完成数据的收发;8B/10编码模块完成发送和接收数据的8B/10B编解码;数据组帧发送模块以及数据接收解析模块对从网络接口接收的数据进行组帧、对外部LVDS/RS422接收的数据进行解析;参数配置模块以及系统交互模块完成FPGA与ARM之间的AXI总线控制以及RTC时钟授时。

FPGA软件工作时,数据流图如图7所示。

图7 FPGA软件信息流

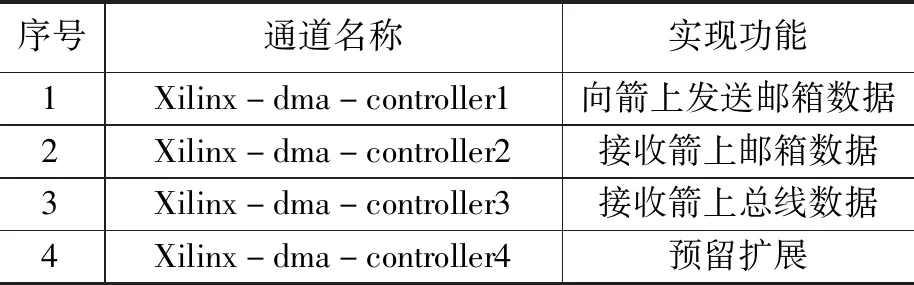

3.3 多DMA通道传输设计

箭地间通信具有数据量大、传输速度快、传输通道多的特点,采用单DMA通道进行通信会导致系统资源占用严重、调度不及时,从而导致数据丢失或异常情况,因此需要采用多DMA通道。多DMA通道并行传输的是本文的技术难点和关键技术之一。

本文采用了双DMA引擎四DMA控制器的方案实现多通道并行传输,各通道承担的功能如表1所示。

表1 多DMA通道分配

针对多通道并行工作时可能造成的系统资源竞争以及内存资源不足的情况,在软件中综合采用多线程技术、高精度定时技术、资源锁等方式,用高性能C语言开发了DMA传输模块,并封装为动态链接库,主控软件通过调用该动态链接库与硬件的总线通信,这种形式具有较高的扩展性以及可靠性。

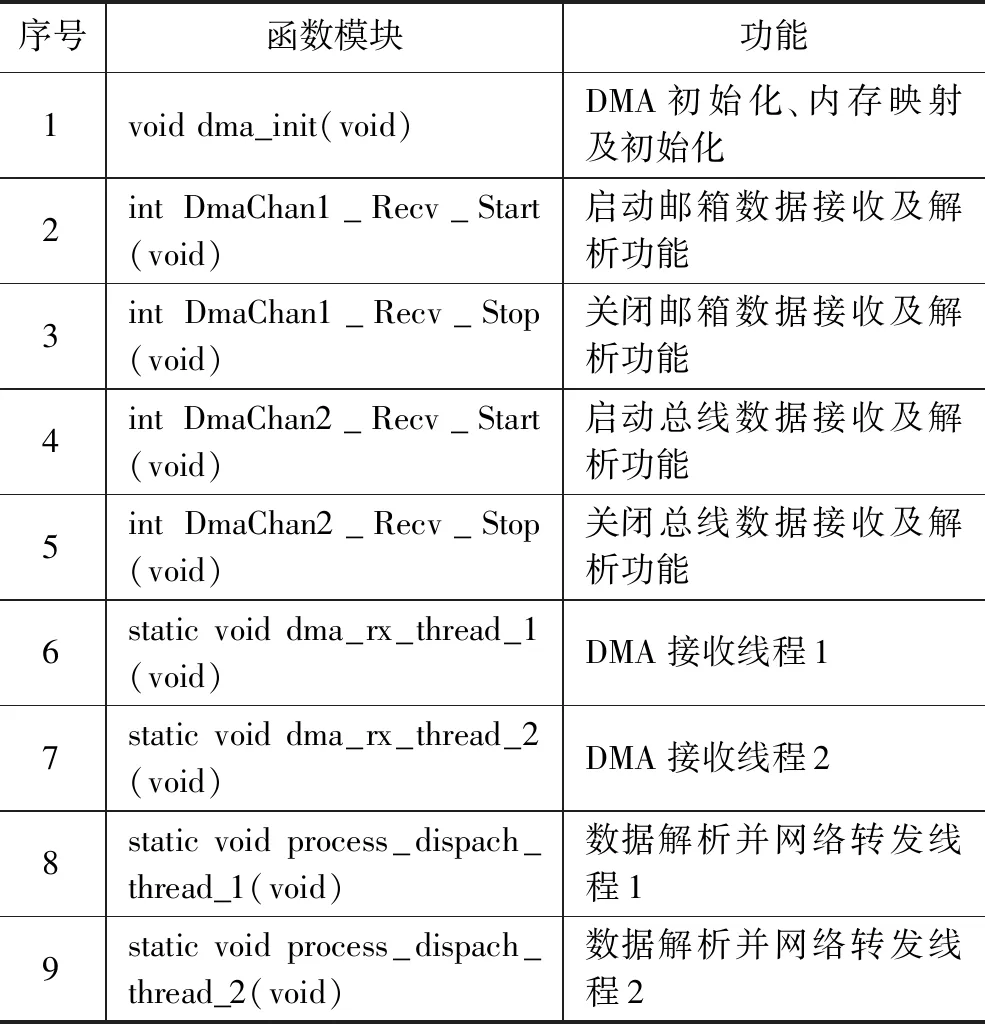

多DMA通道同时接收箭上邮箱和总线数据时,在接收线程中直接进行数据处理会导致单线程占用CPU时间长,从而引发系统CPU占用率大幅度提高,因此将数据接收以及数据处理分发分别用不同的线程来处理,涉及的主要实现函数如表2所示。

表2 主要实现函数

多DMA通道并行传输时,线程之间会彼此抢占CPU导致系统效率降低[8],因此综合利用通信装置的2个CPU,将DMA接收线程1和邮箱数据解析线程分配给CPU1进行处理,将DMA接收线程2和总线数据解析线程分配给CPU2进行处理,同时采用Linux下Select函数实现毫秒级的高精度定时器,对多个线程进行调度管理,避免了某个线程长期占用CPU,实现了CPU资源的合理分配[9]。

3.4 双网口热备份设计

本文采用双网口热备份(即双网口绑定)的方式提高箭上与地面网络数据传输的可靠性,双网口绑定是本文的关键技术之一。

在硬件设计时配置了2个独立的网卡,软件上通过Bond方式将两块网卡绑定到一个IP地址。通过这种方式,当一块网卡发生物理性损坏的情况下,另一块网卡自动启用,并提供正常的服务,实现了网卡的冗余,提高了网络的可靠性和设备的稳定性[10]。

双网卡热备份的实现步骤主要分为以下几步:

1)在系统制作时将bonding模块编译进内核,每次系统启动时可以自动加载bond模块,无需手动载入;

2)在系统中安装负载均衡工具ifenslave;

3)进入系统后,配置/etc/modules文件,将bond模式配置为模式1(Active-backup policy),设置链路连接状态监测间隔为100毫秒;

4)进入系统后,配置/etc/network/interfaces文件,将两个网卡都设置为bond0模式,同时设置虚拟网口的IP地址等信息;

5)重启系统并通过cat /pro/net/bonding/bond0查看并确认双网卡绑定状态,当前活动网卡以及备份网卡。

4 实验结果与分析

4.1 试验环境及步骤

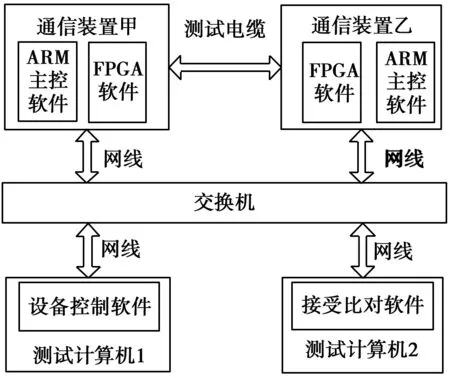

为了验证通信装置在远距离情况下高速数据传输的性能和可靠性,编写了设备控制软件和接收比对软件,并制作了长度为1米和150米的两根屏蔽双绞测试电缆,在室温条件下,对通信装置的各个功能进行了闭环测试,测试环境包含1台交换机,2台通信装置,2台测试计算机,测试环境中的设备及软件说明如表3所示。

表3 测试设备及软件

测试环境架构如图8所示。

图8 测试环境

传统的箭地通信装置采用5 Mbps的波特率,而新型火箭采用10 Mbps的波特率,因此本文在测试时,采用了5 Mbps、10 Mbps的波特率,以验证设备可否满足新老型号火箭的要求,同时也测试了20 Mbps的波特率,验证设备是否可以承受更高的传输压力。

由于箭上单机与通信装置传输数据时会经过8b/10b编码,且同时有3个通道在传输,因此测试时,设备实际的最大接收码速率为波特率的2.4倍。

具体测试步骤如下:

1)两台通信装置之间连接1米测试电缆;

2)启动通信装置甲、通信装置乙,设备内部ARM和FPGA软件上电自启动;

3)启动测试计算机1的自测软件,启动测试计算机2的接收比对软件;

4)自测软件设置两台通信装置的波特率为5 Mbps;

5)自测软件设置通信装置甲为发送状态,设置发送数据的码速率并启动发送;

6)通信装置乙通过硬件接口收到数据后转发给测试计算机2的接收比对软件;

7)接收比对软件实时接收数据并对数据进行判读,记录测试结果。

8)自测软件设置两台通信装置的波特率为10 Mbps和20 Mbps并分别重复4)~6)步骤,记录测试结果;

9)通信装置断电,换150米测试电缆连接;

10)重复2)~8)测试步骤,并记录测试结果。

4.2 结果分析

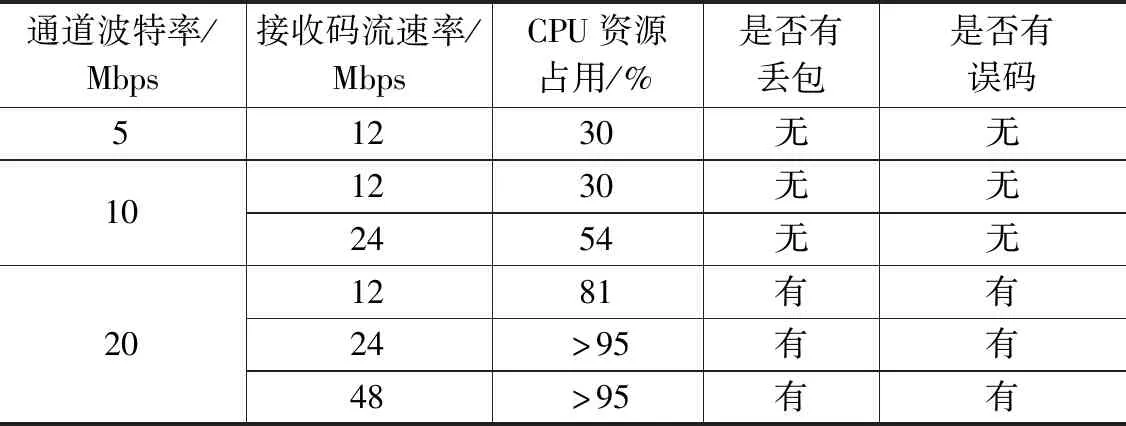

首先对150米电缆情况下的测试数据进行分析,测试结果统计如表4所示。

表4 试验结果(150米测试电缆)

测试结果表明,通道波特率设置为10 Mbps时,设备可以稳定工作,没有丢包和误码现象,可以满足新老型号火箭的通讯要求。而通道波特率设置为20 Mbps时,信号在链路层衰减过于严重,从而出现了丢包和误码现象,内部组帧和转义等操作受到误码影响,导致了CPU资源占用率大幅度提升。

接着对1米电缆情况下的测试数据进行分析,测试结果统计如表5所示。

表5 试验结果(1米测试电缆)

测试结果表明,在短距离通信情况下,通信装置工作稳定,没有丢包和误码现象。在短距离通信时,设备的CPU利用率主要受实际码流速率影响,不受传输波特率影响。

除此之外,还对通信装置的双网口热冗余,内部数据存盘功能,多通道独立工作以及装备自检功能进行了验证,测试结果都无异常。

箭地通信装置为部署在发射场塔架地下室,实现箭上数据到后端的通信转发功能的设备。传统方案采用的工控机配备多张PCI/PCIE功能卡,再加上显示器、鼠标、键盘等外设实现,而本文研制的通信装置,大小为标准的19英寸1U机箱,体积小,成本低且无需人工操作,提升明显,具体对比如表6所示。

表6 与传统方案对比

本文研制的通信装置,不仅体积缩小到原来的1/4,成本降低为原来的1/3,通信速率提高了一倍,且无需人工操作,更加安全可靠。

5 结束语

本文设计并实现的基于ZYNQ架构的全冗余高速箭地通信装置,目前已成功应用在某新型低温液体运载火箭上,该通信装置具有小型化、成本低、扩展灵活、运行可靠和性能优越的特点,后续可广泛应用在我国航天发射领域以及地面通信领域。