基于FPGA 的千兆以太网采集传输设计

2021-07-26周尧

周尧

(第七一五研究所,杭州,310023)

随着水声领域技术的发展,大吞吐量实时数据服务、实时信号传输系统的需求越来越迫切。同时,系统设备不断向集成化、网络化发展,从20 世纪80年代开始,以太网就成为最普遍采用的网络技术[1]。1996 年7 月,IEEE 802.3z 千兆以太网任务工作组研究制定了千兆以太网的帧格式与冲突处理方法,并规范了单模、多模光纤及铜缆标准[2]。2001 年,SUN L等人提供了三层交换机为核心的千兆以太网方案[3]。2009年,赵金保等人设计了以DSP为核心、基于千兆以太网的数据采集与处理系统[4]。相对于DSP 而言,FPGA 具有高灵活性、可并行执行、可扩展性和可擦写性等特点[5],不仅对AD 芯片引脚时序的同步控制更为精准,更方便对系统进行后期的维护和升级。同时,在FPGA 中集成千兆以太网的MAC 子层可以有效降低系统成本,简化布线难度,非常适合小型高速采集系统的应用。目前,在水声领域中基于FPGA 的千兆以太网应用案例较少,本文为水声领域中千兆以太网的应用提供一定的参考。

1 基本原理

1.1 采集

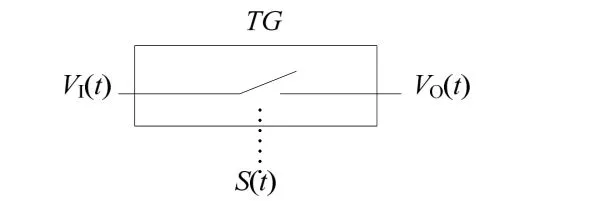

模拟信号转化为数字信号一般经过采样、保持、量化和编码。图1 是取样电路结构。模拟信号输入后,通过采样将随时间连续变化的模拟量转换为时间离散的模拟量。采样电路取得的模拟信号转化为数字信号都需要一定的时间,为了给后续的量化编码过程提供一个稳定值,每次取得的模拟信号必须通过保持电路保持一段时间。

图1 取样电路结构

图2 是取样-保持控制电路结构,由输入放大器A1 与输出放大器A2、保持电容C 和开关驱动电路S 组成。该电路工作状态由逻辑电平控制,具有两个稳定的工作状态:①跟踪状态(S 闭合),在此期间它尽可能快的接收模拟输入信号,并精确的跟踪模拟输入信号的变化,一直到接到保持指令为止;②保持状态(S 断开),对接收到保持指令前一瞬间的模拟输入信号进行保持。

图2 取样-保持控制电路

图3 是取样-保持电路的工作时域图。在t=t0时,开关S 闭合,电容被迅速充电,在t0~t1时间间隔内是取样阶段;在t=t1时刻,S 断开。若A2 的输入阻抗为无穷大、S 为理想开关,这样可认为保持电容C 没有放电回路,其两端电压保持为VO不变,t1到t2的平坦段就是保持阶段。

图3 取样-保持电路的工作时域图

1.2 传输

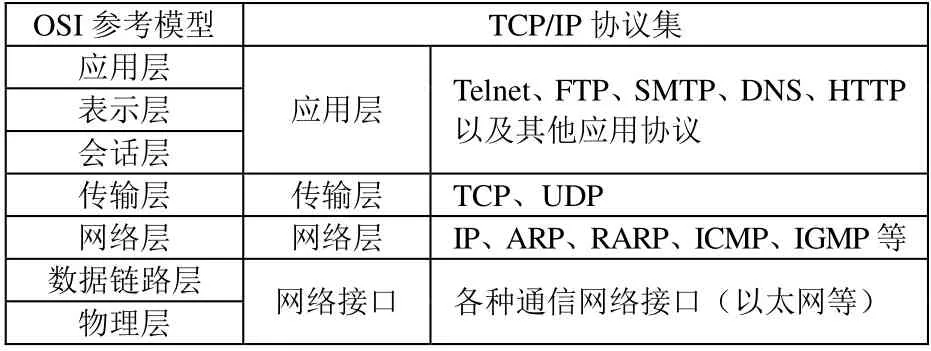

国际标准化组织制订了OSI 模型[6],把网络通信的工作分为七层,每一层负责一项具体的工作,然后把数据传送到下一层。见表1。OSI 网络通信协议模型是一个参考模型,而TCP/IP 协议是行业应用标准[7]。TCP/IP 是一个协议族,也是按照层次划分,见表2。

表2 TCP/IP 四层模型

PHY(Physical Layer)是IEEE802.3 中定义的一个标准模块。利用传输介质为数据链路层提供链接,尽可能屏蔽掉具体传输介质与物理设备的差异,实现比特流的透明传输。另一个重要的功能就是实现CSMA/CD 的部分功能,可以检测到网络上是否有数据在传送。

MAC(Media Access Control)由硬件控制器及MAC 通信协议构成。该协议位于OSI 七层协议中数据链路层的下半部分,主要负责控制与链接物理层的物理介质。

从硬件角度来看,以太网接口电路主要是由PHY 、MAC 两部分组成,工作在OSI 七层模型的物理层和数据链路层。

1.3 总体结构

图4 给出了本系统的总体结构框图,完成基于FPGA 多通道同步采集及千兆以太网发送系统应用层到数据链路层的搭建。

图4 总体结构框图

ADC 选用ADS1271,该器件集成了数字滤波器,具有109 dB 信噪比,通带纹波小于0.005 dB,可提供最大105 kSPS 数据速率。FPGA 选用Xilinx公司Virtex-5 系列芯片XC5VFX70T,具有44 800个LUT、148 个BlockRAM、32 个BUFG、12 个DCM 以及360 个可用IOBs 引脚,提供千兆MAC硬核。

在模拟侧,FPGA 搭载多通道ADC 采样驱动控制器,实现多通道模拟数据采集工作。在网络侧,FPGA 搭载MAC,将多通道AD 采样数据按以太网帧格式封装,通过MIIM(GMII)接口发送到PHY中。PHY 把从MAC 收到的并行数据转化为串行流数据,按物理层的编码规则把数据再变为模拟信号,经网络变压器进行信号增强和抗干扰处理后,发送到PC 端。

2 方法实现

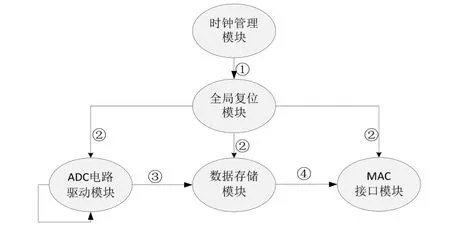

FPGA 中主要搭建了时钟管理模块、全局复位模块、ADC 电路驱动模块、数据存储模块、MAC接口模块等,FPGA 各模块的主要功能见表3。

表3 FPGA 各模块的主要功能

图5 是功能模块运行状态图。从FPGA 上电开始,对各模块运行状态进行说明:①FPGA 上电后,检测DCM 是否完成时钟LOCK 锁存,产生全局复位脉冲;②全局复位模块收到全局复位脉冲后,对各模块进行全局复位;③ADC 电路驱动模块循环产生ADC 驱动时序,并将从ADC 中读出的数据存储到数据存储模块;④当数据存储模块存放了N个采样点后,向MAC 接口模块请求发送数据,MAC 接口模块收到请求后,将N个采样点的数据从数据存储模块中取出并按以太网帧格式封装后,通过MAC层接口发送到PHY 侧。

图5 功能模块运行状态图

2.1 ADC 驱动实现

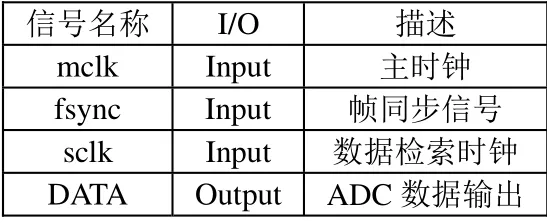

采用24 bit 位宽delta-sigma 模数转换器ADS1271实现ADC 驱动。FPGA 与ADS1271 之间采用FRAME-Sync 接口,信号描述见表4。

表4 FRAME-Sync 接口

驱动时序如图6 所示。每个采样周期需要256个mclk、64 个sclk、1 个fsync,即fmclk:fsclk:ffsync= 256:64:1。其中,fsync 的边沿与sclk 的下降沿对应;sclk 下降沿与mclk 的下降沿对应;采样点在fsync 上升沿时更替;DATA 在sclk 的下降沿从高bit 位(MSB)开始依次放置到总线,共24 bit,DATA在sclk 的上升沿被获取。

图6 ADS1271 驱动时序

2.2 MAC 接口实现

FPGA 搭建千兆以太网MAC 侧与PHY 侧进行通信,其接口定义见IEEE802.3-2000[8]。目前,常见的千兆网接口有三种,包括GMII、RGMII 和SGMII。采用数据位刷新率较低的GMII 接口作为MAC 与PHY 接口,信号定义见表5。GMII 采用8位接口数据,工作时钟125 MHz,传输速率可达1000 Mbps。兼容MII 所规定的10/100 Mbps 工作方式。GMII 支持1000BASE-TX 标准。

表5 GMII 接口信号定义

网络建立后可忽略MDIO、MDC,全双工运行时可忽略CRS、COL 信号。IEEE802.3 标准中仅对发送通道中接收端的建立时间(Setup time)和保持时间(Hold time)作出规定。即数据在时钟上升沿前保持稳定,在时钟上升沿后继续保持一段时间不变。

3 仿真分析

在ISE 开发平台下,采用Isim 仿真工具完成系统中各功能模块的功能仿真(前仿真),针对基于总体结构框图设计对所创建的逻辑进行验证。

图7 是ADC 驱动时序仿真图。对于FPGA 来说,o_mclk、o_sclk、o_fsync 为输出信号,i_ADin为输入信号。shiftdata[23:0]为24 bit 移位寄存器,o_ADdata[23:0]为24 bit 采样数据的输出。shiftdata在sclk上升沿时移位采样i_ADin的数据。自o_fsync上升沿后的第24 个o_sclk 上升沿完成该采样点24 bit 采样数据o_ADdata[23:0]的锁存和输出。

图7 ADC 驱动时序仿真

图8 是GMII 接口时序仿真图。这是一个UDP报文的仿真,共计74 byte,按以太网帧格式分解为:

图8 GMII 接口时序仿真

8 byte 前导码(7 个0x55,1 个0xd5)+14 byte以太网帧头+20 byte IP 帧头+8 byte UDP 帧头+20 byte UDP 数据位+4 byte CRC 校验位。

4 工程应用

根据系统架构,搭建了低频阵52 通道实时采集传输系统硬件平台,实现了52 通道24 kHz 采样率的同步采集上传、命令接收/回应、状态信息上行等功能。低频阵通道信噪比高达109 dB,各通道相位偏差±4°、峰峰值偏差在5%以内满足技术指标。

FPGA 采用Xilinx 公司Virtex-5 系列芯片XC5VFX70T,开发环境为ISE14.6。方案实现中,FPGA 中采用了两个全局时钟:6.144 MHz 时钟为多通道ADC 采样驱动器的全局时钟;125 MHz 时钟为千兆MII 接口的全局时钟,采用FIFO 作跨时钟域处理。FPGA 消耗占用逻辑资源情况见表6。以太网物理层芯片采用88E1111,与以太网的接口采用GMII。项目采用4 块52 通道的采集传输平台构成208 通道的采集传输系统,连续3 天的烤机,设备性能可靠,各项指标满足要求。

表6 FPGA 消耗占用逻辑资源

5 结束语

本文采用Virtex-5 系列芯片XC5VFX70T 在ISE14.6 开发平台下,搭建了基于FPGA 的千兆以太网采集传输系统,实现4 块52 通道水声信号的同步采集、传输工作。与基于ARM、DSP 的千兆以太网系统相比,本文的采集传输系统时序控制更为精准、可调用I/O 引脚更丰富,更适合项目后期的维护和升级。在后续研究中,将关注以光纤为媒介的千兆网传输系统,进一步提升传输距离。