基于FPGA的口袋实验装置示波器设计

2021-07-11朱铁柱

张 凡,黄 浩,朱铁柱

(1.淮阴工学院电子信息工程学院,江苏淮安 223001;2.淮阴工学院江苏省湖泊环境遥感技术工程实验室,江苏 淮安 223001)

基于FPGA 的数字示波器在功能控制和数据处理性能的优越性突出。从数字系统方面来说,系统性能取决于系统参数,通过改变参数很容易实现为不同的应用场景选择合适的数字系统[1-3]。数字示波器可以灵活地适应多路信号,通过时分复用一套示波器就可以通过片选信号,分时处理几路模拟信号,有效地减少了电路资源浪费;还可以根据面向对象的不同以及用户的不同需求选择不同的算法[4-6]。此外,数字示波器具有精度高、抗干扰能力强的优点,可以实现数字编程等模拟示波器无法实现的功能[7-8]。

文中设计了一款智能数字化数字示波器系统,设计指标如下:采样精度12 位、幅值范围-5~+5 V、测量频率范围100~10 MHz、水平灵敏度20 mV/div,垂直灵敏度0.1 μs/div。

1 系统硬件设计

1.1 硬件设计

以FPGA 作为核心的主控芯片,其外围电路比较简单,因为FPGA 内部集成了大量电路模块,不需要外接太多的电路就可以实现想要的功能,如产生分频的锁相环。FPGA 内部嵌入式软核处理器MicroBlaze、DSP 资源,所以FPGA 既可以使用DSP 资源实现相关算法,又可以实现控制功能。此外,FPGA 可实现并行处理,协调控制能力强,可在内部实现通信接口等功能[9-11]。所以,该方案相对于MCU和模拟示波器方案有着独特的优势。

信号首先经过信号调理电路即程控衰减放大电路和过压保护电路进行处理,AD 转换电路对外部信号进行采样,将模拟信号转换为数字信号。FPGA 开发板外接控制交互电路(如按键、拨码开关、旋转编码器等)、片内存储电路、VGA 显示电路。硬件设计框图如图1 所示。

图1 硬件框图

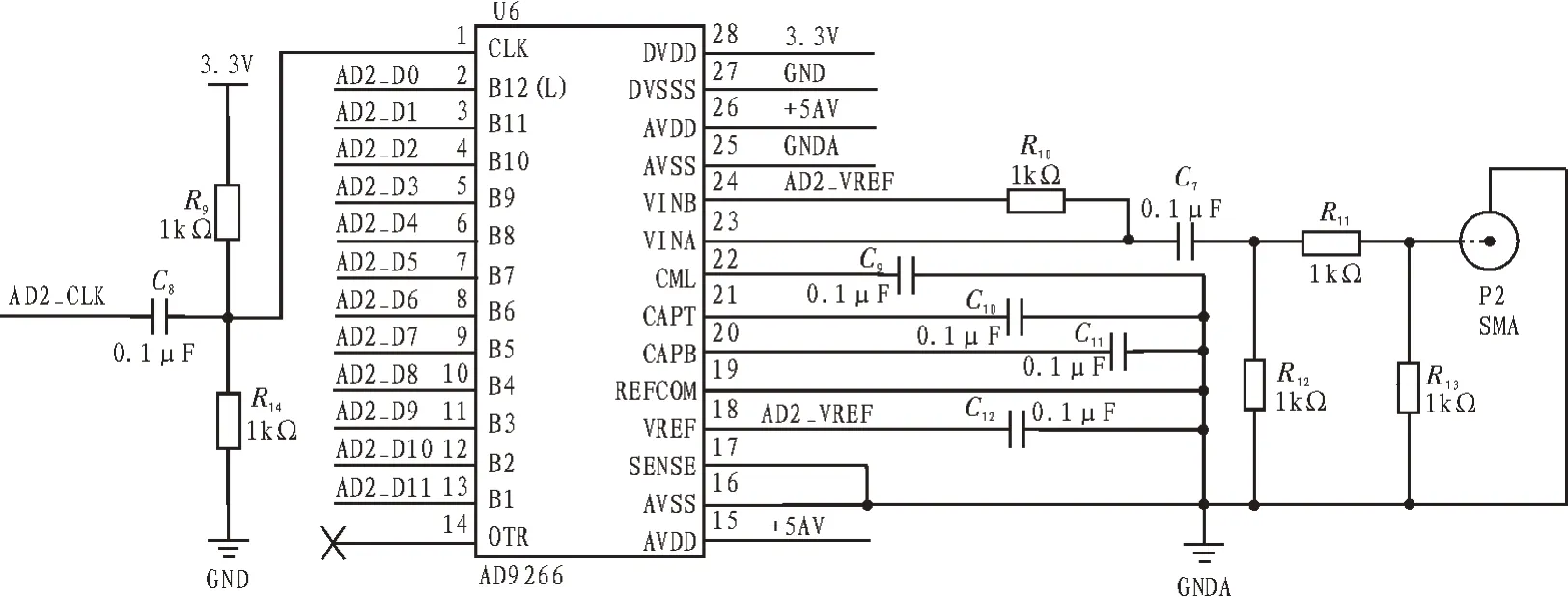

1.2 模数转换电路AD9266

此次设计所采用的是型号为AD9266 的高速AD模块,两块65 MPS 的AD 芯片集成在一块电路板上,既可以实现多通道的功能,也可以为之后的欠采样技术等效采样提供硬件支持,还可以满足高速数据采集与处理的要求。FPGA 完成对双路AD 转换的时序控制和数据读取功能。

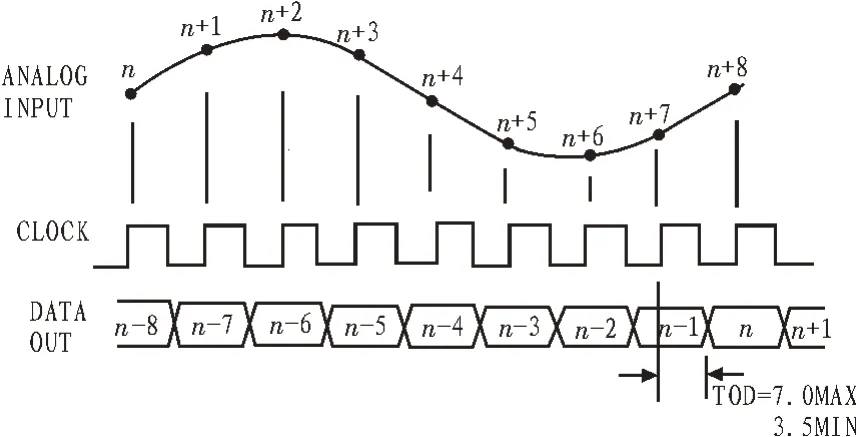

AD9266 采用多级差分流水线架构,可以通过一定的时序控制实现FPGA 开发板的通信功能,控制时序如图2 所示。用户可以选择硬件如SENSE引脚的外接电压值,从而改变输入信号的范围和直流分量[12-13]。

图2 AD9266时序图

AD9266 芯片内部自带采样保持放大器,在中频段,通过等效采样和欠采样技术,实现更高频率的模拟信号采集。设计中选择单端输入的模式,采用SMA 接口直接接入信号。

1.3 电压衰减电路和采样保持电路

芯片生产厂商在内部集成了片内基准电压源和高性能的占空比稳定器,可以实现任意占空比的时钟,完成对信号的采样和采样保持,具有高效和方便的优点。

输入阻抗也是示波器的关键指标,输入阻抗高可以降低对待测电路的影响。AD9266 输阻抗很高,电源电压范围灵活,相位误差和差分增益可忽略,在示波器应用中适合作示波器的前级信号调理。

根据原理图,配置的AD9266 基准电压只有2 V,但是2 V 的电压在正常的示波器使用中是远远不够的,所以设计了一款电路,如图3 所示,可以将输入范围扩大至-4~+4 V。

图3 不使用运放的电压衰减电路

在另一种方案中,采用带宽为145 MHz 的快速场效应管电压反馈放大器,该放大器的工作噪声低,属于单电源供电,与单极性ADC 配合单路放大器使用,所以非常适合用来作示波器的前级衰减运放。通过运放将-5~+5 V 衰减到-2~+2 V 的范围内。

电压计算公式如下:

当Vi=-5 V 时,对应Vo=1 V,当Vi=5 V 时,对应Vo=3 V。输入电压就可实现从10 V 衰减到参考电压配置的2 V。

2 软件程序设计

2.1 系统工作流程

示波器系统工作流程图如图4 所示。系统上电时,FLASH 中的程序会由配置电路配置到FPGA 中,显示界面初始化,ADC 开始采集数据。

图4 软件流程图

判断触发条件,如果满足触发条件就开始保存ADC 的数据,采集的数据存入RAM1 和RAM2,分别供FFT 模块和波形显示模块调用,数据的前后差值存入RAM3,启动测频模块和测幅模块。

测频模块通过滤波将ADC 采集到的信号变为方波信号,并计算周期。如果是自动控制模式,则根据周期更改显示模块和测幅模块的参数,如果不是,则根据按键或者旋转编码器的值更改参数。

下一步进行快速傅里叶变换,并将结果存入RAM4。显示界面调用RAM2 和RAM3 的数据显示波形,存入RAM4 中的数据显示傅里叶变换的结果。

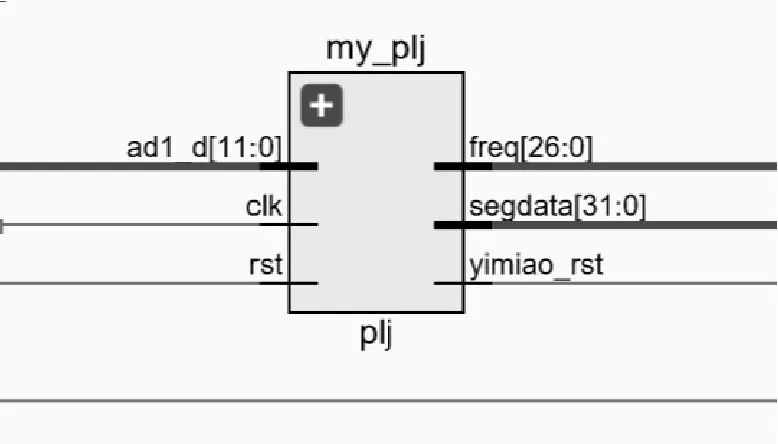

2.2 频率计模块

频率计数常用的方法有两种:周期法测定频率和直接测量频率。示波器测量的信号频率范围大、频率高,所以采用周期法测频[14]。

为了排除噪声信号的干扰和减少外围的器件,没有选择过零比较器,而是利用软件实现了一个施密特触发器,将离散的正弦波信号滤波为方波信号,这样就可以通过软件实现计数滤波后的上升沿次数,计数值就是信号的频率,如图5 所示。

图5 频率计框图

测得的频率信号会被采样模块和波形显示模块调用,根据频率的值更改采样模块的参数。因为采用的是等效采样,需要产生与信号频率相差1 时钟周期的方波,作为ADC 的时钟信号,因此在测量中最好采用等精度测频,以避免产生的时钟信号因此受影响。

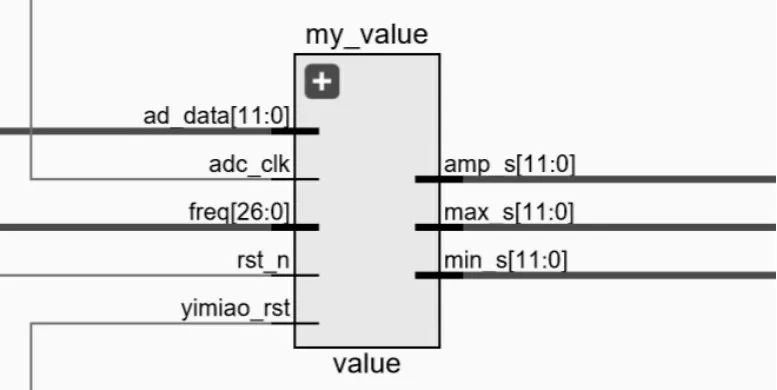

2.3 测幅模块

测幅模块记录每一个周期的峰峰值,最后计算平均值。为了提高计算的精度,引入了周期参数,如图6 所示。在实际应用中,信号往往会叠加周期性的噪声。当噪声频率低于信号频率时,根据测频模块测得的周期,可以只在一个周期内寻找最大值和最小值,这样可以一定程度上避免低频信号对测幅模块的影响。连续10 次测得这样的信号后,就可以计算平均值,输出信号的幅度值。

图6 测幅框图

2.4 PLL模块

PLL(锁相环)是FPGA 内部重要的时钟资源。利用锁相环可以对时钟进行分频、倍频、相位调整。PLL 基于压控振荡器VCO 获得实际想要的输出频率,而MMCM(混合模式时钟管理器)基于可变延时线技术,当时钟信号特别纯净时,分频操作不用PLL和MMCM,因为会引入延迟和偏斜[15-16]。而PLL 可以自身通过压控振荡器产生震荡,输入时钟用来产生基准。在设计中,ADC 实时采样时钟频率为50 MHz,等效采样频率为125 MHz,故需要65 MHz 的时钟,并使用VGA 显示时钟,如图7 所示。

图7 PLL框图

2.5 缓存模块

设计的缓存模块使用FPGA 内部BRAM 资源。在赛灵思FPGA 内部,有两种RAM:资源块RAM 和分布式RAM。分布式RAM 是消耗赛灵思特有的SLICEM,会消耗逻辑资源但时序性能好,是非常珍贵的资源。文中设计对时序要求不高,且片上资源足够,所以不采用分布式RAM。

缓存框图如图8 所示,中例化了4 个双口RAM,分别作为波形数据、波形差值数据、FFT 输入数据、FFT 输出数据存储缓存。波形数据和波形差值为八位,深度为1 024,每512 个数据显示一个周期的波形。另外,IP 核选择配置额外的输出寄存器,提高存储器使用性能,但读取值要延时一个周期。为避免冲突,采用异步时钟。读数据采用VGA 接口以65 MHz 的频率读取,写数据采用ADC 采样时钟,配置为读优先,这样可以保证当一个端口执行写操作时,读取无效。

图8 缓存框图

2.6 采样模块

示波器的采样功能由采样模块实现,提供对AD芯片的时钟控制和数据处理功能,输入测频信号的数值来对AD 芯片进行自动控制。当被测信号频率高于示波器实时采样预设的频率阈值时,示波器采用等效采样;否则,示波器采用实时采样。

实时采样的原理简单,AD 芯片内部自带了采样保持稳定功能,实时采样时只需将时钟信号分频给AD 芯片,就可以按照想要的次序进行采样。

采样模块框图如图9 所示。当等效采样时,PLL通过压控振荡器倍频到125 MHz,根据测得的频率生成和信号相差一个PLL 输出时钟周期的信号。这样根据差频法的性质,采样的等效采样率即为125 MHz,因此可以在AD 芯片性能不够的情况下实现对信号的欠采样。

图9 采样模块框图

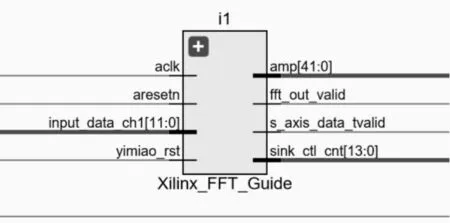

2.7 傅里叶变换模块

Xilinx 提供了FFT IP 核,可以直接例化使用。FFT IP 核具有12 个通道,不同的通道可以针对不同的计算点数和信号频率等计算参数实现不同的工作模式。通过设置数据类型、数据位宽、相位因子、输出指令来调整输入输出的格式,可以根据用户的需求方便地实现FFT 算法[17]。

傅里叶变换框图如图10 所示,这里选择1 通道,对1 024 个点进行操作。选择工作模式时,IP 核可以根据所需要的处理速度,配置成基2、基4、突发模式、流水线模式,通过面积和资源的互换实现自动配置。文中根据资源和性能的取舍选择基4 模式。

图10 傅里叶变换框图

在使用时,存在三类信号:基本的时钟和复位信号、AXI 的总线信号和状态线信号。AXI 的总线信号负责命令的输入和数据的交互。状态线信号包括started 开始转换信号、溢出的overflow 信号等。

文中通过testbench 来验证FFT 模块的结果,系统时钟(即FFT 计算时钟)为100 MHz,因此频谱范围为0~50 MHz。使用Matlab 生成低频与频率更高的正弦波信号A 和B,分别写入txt 文件。通过读取文件的正弦波信号,并转换为testbench 的输入信号,对电路进行仿真,分析FFT 的功能。

信号的频率越高,经过变换后尖峰要比信号更靠近中间。在有效信号持续的时间内,很明显可以看到低频信号的采样结果要比高频信号采样的结果更加精确,因为vivado 仿真工具会对信号的值进行压缩显示,频谱图实际波形与Matlab 仿真类似。

2.8 显示界面模块

界面模块由VGA 时序生成模块和网格生成模块组成,VGA 时序模块主要由计数器组成,计数单位是显示一个像素所需要的时钟。文中VGA 模块像素大小为1 024*768,每秒刷新60 次,每次刷新行有效和场有效信号计数器分别计数1 024 次和768 次,同步信号可以通过查询资料设定相关参数,显示模块框图如图11 所示。

图11 显示模块框图

在满足VGA 时序的基础下,网格叠加模块根据横纵坐标网格表达式更改VGA544 颜色参数的值,从而显示横向和竖向网格。

2.9 波形和频谱图显示模块

波形和频谱图显示模块如图12 所示。该模块用于接受已经生成的网格VGA 时序。PLL 生成的65 MHz 的时钟作为RAM2 和RAM3 的读取时钟。

图12 波形和频率谱模块框图

在实时采样模式下,采样多个周期的波形会超出显示所具有的功能。系统具有自动控制的功能,频率计模块已经测得了频率,因此示波器可以在不外接输入调整频率的情况下对波形进行调整[18]。在模块中根据输入信号的时钟频率表达式控制ADC采样存储的间隔,这样屏幕就可以始终显示两个周期的波形。

3 实验分析

上述过程实现了基于FPGA 的数字示波器设计,但是对于实际采集系统的精度和系统留下来的缺陷无法确定,为此选择用FPGA 和DA 芯片通过DDS 的方式模拟正弦波、方波、三角波的功能[19]。在实验过程中,将AD 和DA 直接相连,将待测信号的生成参数和实验数据进行对比,分析示波器系统测量的效果。实验结果在测量信号频率低于50 MHz 时,误差不超过0.1%,测幅误差在校准后误差不超过5%,波形和频谱显示效果分别如图13、14 所示,可见基本实现了示波器的功能。

图13 正弦波波形图

图14 正弦波频谱图

4 结束语

文中通过Artix-7 FPGA 开发板和高精度ADC芯片实现了数字存储式示波器,实时采样可以达到65 MHz,通过等效采样还可以提高示波器的采样频率,并提高示波器的数字处理能力,降低示波器的成本,提高示波器的集成度。