多路数据采集传输系统的FPGA设计与实现

2021-06-29李茂林

李茂林

摘 要: 设计一种采用FPGA的数据采集传输系统。以FPGA为逻辑控制核心,通过RS485接口接收上位机指令,数据传输采用SDLC(同步数据链路控制)协议以提高可靠性。FPGA采集六路AD数据以及八路温度数据,这些数据经由DSP处理之后存储至FLASH中。FPGA根据上位机指令,读取FLASH中相应的数据并通过RS485接口上传至上位机。经系统测试验证,该设计能够满足技术要求,数据的采集、存储、传输均正确,为后续工作提供了保障。

关键词: FPGA; 采集传输; 存储; SDLC协议; FLASH

中图分类号:TP31 文献标识码:A 文章编号:1006-8228(2021)04-49-05

Abstract: A data acquisition and transmission system based on FPGA is designed. FPGA is used as the logic control core, and RS485 interface is used to receive instructions from upper computer. SDLC (synchronous data link control) protocol is used for data transmission to improve reliability. FPGA collects six channels of AD data and eight channels of temperature data, which are processed by DSP and stored in FLASH. According to the instructions of the upper computer, FPGA reads the corresponding data in FLASH and uploads it to the upper computer through RS485 interface. It is verified by the system test that the design can meet the technical requirements, and the acquisition, storage and transmission of the data are correct, which provides a guarantee for the follow-up work.

Key words: FPGA; acquisition and transmission; storage; SDLC protocol; FLASH

0 引言

随着国际形势的不断变化,国家安全越来越得到人们的重视。光电系统广泛应用于探测系统、导弹防御、航空、红外探测等领域。光电探测技术,不仅需要不断地优化复杂的算法,还需要采集更加准确的前端数据[1]。系统选用FPGA作为主控芯片,利用其强大的并行处理能力,快速高效的完成数据的采集、存储及传输任务。系统设计对于开展后续数据解算等工作具有重要的意义。

1 系统总体设计

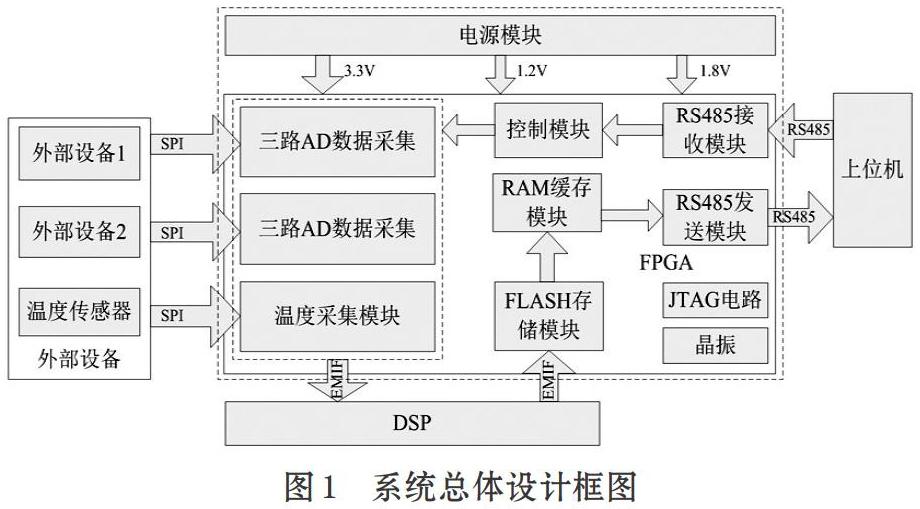

系统采用Xilinx公司的Spartan6系列XC6SLX45芯片作为逻辑控制核心[2],上电时启动对六路AD数据以及八路温度的采集,并将采集好的数据按照1KHz的频率通过EMIF接口发送至DSP,DSP对收到的数据进行相应的处理。FPGA和DSP通过握手信号进行信息交互,FPGA解析相关指令并控制FLASH进行擦除、读写操作。同时,FPGA通过RS485接口接收上位机发送的指令信息,在技术要求规定的时间内,完成数据的接收及发送。系统总体设计框图如图1所示。

2 系统总体设计

2.1 温度采集模块

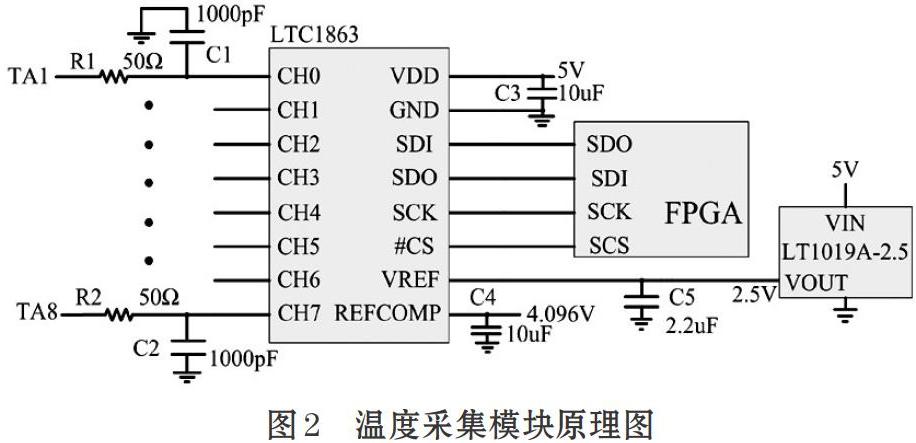

系统采用A/D转换器LTC1863实现对外部8个通道的温度采集。LTC1863芯片的分辨率为16bit,系统上电启动后,通过对芯片写入配置数据来完成不同通道数据的采集,数据传输波特率为1Mbps,采样频率为1KHz。温度采集模块的硬件原理图如图2所示。#CS为启动数据转換引脚,初始状态时#CS为高电平,当它变为低电平时启动一次A/D转换。在数据转换期间,LTC1863接收配置字节,并输出转换结果[3]。设计时,为了降低其他电路对LTC1863输入端的噪声及失真影响,在模拟输入之前增加了滤波电路。

2.2 RS485收发模块

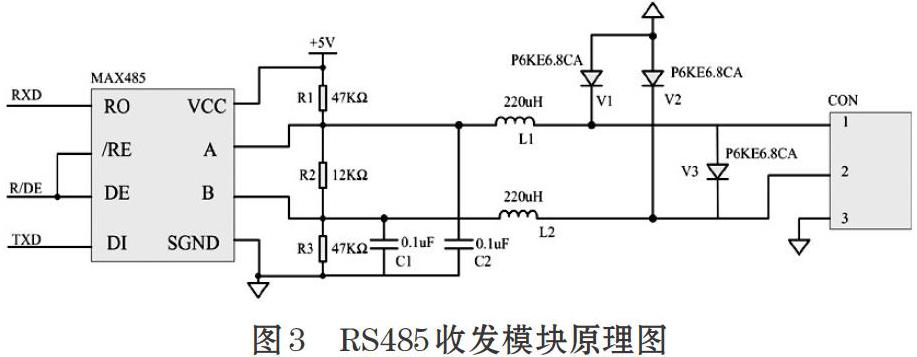

系统采用MAX485芯片实现FPGA与上位机的同步半双工通讯[4]。RS485收发模块的硬件原理图如图3所示,其中RE与DE管脚分别表示接收使能和发送使能,且均为低电平有效。当系统处于初始化状态时,设置R/DE=0,即接收使能。由FPGA根据系统时序来控制这两个管脚的使能切换。为了提高RS485通讯的可靠性,设计上采用了上拉电阻、下拉电阻以及瞬态抑制二极管P6KE6.8CA来对该芯片进行保护[5]。

3 系统软件设计

系统选用FPGA作为逻辑控制核心,通过RS485接口接收上位机指令。通过对接收到的指令信息进行解析,从而获取有效数据发送至DSP进行后续的数据处理。DSP将数据处理完成后,将通过EMIF接口,采用握手信号作为与FPGA进行数据交互的标志来对数据进行传输。FPGA接收到处理好的数据后,将其存储至FLASH中。当FPGA接收到指令时,读取FLASH中的数据,同时通过RS485接口上传至上位机进行显示及处理。系统软件设计框图如图4所示。

3.1 RS485接收模块

为提高数据传输可靠性,FPGA与上位机的通信协议采用SDLC协议。它通常作为主从设备之间进行通讯的一种协议[6]。SDLC协议的数据传输格式如图5所示,它主要由启动标志0x7E、目的地址、控制信息、数据、校验码及结束标志0x7E组成[7]。其中控制信息用于区分该帧数据是主设备发送的命令,还是从设备反馈给主设备的响应。

数据在传输过程中,会对除启动标志及结束标志以外的比特位进行“补0”操作[8],即:若连续发送五个“1”,则会补发一个“0”,然后继续按位发送数据。数据传输波特率为2Mbps。RS485接收模块由两部分内容组成,底层模块实现对启动标志及结束标志的识别,并对数据进行“去0”操作。顶层模块实现一帧数据的长度计算并进行数据发送。

首先底层模块为确保RS485模块上电时收到的0x7E是启动标志,采用一个16bit的移位寄存器对数据进行判断。当MAX485芯片管脚RE=0,即接收使能时,采样1bit并移至移位寄存器MSB,当采样次数为16时,对该移位寄存器进行判断。若高8bit字节为0x7E,而低8bit字节不为0x7E时,认为接收到的0x7E为启动标志,并发送一个开始标志给顶层模块;若为其他情况,则继续进行移位,直至移位寄存器中的值为0x7EXX(XX不为7E)。判断到启动标志以后,开始对数据按位进行“去0”操作。设计上采用两个4bit的寄存器count1、count2来对数据进行控制。count1用来计数收到连续数据位为“1”的个数,若计数不足5时,同时接收到的下一个数为0,则计数清零。若计数为5时,将继续接收下一个数据并对其进行判断。若为0,则在该周期内不做任何操作,等待接收下一位,且计数清零。若不为0,则发送一个异常标志给顶层模块进行处理。count2用来计数一个完整的字节,当经过“去0”操作之后的数据位计数至8时,即count2=8时,发送一个标志给顶层模块,表示一个字节接收完毕。同时,对16bit移位寄存器的低8bit进行判断,若为0x7E,则认为接收到了结束标志,底层模块将发送帧结束标志至顶层模块。

当顶层模块接收到开始标志时,将采样数据至FIFO中,同时进行长度length的累加。当接收到结束标志后,将写数据及数据长度写至EMIF接口相应地址上,通过与DSP进行握手来完成数据的传输。图6为RS485接收模块流程图。

3.2 FLASH存储模块

FPGA根据上位机指令对经DSP处理后的数据进行存储。依据指令,外部设备将发送八个文件的内容至FLASH中进行存储,因此需要对其文件位置进行扇区地址划分。系统上电后,FPGA依据指令信息,来对指定文件进行扇区擦除。擦除完成后,将文件内容存储至FLASH指定扇区相应的地址上。FLASH芯片与FPGA通过SPI接口进行信息交互,系统主频为160MHz,SPI时钟频率为40MHz。当FPGA接收到读文件指令时,FPGA将读取相应地址的数据并通过SPI接口发送至RS485发送模块进行后续数据处理。图7为FLASH的写时序图。

FPGA进行FLASH写操作时,首先需要发送写使能命令0x06,然后对配置寄存器进行初始化配置[9]。配置完成后依次发送写使能命令0x06、写指令0x02、写地址、写数据。由于每个文件包含800帧数据,每一帧有256个数据字节,FPGA采用按字节写的方式写数据至FLASH中,所以每写完一个字节,地址加1。当写完800帧数据后,FPGA发送完成标志给DSP,以便下一个文件内容的写入。

4 系统测试与验证

为实现对系统的测试与验证,分别对RS485收发模块以及FLASH存储模块进行了仿真测试,并采用chipscope对系统进行在线调试,验证了系统功能的正确性。

4.1 RS485接收模块仿真

由于数据在接收时需进行“去0”操作,若在接收的数据中,出现连续‘1的个数大于5时,系统将会认为接收异常,因此需对接收正常与接收异常这两种情况均进行验证。编写仿真文件,输入数据为0x7E、0xd5、0x53、0x9f、0xfb、0xf8、0xf2、0x7d、0xf8、0x7c、0x7c、 0x7E,对RS485接收模块进行仿真测试,测试结果如图8所示。

在数据“去0”过程中,error保持0不变,表示接收的数据未出现异常。“去0”输出的数据如图8中dataout[7:0]所示,对其进行放大显示,如图9所示,输出数据为0x7E、0xd5、0x53、0xdf、0x7d、0x7e、0xfe、0xc7、0xf7、0xf9、0x7E,测试結果与设计相符。

输入数据为0x7E、0xd5、0x53、0x9f、0xfb、0xff、0xf2、0x7d、0xf8、0x7c、0x7c、 0x7E,对其进行仿真测试,测试结果如图10所示,当检测到数据0xFF时,即出现连续五个以上的‘1,认为接收异常,error在一个周期内置为1,且当前这一帧数据不再进行发送。该模块将重新检测下一帧数据帧头0x7E,测试结果与设计相符。

4.2 FLASH存储模块仿真

为验证FLASH存储模块的功能,对其各模块进行仿真测试。图11为对FLASH中写操作模块进行仿真得到的时序图。为便于观察,模拟写入FLASH的文件1中的数据内容为0x00-0xFF。当该模块接收到写字节标志时,将要写入FLASH的数据字节进行暂存,然后发送写使能标志、写指令、写地址,最后写入暂存的数据。等待写操作完成后,开始接收下一个字节,并写入FLASH。图中写入文件数据首地址为0x010000,随着数据的写入,地址也在递增。

4.3 在线调试

系统采用ISE自带在线调试工具Chipscope对系统的输出进行在线调试。RS485模块工作方式采用同步半双工通讯,因此指令及数据的收发是不同步的。系统对数据进行存储、发送等操作均需依据指令信息。为验证FLASH存储模块及RS485数据发送模块之间的通讯是否正常,首先提前将数据0x00-0xFF写入FLASH中,然后对FLASH的读取、数据的发送进行在线调试。由图12可以看出,发送一帧的数据长度为262,包括帧头0x7E、目标地址0xD5、回应帧53、校验码0x6980和帧尾0x7E。数据发送长度正确,且实现了RS485模块的发送数据补零操作。

上位机通过RS485接口接收串行数据,对其进行“去0”操作后转换成并行数据显示,处理后的数据如图13所示。与系统发送的数据相一致,验证了该系统測试无异常,在满足技术指标的前提下,正确实现了数据的采集存储与传输。

5 结束语

本文提出的多路数据采集传输系统的设计采用FPGA作为系统控制核心,RS485作为数据传输接口,正确实现了多路数据的采集传输。经过一次通电24小时测试验证,数据传输速率达到2Mbps,且未出现丢帧、乱帧的现象,系统工作稳定,实时性好,可靠性高。利用FPGA软件搭建底层协议,可移植性好,进而降低了生产成本,为各个生产领域的数据采集系统提供了一种非常可靠且高效的方法,应用前景看好。

参考文献(References):

[1] 邓昌晟,刘昱,李海洋,王小松,张海英.ETC系统中HDLC协议解码控制器的Verilog HDL实现[J].微型机与应用,2017.36(19):30-33

[2] 李果萍,成龙,柴波.基于SDLC协议的同步RS 485总线控制器的设计[J].现代电子技术,2009.32(4):152-154

[3] 耿立中,王鹏,马骋,贾惠波.RS485高速数据传输协议的设计与实现[J].清华大学学报(自然科学版),2008.8:1311-1314

[4] Research on a 485-serial network architecture in intelligent uptown management. NI Haiyan,HU Chao,MA Changwang. Proc 2006 IEEE Conf on Mechatronics and Automation,2006.

[5] 蒋玉峰,张志明,崔麦会,尹业宏.RS-485图像数据并行传输协议的FPGA设计与实现[J].电视技术,2012.36(17):71-72

[6] 曹志锦,王永梁.基于RS-485的多机串行通信实验系统设计及应用[J].实验技术与管理,2002.5:65-67,70

[7] 高大勇,刘书信.一种基于FPGA的SDLC协议的通信板卡的实现[J].计算机光盘软件与应用,2012.12:175,177

[8] 岳绚,杨健.基于VHDL描述语言的高级数据链路控制协议实现[J].电气自动化,2012.34(2):16-18

[9] 陈晨,李志来,徐伟,金光.基于FPGA的高速同步HDLC通信控制器设计[J].电子设计工程,2010.18(8):175-178