微小型SMD压控晶振(VCXO)的研制与分析

2021-06-29浙江嘉康电子股份有限公司邹康俊倪鹏飞

浙江嘉康电子股份有限公司 邹康俊 杜 文 倪鹏飞

基于压控晶振理论研究,采用厚膜和二次混合集成技术,对VCXO的关键元件石英晶体谐振片设计以及变容二极管的选择及电路进行了分析,成功实现了体积为5.0×3.2×1.2(mm)的SMD微小型压控晶振,其频率稳定度、压控频率范围等方面都得到了明显的提升,尤其在封装形式上体积显著减小。并着重介绍了采用厚膜印刷的表面安装技术和压控晶振中频率的异常跳变分析与消除。

随着电子产品日益发展,电子产品的小型化甚至微型化需求突出,所以传统元器件的生存空间也越来越小,高度的集成化成为必然的趋势。而微小型压控晶振的突出特点是体积小,这对电路性能的改进,首先是元器件的选用提出来了更高的要求,尤其是石英谐振器和IC的选择与加工;而且要在保证压控晶振性能的基础上,尽可能少用元件。 压控晶振就是用外加电压对晶振的频率进行控制,压控晶振广泛用于晶振频率的电校准、锁相晶振、模拟和数字温补晶振、频率调制和频率捷变技术中。本文基于压控晶振理论,采用厚膜和二次混合集成技术,并通过多次对比实验与研究,攻克了VCXO的关键元件石英晶体谐振片及其他元件的选择、加工等难题,研制出了一款具有体积小、精度高等性能指标优越的微小型SMD压控晶振。

1 微型VCXO的电路原理及其结构

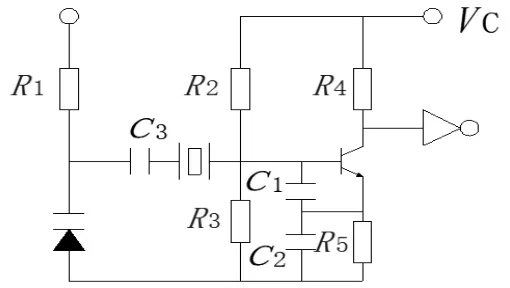

VCXO主要由石英晶体谐振器、变容二极管和振荡电路组成,其工作原理就是通过控制电压来改变变容二极管的电容,从而对石英晶体谐振器的频率进行调频,以达到线路使用频率调制的目的。VCXO作为频率可调的稳定频率源,其技术指标主要取决于压控网络的设计。为配合整机的小型化,本文研制、分析一款国际通用SMD5032基座晶体结构的压控晶振VCXO,如图1所示。

要在这样狭小空间里装配多种元器件而制造出VCXO,电路的合理设计和元件的使用装配需要大量的匹配试验,而我们采用厚膜印刷及二次混合集成技术很好的解决了这一问题。图1是VCXO外形结构,该产品的基本电路原理如图2所示。

图1 SMD5032 VCXO外形结构

图2 VCXO电路原理

此电路可以从10MHz到50.000MHz范围调整而稳定地工作;低频VCX0(1~10MHz)采用分频IC而获得所需各种了,只需调整C1和C2就能实现要求的输出频率,由于我们采用动态有源微调,晶体支路中串上的微调电容C就可以省掉了。电路中电阻是为电路提供偏置,对它们进行调整可获得需要的波形和幅度输出。R2、R3给电路提供一稳定的静态工作点,R4、R5对调整输出稳定的频率也能作出贡献,所以不能随意省掉。除振荡电路外,还加入了变容二极管控制电路和IC放大电路,以便实现压控频率变化和稳定输出功能。

2 压控晶振设计及分析

2.1 石英晶振的设计与分析

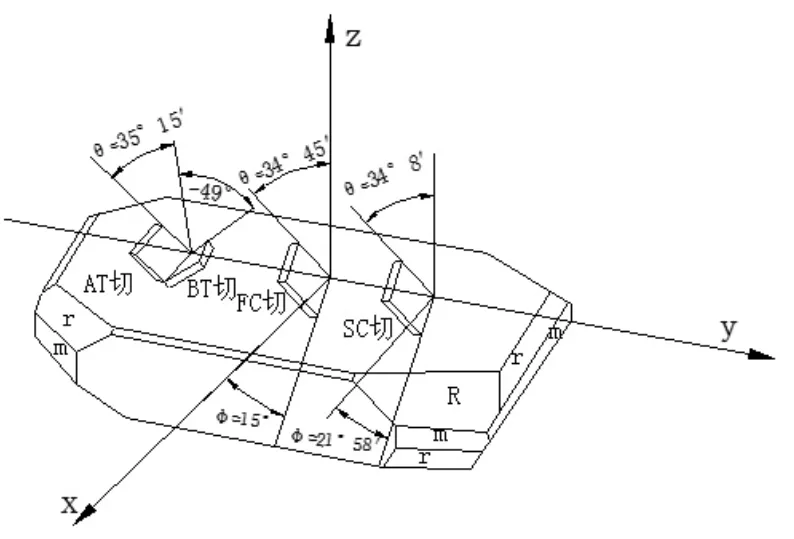

石英晶振是压控晶振的核心元件,要实现性能优越的压控晶振,必然少不了性能优越的石英晶振;而石英晶振的性能除了与水晶材料的纯度和结晶完美性(无气泡、无兰针、无位错、无裂隙、高Q值)有关之外,还与石英片的切角有关。常见的几种石英谐振器晶片的切角如图3所示。

众所周知,高频晶体大多采用AT切型,AT型石英谐振器的频率与温度的关系呈三次函数关系,因而它具有零温度系数点。因此,用AT切谐振器制成的振荡器具有较好的频率温度特性。

但AT切谐振器存在着两大缺点:

(1)存在较大的热过冲现象。热过冲使振荡器的频率从加电起,要经过一段时间的来回起伏才逐渐稳定下来。

(2)存在幅频效应较大。振幅过大时,频率会随振幅的增大而剧增。

AT切型以T0为参考,其频率—温度方程式为:

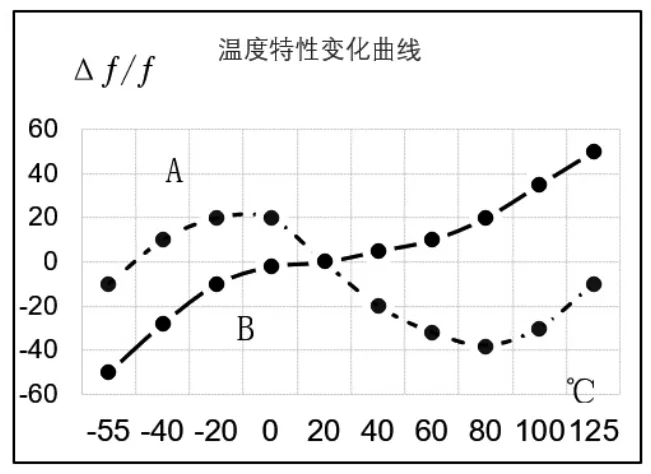

公式⑴中:T为任意温度,ɑ0、b0、c0分别为一级、二级、三级频率温度系数。实验得出频率—温度特性曲线图如图4所示。

图3 切型石英片的方位图

图4 AT切型的频率—温度特性曲线

图4所示是呈三次函数关系的曲线,最典型的是曲线A,由曲线A可以看出,当AT切型晶体使用在宽温范围,如-55~+125℃范围,有很好频率漂移。曲线B在-55~+125℃范围频率变化虽然很大,但在-10~+70℃这一温度范围内频率漂移却很小。要获得曲线B,对应16MHz晶体片切角为AT35o13,对应24MHz的晶体切角为AT35o15,选择这种切角对制作Φ2.5mm的谐振片适合,但对其它直径的圆片就不能用这个切割角度了。

由于VCXO体积所限,依据频段不同,我们采用Φ2.5mm(频段1.000—26.999MHz)和Φ2.0mm(频段27.000—50.000MHz)两种规格的晶体片。根据VCXO的特点,电极面积尽可能大,以便使VCXO压控范围增大。电极厚度用返回频率公式:Δƒ=kF2来计算,其中F为基频,K为常数也称返回系数,其取值范围由频率来定,即频率从1.000M~50.000MHz,取K值从现在0.8~0.3即可。晶体片的加工,只须按设计要求进行研磨、腐蚀、清洗、镀膜,均按常规工艺进行即可。

2.2 变容二极管的选择与分析

变容二极管作为压控振荡器中调频元件,变容二极管其性能和使用方法对压控性能的影响很大。变容管pn结的结电容Cj与加于变容二极管上的反向电压VR之间的关系为:

公式(2)中,Κ为常数,Φ为接触电势差,n为变容指数。

选择变容管参数时注意的几点:

(1)适合的变容管的中心值。压控晶振中谐振器的负载电容约为12~51pF,而控制电压的中值大致在-2~-5V的范围内。变容管的中值电容应满足这一要求,否则,振荡器将校不到标称频率,或者是变容管不能工作在合适区域。

(2)足够大的变容管Cj~VR特性的平均斜率,以满足压控总频偏的要求。

(3)满足变容管Cj~VR特性曲线的线性要求。在锁相晶振中以及在校准晶振频率准确度的电子校频电路中,变容管的非线性系数达30%,而在频率调制用的晶振中非线性系数应不超过3%。变容管本身的非线性系数很难小到3%,所以就要求压控电路设计中对变容管的非线性系数进行校正。简单而有效的办法就是将两个变容管串联使用如图5,正反向偏置的两个变容管的结电容相串联时,当VR=0时,串联电容为1/2Cj0。随着负偏的增加CjR越来越小,因而CjF对串联电容的影响越来越小,可以得到图6中虚线所示,这条曲线的斜率随着VR变化的非线性度得以减小。

图5 两个变容管的串联图

图6 串联变容管的Cj~VR特性

2.3 压控晶振IC的选择分析

实现VCXO小型化,采用了NPC公司生产的专用钟振IC(SM5000系列),这种电路块具有体积小和功耗低的特点,其基本性能在VCXO中的应用情况如下:

电源电压:3.0V~5.5V;电流:<10mA;功耗:250mW;工作频率:ƒ0或ƒ0/2、ƒ0/4、ƒ0/8(ƒ0为基频);输出波形:上升/下降时间满足钟振标准;占空比:40~60%;负载能力:1~10个TTL门或15PF CMOS/TTL兼容。

3 厚膜印刷及二次混合集成技术的应用

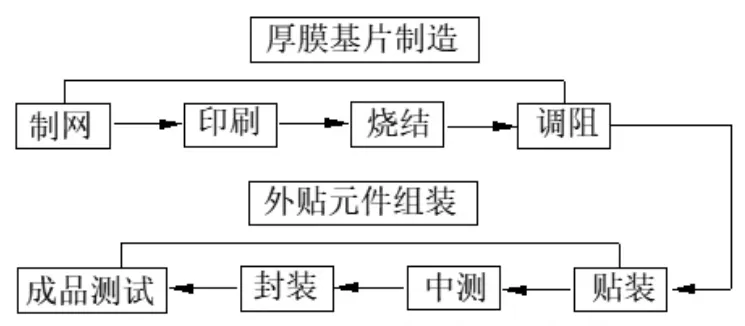

厚膜混合集成技术的主要特点是产品性能稳定,温度特性优越;适用于批量自动化生产,具有工艺简单、成本低、见效快等优点,便于工艺实现。主要工艺流程如图7所示:

图7 厚膜集成工艺流程图

3.1 工艺特点分析

(1)电路布线细线条化,利用陶瓷基板的热导率比PCB高二个数量级经及热稳定性好的特点,有效减少了电路布线面积。

(2)由于采用激光动态调阻技术,使得电阻精度大大提高,其精度可达到0.5%。

(3)采用表面安装元器件及细间距器件(Fine pitch Device)。

(4)二次混合集成电路中振荡专用IC、变容管、片式电容都采用SMT技术完成二次集成。

(5)封装采用贮能焊可经受-40~+180℃温度冲出,能满足气密性封装要求,实现了高密度组装。

3.2 关键工艺技术分析

(1)厚膜导体和电阻及高温介质均为高温烧成,应严格检查导体是否完整,不能有短路和开路发生,激光调阻应调至所规定的阻值上。

(2)元器件表面安装时应严格红外再流焊温度曲线控制,防止温度过高损坏元器件。

(3)必须采用弹簧作为晶体谐振片支架,保证优良的起振性能;频率微调时控制端需加上相应的电压,其值为控制电压范围的中心值。

4 压控晶振中频率的异常跳变分析与消除

在实际调试晶振中,实际会有振荡频率随压控电压的变化而突变的情况,我们用实验电路很好的研究了产生这一现象的原因,电路中采用了一只罗兰环作为电流监测器,用它可以测出出现异常频率突变时流过晶体电流的频谱如图8所示。实验时以R为移动参数,以晶体负载电容CL为自变量,测出基音振荡频率ƒ0与CL的关系如图9所示。实验结果表明,所有的频率异常跳变都发生在ƒ1L=ƒ3L/3附近,电流监测器测得在频率跳变附近的三次谐波电流分量比没有频率跳变处的大20dB以上。当R=200Ω时,不产生频率异常跳变,此时的三次谐波电流分量较基波分量低20dB以上。

图8 频率突变与负载电容的关系

图9 异常跳频实验电路

以上实验可得到下列结论,当变容管、晶体管和一对二极管所产生的三次谐波电流的频率3ƒ0远离ƒ3L时,频率3ƒ0上回路增益很小,因而振荡频率几乎不受3ƒ0三次谐波电流的影响。但3ƒ0当接近ƒ3L时,串联的晶体和负载电容就进入谐振状态,3ƒ0频率的回路增益就增大,而在回路中环流的三次泛音电流与被非线性元件把基波电流变换来的三次谐波电流就相互干扰,结果会使晶体的基波模和三次泛音模耦合。当这种耦合最紧密时,由CL变化引起的ƒ0的变化就成为ƒ3L/3的变化。

消除频率异常跳变的方法:

(1)适当加大反馈电阻R,即减小放大器的增益边界,使频率为ƒ3L/3的振荡不能形成,这就意味着消除频率异常跳变后,压控频偏变得很窄。故增加R不适用在压控晶振中。若压控晶振中使用带A.G.C的放大器作振荡级,则A.G.C电路可以减小流过晶体的电流。当晶体电流很小时,其三次和五次等高次泛音模不会激励起来,因而避免了高次泛音模的干扰,从而避免了基音模频率跳变现象。

图10 改进的晶体振荡电路

(2)在回路中增加两个陷波电路,使回路在3ƒ0处的增益将至零,可消除频率异常跳变。具体电路如图10所示。

5 压控晶振的结果与分析

频率微调后,在封装之前即可测试。首先在自制的专用夹具上测定VCXO其中心频率和压控频率范围,若不起振,则应细查是否晶片损伤并予以更换返工。最终测试采用微机检测,其测试原理图如图11所示。

图11 测试原理图

当测试夹具上放入一个VCXO时,产生一触发信号,输出给计算机,计算机则根据所编程序反馈一脉冲信号给测试夹具,测试夹具接收脉冲信号后,自动依次输出VCXO所需的控制端电压,此时计数器和示波器上显示VCXO的准确输出频率和波形,同时,计算机根据设置的程序进行计算,显示出VCXO的各项指标,最终判定合格或不合格。

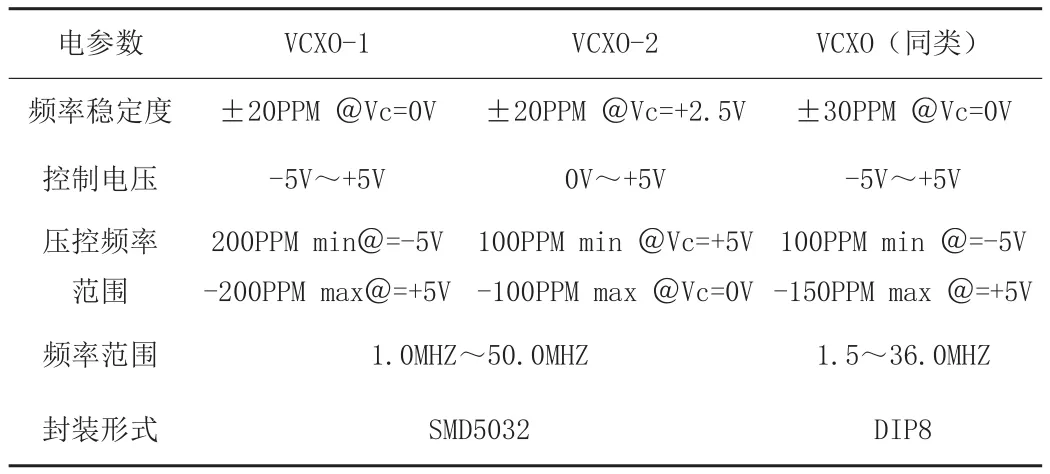

该产品与国内同类相关产品相比,频率稳定度、压控频率范围、频率范围等方面都得到了明显的提升,尤其在封装形式上体积显著减小,实现了该产品微小型的突破,相关产品对比如表1所示。

表1 技术参数及国内产品对比表

结束语:经过对压控晶振理论原理的深入研究,研制了一款具有高稳定性、高可靠性和宽范围压控频率范围的金属封装结构的SMD5032压控晶振,其频率稳定度达到±20PPM,绝大多数非线性优于2.5%,压控频率范围可达±100~±200PPM。通过变容二极管的选择以及电路的改进对非线性系数和频率异常突变进行了有效改善。压控晶振目前广泛应用于电子技术的各个领域中具有非常重要的实际价值。