基于FPGA的混沌神经网络同步实时实现

2021-06-22张建勋虞名海胡卫生义理林

张建勋,杨 钊,虞名海,胡卫生,义理林

(1.上海交通大学 区域光纤通信网与新型光通信系统国家重点实验室,上海 200240;2.中国人民解放军66389部队,郑州 451100)

0 引 言

信息技术的飞速发展在给人们的生活带来便利的同时,也给信息安全带来了严峻挑战。自20世纪以来,混沌现象[1]和混沌同步[2]相继被发现和提出,将混沌现象应用在保密通信中成为人们日渐关注的问题[3-7]。但在已提出的混沌保密光通信方案中,接收端都需要采用与发射端参数完全一致的激光器来产生同步的混沌载波,这种同步方式结构复杂,很难在实际中得到应用。2019年,上海交通大学使用光电光混沌的加密方式,通过神经网络建模的方法获得加密信号和混沌载波之间的函数关系,进而提出了在数字域上实现混沌同步解密的方案,实验采用10 GHz带宽的混沌信号,通过训练后的神经网络实现了对20和32 Gbit/s信号的解密[8],但只是进行了离线实验验证。到目前为止,还没有使用基于神经网络同步的方式进行实时混沌保密通信实验的报道。

本文使用电路混沌对基于神经网络的同步进行实时验证。基于现场可编程门阵列(Field Programmable Gate Array, FPGA)产生混沌信号对传输信号进行加密,在发射端分别获取混沌和加密信号,利用神经网络进行离线监督训练,获取网络结构参数后,基于数字信号处理(Digital Signal Processing, DSP)Builder工具箱搭建神经网络模型,并移植到FPGA中进行混沌同步,达到信号实时解密的目的。

1 实验设计

1.1 基于FPGA的混沌信号产生

连续混沌系统是由微分方程描述的非线性动力系统。本文通过洛伦兹方程生成连续混沌信号作为保密通信的载波。洛伦兹混沌系统的连续状态方程如下:

该常微分方程组是科学家洛伦兹在研究大气对流模型时所提炼的三维方程及由其表现的“蝴蝶效应”动力行为而得出的。式中:x、y和z为变量;t为时间;a、b和c为系统参数。当系统参数设置为a=10,b=28,c=8/3时,系统将处于混沌状态。

通过对洛伦兹状态方程进行等价变化,选择合适的模拟非线性电子器件,可以用模拟电路来产生洛伦兹混沌信号。但这种方法比较复杂,所需电子器件较多,增加了线路之间的干扰,并且更容易受到外界因素的影响,增加了混沌系统的不稳定性。相比于模拟电路,以FPGA为平台产生混沌信号更加简单直接,可移植性强,并且基于混沌系统的初值敏感性,可以随时改变系统初值,使混沌系统的运动轨迹发生巨大变化,增加了破译的难度,进而增强了保密通信系统的安全性。

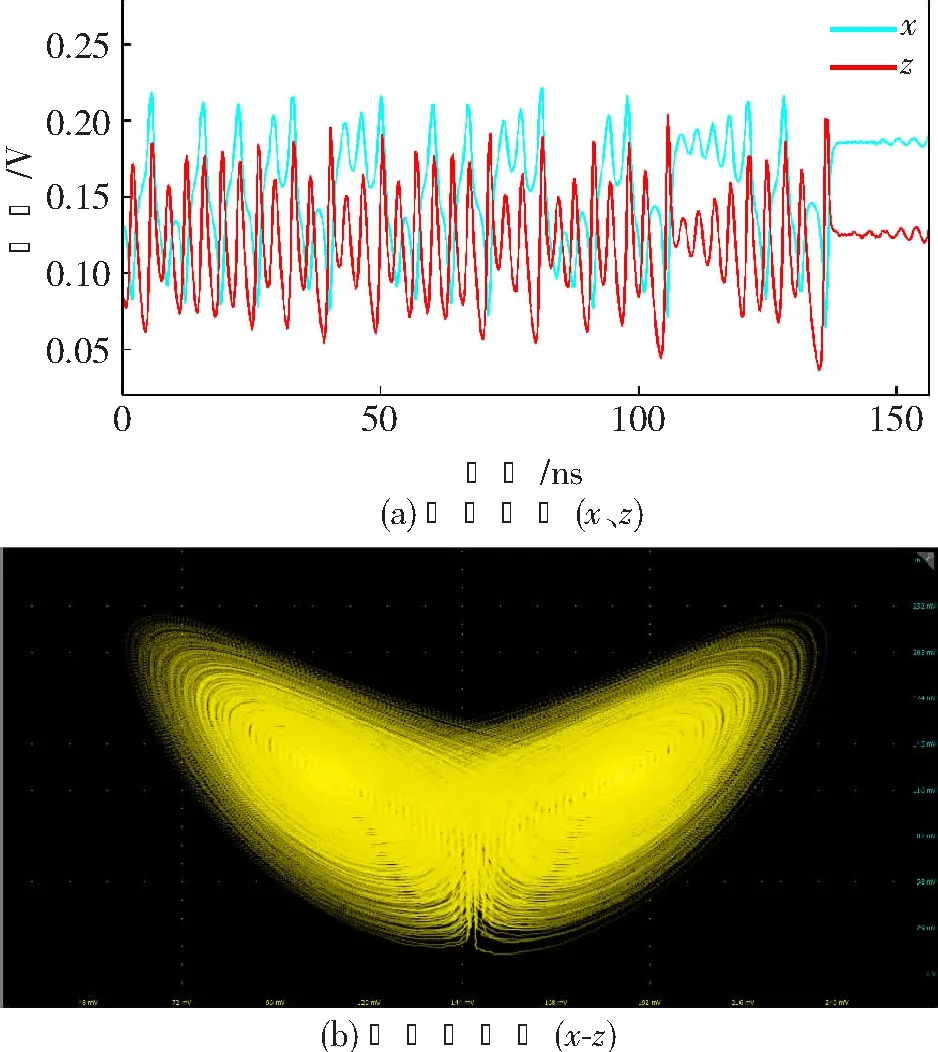

由于洛伦兹混沌系统是对连续状态的描述,而FPGA只能处理离散化的数字信号,所以使用FPGA产生洛伦兹混沌信号时必须把系统的状态方程离散化,这样得到的混沌系统的运动轨迹会接近真实的混沌运动轨迹[9]。在状态方程离散化以后,使用DSP Builder工具箱来进行混沌生成模型的硬件设计。DSP Builder是一个系统级和算法级设计工具,它架构于Matlab/Simulink软件之上,对FPGA进行方便、快捷和高效的DSP,具有很强的可视化,方便设计中功能的仿真与验证,极大简化了基于FPGA的DSP系统和算法的设计流程。根据离散化的状态方程,调用DSP Builder工具箱中的元件搭建混沌生成模型。功能仿真通过后,使用信号编译(Signal Complier)模块将混沌生成模型转换成.qip(Quartus IP)文件,在Quartus II中进行例化和编译,下载到FPGA进行硬件调试,最终产生混沌信号,混沌信号波形(变量x和z)和混沌吸引子(x-z)如图1所示。

图1 洛伦兹混沌信号和混沌吸引子

1.2 混沌加密和解密结构

本文使用洛伦兹混沌的变量z信号采取混沌掩盖的方式对信号进行加密。加密结构如图2所示,用任意波形发生器(Arbitrary Waveform Generator, AWG)产生一个10 Mbit/s的随机非归零码(Not Return to Zero, NRZ)信号,与FPGA经数模转换器(Digital to Analog Converter, DAC)产生的洛伦兹混沌信号进行耦合,生成混沌掩盖加密信号。

图2 混沌加密结构

本文使用的洛伦兹混沌信号带宽为100 MHz,混沌信号和传输信号的掩盖比例(幅度峰峰值之比)为8∶1,这样既可以使信号完全隐藏在混沌信号中,而且基本不改变混沌信号的原始结构,如图3所示。

图3 混沌加密信号

基于神经网络对非线性系统的强大拟合能力,用神经网络对洛伦兹状态方程进行建模。使用示波器(Tektronix MSO64)采集DAC输出的混沌信号作为神经网络的目标输出,耦合器输出的混沌加密信号作为神经网络的输入,加密信号速率为100 Mbit/s,示波器的采样率设置为312.5 MS/s,与模数转换器(Analog to Digital Converter,ADC)的单通道采样率保持一致。混沌信号和加密信号各采集1 250 000个数据点,并将前80%的数据作为训练集,后20%的数据作为测试集,使用全连接神经网络进行离线训练。神经网络解密结构如图4所示。只要神经网络同步出来的混沌波形与目标混沌波形相似度足够高,就能通过减法运算得到所需要解密的信号[10]。

图4 神经网络解密结构

本文使用的全连接神经网络由一个包含64个神经元的输入层、20个神经元的隐藏层以及1个神经元的输出层组成,使用ReLU作为神经网络的激活函数f(x)。训练迭代次数为100,学习率设置为0.001。

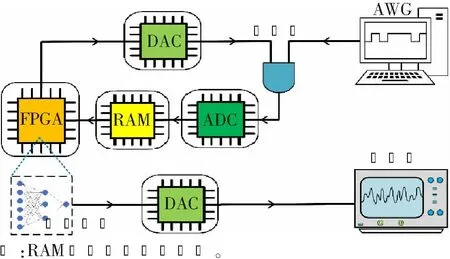

使用FPGA对信号进行解密时,将耦合器输出的混沌加密信号输入到ADC进行模数转换,转换后的数据使用第3代双倍速率同步动态随机存取内存(Double Date Rate 3 Synchronous Dynamic Random Access Memory, DDR3 SDRAM)进行存储,编写控制命令读取数据并在FPGA中进行神经网络运算,运算结果经DAC后输出。硬件加密和解密结构如图5所示。

图5 硬件加密和解密结构

2 实验验证及结果分析

2.1 神经网络离线训练

使用采集到的混沌信号和加密信号,通过全连接神经网络的训练,相似度可以达到98%以上,信号解密误码率为0。图6所示为基于神经网络同步的混沌波形和目标混沌波形相似度比较,其中,RC为目标混沌,YC为神经网络同步的混沌。

图6 目标混沌波形和基于神经网络同步的混沌波形及相似度比较

2.2 基于DSP Builder的功能验证

神经网络离线训练完成后,获取该网络结构的模型参数,主要包括隐藏层、输出层的权值和偏置等。使用DSP Builder工具箱进行全连接神经网络模型的搭建。

对于64-20-1的全连接神经网络来说,输入层64个神经元分别与隐藏层20个神经元相对应的权值进行乘法运算,隐藏层每个神经元对应的64个乘法结果进行累加运算,然后与对应偏置值相加,经过激活函数的非线性处理后,作为输出层的输入,与输出层神经元相对应的权值进行乘法运算,最后与偏置相加后输出。基于神经网络各层之间的串行特性,使用流水线结构处理的方法,即先进行输入层-隐藏层的运算,再进行隐藏层-输出层的运算,确保大量数据计算的准确性,同时节省了硬件资源。

根据全连接神经网络的结构和算法流程,调用DSP Builder工具箱中乘累加器、乘法器、加法器和多路复用器来实现神经元的输入和乘加运算,通过计数器模块来实现神经网络计算的全局控制,激活函数ReLU通过比较模块和常数0来实现,将权值以mat文件的形式存储于只读存储器(Read Only Memory,ROM)中,通过1个6 bit的计数器生成地址信号进行读取,权值、偏置和中间数据的存储、计算采取4Q20(即4个整数位、20个小数位)的定点小数格式,保证了计算的精度,同时也避免数据溢出。添加系统时钟为100 MHz,采取固定步长的方式对模型进行编译仿真,从而得出与神经网络离线训练相同效果的混沌波形。经过计算分析,解密信号的误码率为0,目标混沌波形和基于DSP Builder同步的混沌波形及相似度对比如图7所示。

图7 目标混沌波形和基于DSP Builder同步的混沌波形及相似度比较

2.3 基于FPGA的实时测试

功能仿真验证通过后,使用FPGA进行硬件调试。FPGA使用Altera公司Stratix V系列的5SGXEA7K2F40C2,配合1片5.0 GS/s的ADC(EV8AQ160)和两片2.5 GS/s的DAC(AD9739)。ADC采用单通道模式,采样率为312.5 MS/s,采样精度为8 bit。神经网络模块的时钟为100 MHz,使用2 Gbyte的DDR3 SDRAM(MT41J256M16)对数据进行存储,通过Verilog HDL代码采用状态机读写的方式编写DDR3 SDRAM的控制逻辑,配合使用先进先出(First-in First-out, FIFO)逻辑模块,保证数据存储前后速率和位数的匹配。从DDR3 SDRAM读取的混沌加密信号根据全局控制命令进行神经网络运算,同时,将读取的混沌加密信号经过延迟模块,与神经网络同步得到的混沌信号做减法运算,通过判决模块后,经过DAC输出得到解密信号,解密信号误码率为6.4×10-4。使用相关系数来评估解密信号与原始传输信号的相似性,定义为

图8 解密信号波形及与原始信号相关曲线

神经网络模块工作于100 MHz的时钟下,其功能主要通过乘加运算实现,对乘法器资源要求较高。FPGA内嵌256个DSP块,每个DSP 块可实现两个18 bit×18 bit的乘法和加法。由于本文采用流水线结构处理的方法,大大节约了资源的使用率。FPGA的主要资源使用情况如表1所示。

表1 FPGA资源使用情况

2.4 结果分析

从离线训练和DSP Builder仿真的结果看,神经网络对洛伦兹混沌具有良好的同步效果,对10 Mbit/s的NRZ信号解密能达到零误码,混沌同步相似度较高。对于基于FPGA的混沌实时同步与信号解密,虽然受限于ADC的采样精度,解密信号的误码率仍然在1×10-3以下,仍能达到较好的同步效果。因此,在采用混沌掩盖方式的保密通信中,可在接收端将提前训练好的神经网络同步模型集成到硬件中进行同步解密,不需要增加额外的同步信道,并且能够简化接收端的结构,降低信息被窃取破译的风险。

3 结束语

本文提出了利用FPGA生成混沌信号,在发射端对信号进行加密,在接收端基于FPGA实现神经网络算法来达到混沌同步,实现了10 Mbit/s信号的实时加密与解密,解密信号的误码率在1×10-3以下。但是,本文使用的混沌载波为电路产生的混沌信号,混沌带宽有限,难以加密高速率信号。相比于电路混沌来说,全光混沌具有更复杂的非线性动力学特性,带宽更宽,能够进行高速率信号的加密传输。随着更多乘法器资源FPGA的应用,基于FPGA可实现更大规模的神经网络应用,从而实现更高速率和更长距离的混沌加密实时传输。