基于SiP 技术的小型化红外前端采集微系统

2021-06-14赵亚南宋佳囡

方 珉,许 羽,赵亚南,吴 玮,宋佳囡

(上海航天控制技术研究所,上海 201109)

红外前端采集电路用于实现红外成像传感器的高精度、低噪声驱动、模拟信号采集调理、高速模数转换及信号预处理等功能,是各类红外信息处理系统的关键组成部分[1]。随着技术的进步,红外成像传感器不断朝着高帧频与高分辨率发展,由此需要前端采集系统处理的信息量越来越多,处理的速度越来越快,噪声越来越低。此外,为了得到更好的系统性能,其他部组件和执行机构也在不断挤压采集电路的空间,使得电路可利用的空间越来越小。目前红外前端采集电路已选用了大量小封装塑封贴片元器件来实现小型化设计,但即使如此,电路板上的器件也已非常密集,很容易与结构干涉并带来信号串扰等问题。由此可见,基于传统印制板与分立器件的设计模式在电路的进一步小型化上已遇到了瓶颈。

设计了一种基于SiP 系统级封装技术的小型化红外前端采集微系统[2],通过对原系统功能的合理划分,将多片芯片集成至3 个模块中,结合数模混合电路抗干扰及低噪声传感器驱动技术,实现红外前端采集电路的小型化、低噪声设计。

1 系统总体设计

1.1 SiP技术概述

SiP 技术将两个或多个大规模集成电路的裸芯片及其他微组件(包括芯片组件)统一集成在一个高密度互连基板中,并将具有不同功能的高密度微电子组件封装在同一外壳内。SiP 技术中融合了多层布线基板技术、多层布线互连技术、表面贴装技术、裸芯片制造等先进的技术,其优势集中体现在性能高、可靠性强、体积小、密度大等方面。它是制造高速电子系统,实现电子整机小型化和系统集成的有效途径[3]。

1.2 系统功能划分

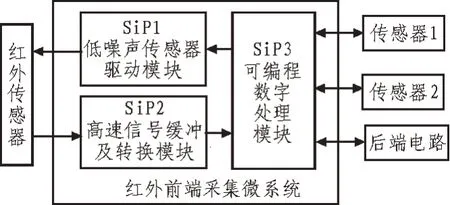

为了避免与红外信息处理系统中的红外成像传感器、执行机构等部组件发生干涉,原红外前端采集电路采用了软硬结合印制板技术,将不同功能器件分散布置在3 块硬板上,板间信号通过柔性板进行连接。该设计通过对电路功能的合理划分,将原先需要多片芯片实现的功能集成至3 个塑封模块:低噪声传感器驱动模块、高速信号缓冲及转换模块、可编程数字处理模块,并将其放置在一块印制板上,微系统总体架构如图1 所示。

图1 小型化红外前端采集微系统总体框图

2 各模块设计

2.1 低噪声传感器驱动模块

低噪声传感器驱动模块主要提供红外成像传感器正常工作所需的电源及低噪声偏置电压[4]。在红外信息处理系统中,红外成像传感器正常工作共需两类偏置电压,一类为可调偏压,用于调整传感器的最佳工作点,另一类则为固定偏压,为传感器提供工作电源、基准电压等[5]。

可调偏压由于不是标准电压值,且对电压调整精度要求较高,因此采用FPGA 输出可调偏置电压代码,由D/A 变换器数模变换后再经运算放大器缓冲输出的方式实现,其中D/A 转换器选用16 bit 分辨率、INL 为±12 LSB、SPI 接口且为电压输出的产品,以简化外围电路。该转换器内部参考电压Vref为2.5 V,根据计算公式:

可得,在给定数字量下,D/A 转换器电压最大变化量约为1 mV,可满足传感器对该路偏压不大于10 mV 的电压调整精度要求[6]。

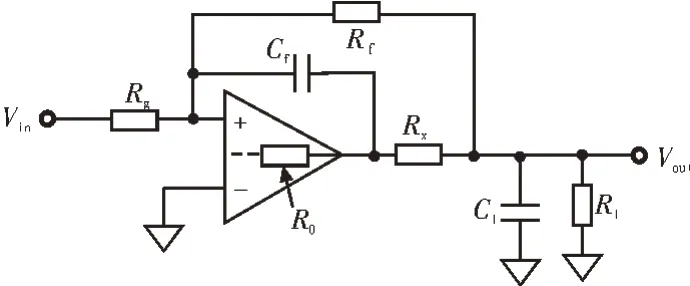

值得注意的是,由于红外成像传感器像元阵列上的每个探测元可简化为一个RC充放电电路[7],经计算该设计所需驱动的红外成像传感器总电容量已达μF 级,因此可以把它看成一个容性负载,当这个容性负载与运算放大器内部的输出电阻Ro相接时,在运放传递函数上将产生一个附加的极点从而导致运放电路变得不稳定。为了避免运算放大器在驱动容性负载时可能引起的振荡,将运放缓冲电路设计成如图2 所示的“双反馈”形式。该电路通过在运放反馈通道中增加电容Cf以抵消传感器电容Cl所造成的极点和零点。因此,整个电路的传递函数和相位响应与没有电容Cl时完全一样,确保了整个偏压电路的稳定[8]。

图2 “双反馈”运放缓冲电路原理图

固定偏压则由低噪声电压基准经电阻分压后产生。通过调整分压电阻分别输出多路探测器工作所需电源与基准电压。该设计采用电压基准外接运放的形式来实现传感器固定偏压的输出。运放缓冲电路同样选用“双反馈”形式以提高稳定性。该电路中所选电压基准输出电压为4.096 V,噪声为35 μV,所选运算放大器则具备最高150 mA的电流驱动能力,可满足红外成像传感器对固定偏压最大100 μV 噪声与不小于35 mA 电流驱动能力的要求。

2.2 高速信号缓冲及转换模块

红外成像传感器模拟信号由传感器输出后,需经过阻抗匹配、信号调理缓冲以及高速A/D 变换后才能传送至FPGA 进行进一步处理。阻抗匹配电路由单倍增益放大电路实现,运算放大器选择250 MHz带宽、轨至轨产品,匹配电阻Rd按传感器要求选择100 kΩ,使传感器信号不失真地进入下一级缓冲电路。由于红外成像传感器的信号输出范围为1~4 V,而高速A/D 变换器的输入范围为-1~+1 V,故不能直接将传感器信号引入A/D 变换器,还需设计基于运算放大器的调理缓冲电路[9]。

如图3 所示,该电路通过选取合适的反馈电阻Rf与Rg值来设置一定的放大倍数,需注意的是为了减小电阻热噪声对传感器信号的影响,Rf与Rg的值不宜选得过大,此处Rf选200 Ω、Rg选300 Ω,将输出信号范围由3 V 调整为2 V。通过在运放反相输入端接入2 V 参考电压Vref来滤除传感器输出信号中的直流分量,确保最终的输出信号正好在A/D 变换器可采集的有效范围内。此外,通过增加Cf与Ct组成两级低通滤波器将传感器信号带宽限制在16 MHz 左右,从而进一步降低传感器信号噪声。

图3 调理缓冲电路原理图

高速A/D 变换器则选择14 bit 分辨率、不小于125 Msps 变换率、LVDS 串行输出接口的产品,在满足整个系统对信噪比与实时性要求的同时,通过降低接口信号线的数量,进一步减小模块面积。

2.3 可编程数字处理模块

该模块以可编程处理器件FPGA 为核心,主要完成数字接口实现、时序逻辑控制及数据传输等功能。经前期评估,整个前端采集电路正常工作所需的逻辑资源约在3 000 个LE 左右。该设计所选用的FPGA 内部包括4 480 个LE,700 kb SRAM 资源,15 个DSP 单元,1 个PLL,16 个全局时钟网络,最大支持207 个I/O 端口,差分端口数量为100 个。此外还集成了FLASH 存储器与RS485 接口转换芯片,可直接与具备同类接口的传感器连接,以进一步简化外围电路[10]。

为了尽量减少对外引线数量,前端采集电路与后端电路间选用了FPGA 内部自带的异步串行接口作为互相间的通信接口,该接口可在程序中直接调用,对外只需要一根同轴电缆即可实现稳定、可靠的数据传输[11]。

3 PCB设计与测试

3.1 PCB设计

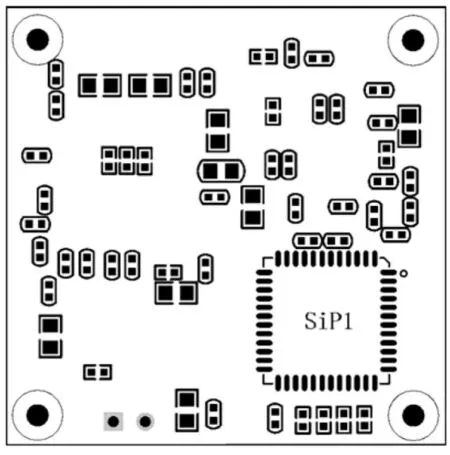

采用Altium Designer 软件进行PCB 设计,在采用SiP 微系统模块后,将原基于分立器件需3 块印制板才能实现的电路功能,整合至一块尺寸为35 mm×35 mm 的PCB 上,电路布局如图4 和图5 所示。设计过程中,将低噪声传感器驱动模块(SiP1)靠近红外成像传感器接口摆放;可编程数字处理模块(SiP3)靠近后级电路串行通信接口摆放;高速信号缓冲及转换模块(SiP2)则放置在中间,通过合理布局可有效地分隔模拟信号与数字信号,降低数字信号对模拟信号的干扰[12]。

图4 PCB正面布局图

图5 PCB背面布局图

尽管在PCB 布局上已尽可能进行了模数隔离,但由于PCB 面积限制,红外成像传感器正常工作时所需的时钟、使能等数字信号,在由可编程数字处理模块输出至传感器接口连接器时,不可避免地会经过模拟区域,由此会带来线间串扰的问题。因此在PCB 布线过程中采取了以下几个措施来减小串扰噪声[13]:

1)在数字时钟、使能信号上采用端接技术,以减小容性耦合和感性耦合产生的串扰耦合干扰;

2)在布线条件许可的情况下,尽量增大可能发生串扰耦合传输线之间的距离,减小并行传输走线的长度;

表5为刀具夹持长度不同时,换能器在20 kHz附近的振模态下,频率、位移节点位置和应力的变化情况,其中刀具长度均为40 mm。

3)在相邻信号传输线间插入一根地线,以有效减小容性串扰。

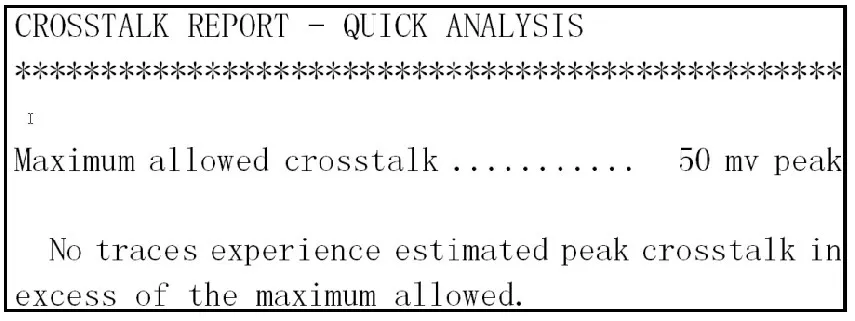

为了验证上述措施的有效性,将设计完的PCB文件导入Hyperlynx 软件进行串扰仿真,将红外成像传感器输出信号设为敏感线,设置串扰电气阈值为50 mV,仿真结果如图6 所示。可见,在设定的串扰阈值范围内,无网络会对该信号形成干扰[14]。

图6 串扰仿真结果图

3.2 系统测试

对微系统各主要功能模块开展相关测试,首先对低噪声偏压部分进行测试[15],其可调偏压纹波如图7 所示,纹波峰峰值在6.9 mV 左右,满足探测器不大于10 mV 的指标要求。

图7 可调偏压纹波测试结果

将各偏压值及纹波噪声与原分立电路测试结果进行对比,见表1 与表2。

表1 传感器偏压测试结果

表2 传感器偏压噪声测试结果

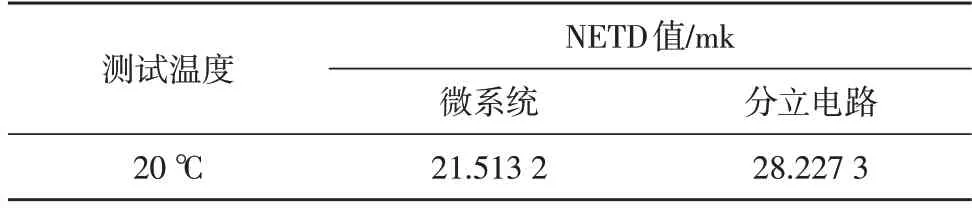

噪声等效温差(Noise-Equivalent Temperature Difference,NETD)指红外成像传感器能探测到的最小温差,可以用于预测极限温差下的观测距离,是衡量红外成像传感器性能的主要指标之一[16]。将微系统连接红外成像传感器后对该指标进行测试,并与原分立电路测试结果进行对比,见表3。

表3 红外成像传感器NETD测试结果

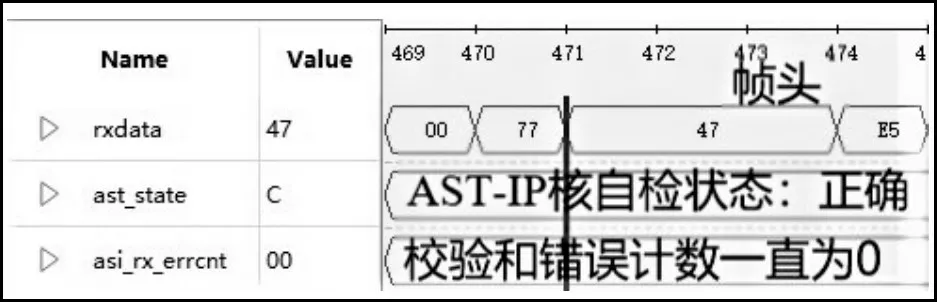

将微系统连接后端电路后对异步串行通信接口进行测试,两者间能正常通信,校验和错误计数一直为“00”,无误码,测试结果见图8。

图8 异步串行通信测试结果

从上述测试结果可见,基于SiP 技术的微系统主要技术指标与原分立电路保持一致,在偏压噪声及NETD 方面优于原分立电路。

4 结论

设计了一种小型化红外前端采集微系统,利用SiP 技术将多片芯片按功能划分并分别集成至3 个模块中,在不裁减功能的情况下,将原需3 块印制板实现的功能集成至单块印制板上,实现了采集电路的小型化设计,为系统其他部组件的安装腾出了空间。同时通过多芯片封装技术,摆脱了以往小型化电路对进口塑封器件的依赖,为后续实现元器件自主可控打下了基础。通过对比测试,应用SiP 技术的小型化红外前端采集微系统性能与原电路保持一致,在噪声等指标上优于原采集电路,后续可推广应用至其他对小型化有迫切需求的红外信息处理系统。