FPGA块存储器的多位翻转容错设计

2021-06-02

(1.中国科学院大学 计算机科学与技术学院,北京 1000492.中国科学院光电技术研究所,成都 610209 )

0 引言

为了满足不断增长的性能和功率需求,FPGA制造技术流程需不断演变,采用先进的工艺节点制造,这使得FPGA组件尺寸不断缩小形成高逻辑密度器件。在这么小的几何结构器件中,太空环境单个辐射粒子撞击器件所引发的单粒子翻转(single error upset,SEU)效应已不限于单比特翻转(single bit upset,SEU)事件,单粒子撞击甚至会导致存储器阵列的多个相邻位的翻转,即多比特翻转(multiple bit upset,MBU)事件[1]。器件物理尺寸的减小还会导致电源和阈值电压的比例下降[2],导致FPGA器件受太空辐射影响的概率不断增大,进一步导致FPGA存储单元发生SEU的概率增加。

FPGA的存储资源主要有配置存储器和用户设计中的存储单元组如:BRAM、DRAM、触发器等构成。BRAM作为FPGA的第二大内存,提供了大量的高容量存储单元用于存储用户设计状态,实现FPGA内部数据的随机存储。一旦BRAM发生翻转故障,会导致FPGA逻辑电路发生异常,严重时甚至会导致电路失效。因此本文主要针对BRAM进行抗SEU防护。

1 FPGA的MBU事件

FPGA缓解SEU的防护可从工艺、版图设计和系统设计等不同层面进行,但工艺和版图设计代价昂贵且设计周期较长,目前的抗辐射加固主要是在系统设计层面上进行。缓解SEU最常用的系统容错方案是采用具有单比特纠错和双比特检错(SEC-DED)的汉明码技术。但是,随着制造工艺节点的减小使得太空辐射环境中FPGA的MBU成为高发事件。在采用的 45 纳米技术中, MBU 事件占FPGA软错误的概率高达48.28%[1],而且对于更小的技术节点,该比率也相对变高[3]。传统的SEC-DED技术已无法满足FPGA存储器纠正多位错误的需求。MBU的发生主要有单粒子撞击造成的多位翻转 ( single event multiple upset,SEMU) 和一位翻转的积累这两种形式,后者的消除通过缩短系统的整个刷新时间即可实现,因此,目前讨论的多比特翻转多指SEMU。它是由单个高能粒子以某种入射角击中存储器的敏感区造成相邻存储单元的多个瞬时错误[4-5],也称之为多比特突发错误( burst error,BE)。

为了能够纠正MBU软错误,国内外学者提出了多种设计方案,文献[6]采用2-D海明码校正配置存储器的多位翻转,可用性超过99.9999999%。文献[2]采用InD 奇偶校验编码来检测配置存储器的MBU,利用纠删码技术重建码字实现纠错,能检测100%MBU,且资源占用率仅为3.3%。文献[7]将多个存储器交错排列成阵列,把单个码字分散到多个存储器,从而使单个存储器上产生的逻辑相邻的多位翻转错误分散到不同码字,使用传统的 SEC-DED 方法即可进行纠错,但是这样需要大量的硬件资源。文献[8]基于信息和硬件冗余的组合,提出一种奇偶校验字节和复制(Parity per Byte and Duplication,PBU)的EDAC技术,将每个存储字分成字节段,奇偶校验位与每个段相关联实现多位纠错,使用的存储块仅占3.85%。在国内,文献[9]提出一种改进型的(14,8)循环码实现了存储器MBU的纠错检错,代码易于实现,且实时性高。文献[10]提出一种位交错技术,将它与汉明码结合,可实现存储器MBU的99.82%纠错。文献[11]通过将两个能纠正一位随机错误和二位突发错误的(13,8)系统码结合,交织度为2的(26,16)交织码,实现了存储器的多位翻转纠错。诸如其它纠错能力强的错误检查和纠正(error correcting code,ECC)码,比如BCH( Bose Chaudhuri Hocquenghem)码、RS( Reed-Solomon) 码、矩阵码等,具有速度和时滞的缺点。

本文使用RM(Reed-Muller)码来进行多位翻转纠错,它是最老的错误纠正线性码之一[12],所实现的RM(2,5)码构造简单,结构特性丰富,占用资源少,可实现少于4位的翻转纠错,而且具有低时滞和高性能的特点。通过对编码系统进行了可靠性分析,利用故障注入进行了仿真实现和实物实验,从理论分析和硬件实验验证证明该编码可提高FPGA BRAM的可靠性。

2 RM码的原理

RM编码与其他纠错检错码一样,均需要经过编码和译码两个过程。

2.1 RM(2,5)编码

对于任意整数m和r,0 ≤r≤m存在一个二进制码长为2m的r阶 RM 码,记为 RM(r,m),其主要参数由三部分[13]:

码长:n=2m

(1)

(2)

最小码距:dmin=2m-r

(3)

t=(dmin-1)/2=3[13]

设信息码为m=(m15,m14,…,m0),生成矩阵为G,则R(2,5)码的编码生成的编码字C为:

C=m×G

(4)

RM(2,5)码共有5个变量:X1、X2、X3、X4、X5,它可以纠正大多数的三位随机翻转错误,其生成矩阵定义为G=(1,G1,G2)[14]。其中:

G1=(X1,X2,X3,X4,X5,)T

G2=(X1X2,X1X3,X1X4,X1X5,X2X3,X2X4,

X2X5,X3X4,X3X5,X4X5)

2.2 RM(2,5)译码

RM(r, m)为正交结构,因此译码通常采用大数逻辑译码(majority logic decoder,MLD),整个译码过程由3个阶段构成[15]。

第一阶段先译码出10个信息位(m9,…,m0),而且每个信息位都由8位校验和来确定,以m9为例:

(5)

其中:C′为译码器接所收到的编码字,通过对8位校验和进行多数表决决定该译码信息位是0还是1,即:分别比较0和1的个数,若0的个数多,则该信息位为0,否则为1;若0和1的个数相等,则表示为发生4位错误,为未知信息位,无法进行正确译码。

第二阶段的译码需要生成16位中间码字C″,由公式(6)计算得到,该中间字的值跟第一阶段译码的信息位相关。该阶段译码出5个信息位(m14,…,m10),每个信息由16个校验和进行多数表决确实,式(7)给出m14的16位校验和计算公式。

C″=C′-[m9…m0]G2

(6)

(7)

第三阶段译码出最后一位信息位m15,该信息位的译码需要生成32位中间码字C‴,由公式(8)计算得到。该阶段无需生成校验和,可直接对C‴进行多数表决得到m15。同时C‴也指示了BRAM数据的具体翻转位置,若无翻转故障发生,C‴的所有位全为‘0’或者‘1’,发生翻转时,若1的个数大于0的个数,则不为‘1’的那几位所在的位置即为数据翻转位;相反,若0的个数多,则不为‘0’的那几位所在位置即为数据翻转位。

C‴=C″[m14…m10]G1

(8)

至此,经过3个阶段的译码,译码器将接收到的32位编码字译码成16位信息位,并完成纠错检错。RM(2,5)码译码思想总结为:

(1)在RM(2,5)编码矩阵的每行找到2m-r=8个特征矢量,将其与接收到的码字C进行点乘得到8位校验和。

(2) 将每个译码位所得的校验和0和1的个数进行判断,若0的个数多,则该译码位为0,否则为1。

(3) 将(2)中得到的译码位与生成矩阵G2相乘,用接收到的码字C′减去相乘结果得到新的码字C″,在C″找到新的特征矢量求出16位校验和,重复(2)。

(4) 将(2)中得到的译码位与G1相乘,用C″减去相乘结果得到新的码字C‴,重复(2)。

(5) 将(2)(3)(4)中得到的所有译码信息位进行整合输出。

3 BRAM防护系统实现

Xilinx Virtex-5 FPGA的BRAM其内嵌有可实现SEC-DED的汉明码,用于缓解SEU的SBU效应,一旦发生MBU,内嵌的汉明码防护无法起到防护作用。常用的解决方案有:对BRAM进行TMR,屏蔽单个存储器的SEU事件;或者为BRAM提供具有纠错能力更强的ECC防护,在存储数据前进行编码防护,读取数据时进行译码修复。

3.1 故障注入

FPGA常用的可靠性评估方法主要为辐射实验和故障注入。辐射实验使用粒子加速器提供的各种粒子来源以模拟太空辐射环境,通过对目标器件进行照射实现。该方法可以得到较为真实的实验数据,但是目前国内能提供实验条件的设备不多,而且实现操作复杂、器件价格昂贵并且实验周期过长。

故障注入技术通过对待测电路模块进行定点或者随机的故障注入,通过观察分析模块电路的输出结果,可得到被测模块电路的可靠性评估结果。该技术可以弥补辐射实验的不足,且成本低、操作简便,已成为FPGA评估单粒子效应的一种重要方法。本文通过对BRAM存储的数据进行随机故障注入,进行0/1翻转,验证RM码防护时BRAM的可靠性。

3.2 BRAM的TMR防护

TMR是一种易于实现的静态冗余防护方法,将电路模块进行三备份,最终通过表决器进行3取2的表决输出,达到屏蔽单个电路模块失效的故障[16]。由于在同一时刻,3个模块均发生单粒子翻转事件的概率较低,且电路实现过程相对简单,被广泛应用于缓解SEU。因此,对BRAM进行三模冗余可提高存储器的可靠性。

尽管TMR易于实现,有效缓解SEU,且提高BRAM的可靠性,但其也存在以下缺陷[17]:

1)只能对错误进行屏蔽不能进行纠错。单个模块发生故障后,只能将其屏蔽,由于不具备纠错功能,且翻转错误的累积,最终会导致TMR防护失效,甚至导致系统崩溃。

2)尽管多个模块同时发生SEU的概率较低,但仍有可能发生,对系统可靠性来说是一个较大的威胁。

3)BRAM的TMR防护导致硬件资源开销增大,其资源利用率在大型设计中较低,且布线资源会增加系统的延迟。

4)表决器本身不具备抗辐射的能力,也可能发生SEU事件,导致表决出错。

因此,单纯的对BRAM进行TMR防护,在一定程度生可有效缓解SEU,提高系统的可靠性,但随着时间的推移,未及时修复的故障会积累,TMR的可靠性也会下降。

3.3 BRAM的RM(2,5)码防护

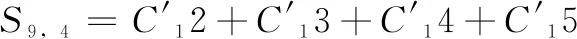

使用纠错能力更强的ECC码进行防护,可节省硬件资源开销,提高资源的利用率。RM(2,5)码对BRAM的防护原理如图1所示,数据处理单元控制BRAM的读写以及故障注入,RM(2,5)模块实现数据的编译码故障注入模块实现故障模拟。

数据处理单元发出写操作指令时,16位原始数据通过encin端口送入编码器,编码器进行编码后将32位编码字由encout端口写入BRAM;当数据处理单元发出读操作指令时,BRAM中的32位数据先从decin端口输入到译码器进行解码,如果块存储器中的数据发生翻转故障,解码器能够对翻转的数据位进行纠正。故障注入模块用来进行故障注入测试,根据处理器单元提供的注入地址从BRAM中读取相应的字对其进行0/1翻转,并将翻转后的数据重写回BRAM,模拟BRAM发生翻转故障的状态。error指示故障状态,error输出“00”表示无故障发生,“01”表示检测到一位、两位或者3位翻转错误,并进行了修复,“10”表示检测到四位翻转错误,无法进行修复, “11”表示检测到无效位错误。

图1 BRAM的防护原理

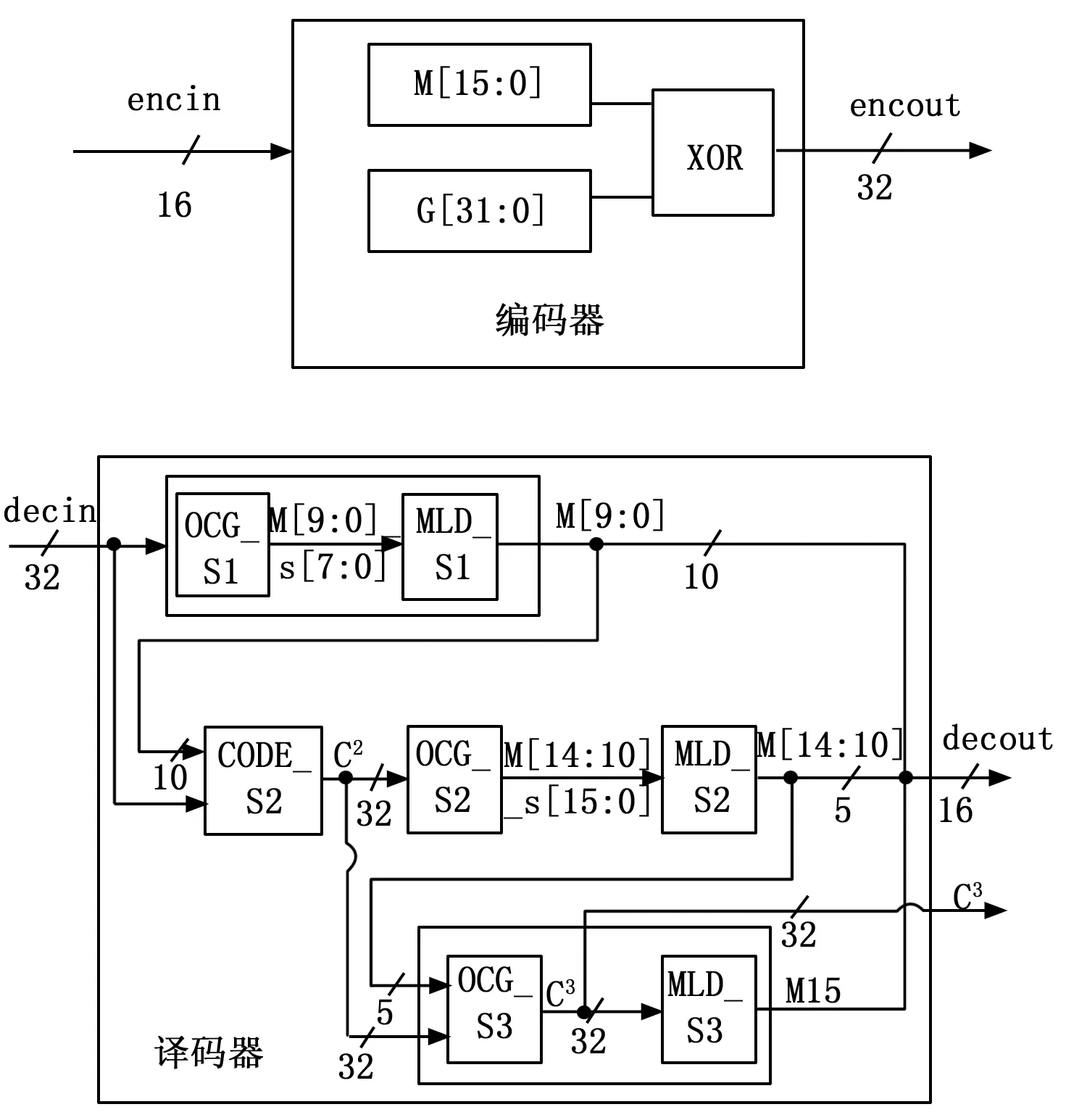

RM(2,5)编译码原理图如图2所示。存入数据时,16位原始信息码M(15:0)从encin端口进入编码器与32位生成矩阵G进行异或运算,得到的32位编码字存入BRAM中。读取数据时,从BRAM读取的32位译码数据从decin端口进入译码器,第一阶段译码出M(9:0),第二阶段译码出M(14:10),第三阶段译码出M15,最后从decout端口输出16位译码字,译码过程中同时修复存储器中的最多3位翻转错误,同时指示了错误发生的位置,以及错误发生的位数,译码结果输出到处理器。

图2 RM(2,5)码编译原理图

3.4 编码系统的三模冗余设计

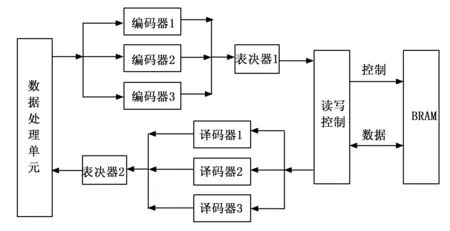

由RM(2,5)码组成的EDAC电路,并不具备抗辐射的能力,在太空辐照环境中,编译码电路也可能发生SEU事件,导致在编码和译码过程中出现翻转故障,无论是编码数据还是译码数据均会出现错误。因此通过将TMR与EDAC相结合,屏蔽单个编译码电路模块的故障,可有效避免EDAC电路的SEU事件,提高系统的可靠性。其原理框图如图3所示,将编码器和译码器分别进行三备份,数据同时进入3个模块,通过表决器进行3取2表决输出,提高了EDAC的可靠性。

图3 EDAC的TMR框图

4 可靠性与实验验证

通过理论分析对比不同条件下BRAM的可靠性以及RM(2,5)防护系统的资源利用率,最后通过仿真和实验验证,证明RM(2,5)码可实现小于4位的翻转修复。

4.1 RM(2,5)码可靠性分析

FPGA 块存储器单元未进行容错设计时其可靠性基本服从泊松分布[18],即假设每个BRAM单元发生SEU的概率为,在时间t内未发生SEU的概率为:

P(t)=e-λt

(9)

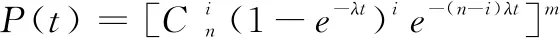

假设一个存储大小为m的BRAM其输入输出位宽为n,则它在时间t内发生i位翻转的概率为:

(10)

其中:i=0,1,2,3。RM(2,5)码能纠正单个码字中的3位翻转错误,因此,在时间t内BRAM的可靠性为:

(11)

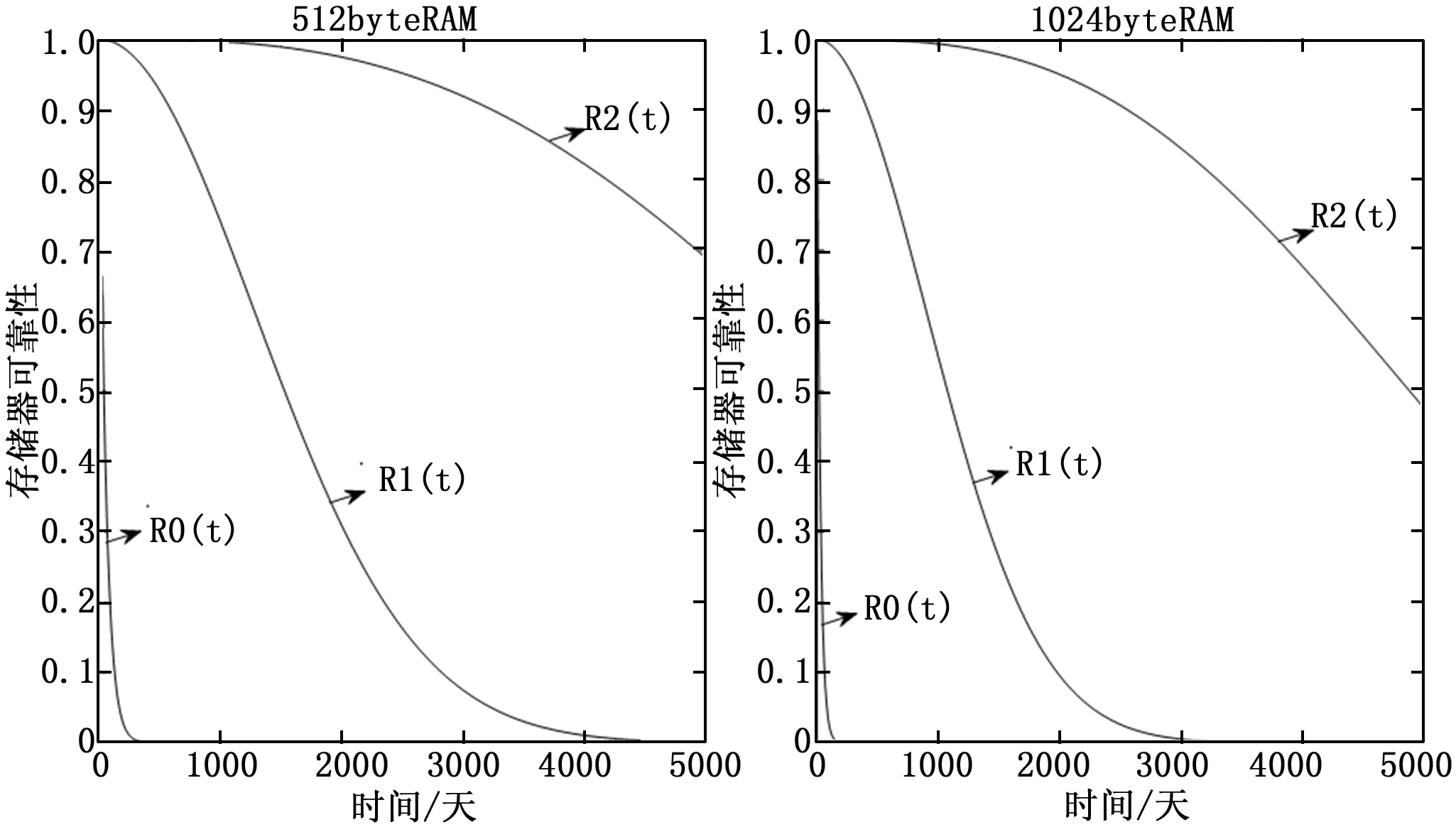

其中:i=0,1,2,3。在NASA提供的试验用粒子束条件下测得每个BRAM单元发生单粒子翻转的概率λ=1.1×10-6b/d[19]。图4是存储器大小分别为m=512 byte和m=1 024 byte下,在无防护、(12,8)汉明码防护和RM(2,5)码防护3种条件下由MATLAB计算得到的可靠性对比。其中R0(t)是无防护时的可靠性曲线,R1(t) 是(12,8)汉明码防护下的可靠性曲线,R2(t)是RM(2,5)码防护下的可靠性曲线。由图可见,在相同存储器大小下,RM(2,5)码的可靠性明显更优;在相同的防护条件下,容量小的存储器具有更高的可靠性。

图4 可靠性对比

4.2 资源分析

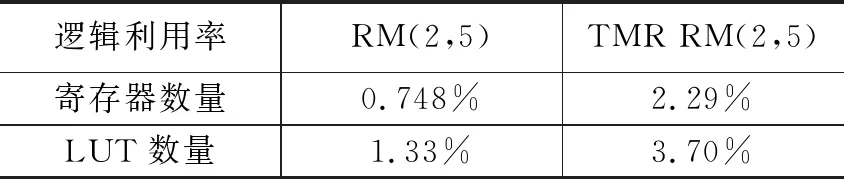

本文设计的RM(2,5)码防护系统利用Xilinx ISE14.7 设计工具在Virtex5 FPGA(xc5vfx70t) 上用VHDL实现,工作时钟频率为50 MHz。译码器和编码器主要是采用组合逻辑方式实现,整个编码系统的延迟由所占用的异或逻辑数量决定,编译综合后得到编码器模块LUT利用率约为0.107%,译码器模块LUT利用率约为1.12%,实现后整个编码模块的延迟为4.456 ns。RM(2,5)编译码模块三模冗余后,其硬件资源约为原始的三倍左右,如表1所示。

表1 RM编译码模块资源 %

4.3 硬件实验平台验证

实验前对该防护系统进行了连续注入故障的仿真测试,分别对存储的数据进行1位、2位以及3位的翻转。仿真结果表明可纠正不少于3位的翻转故障。仿真结果如图5所示。故障注入模块inf_error(2:0)端口对BRAM进行3位随机翻转,可以看到经过译码器修复后,error端口输出1,3位翻转错误被修复。

图5 仿真结果

经过仿真验证后,初步验证了该防护可修复不少于3位的翻转,进一步利用FPGA内部ICAP接口将配置RAM的配置帧内容回读写入BRAM作为原始存储数据。Virtex-5每个配置帧大小为41×32位,所设计的RM(2,5)编码系统其编码输入宽度为16位,通过将其级联实现32位的输入。本实验采用单端口的BRAM,存储宽度为64位,深度为41。使用Xilinx ISE14.7开发工具套件提供的ChipScopeTMPro工具抓取读取BRAM数据时的信号波形图,观察其存入BRAM的数据、故障注入后的数据以及纠错后的数据,实验结果与仿真结果相同。

图6(a)为BRAM写入数据的波形图,当ICAP回读计数器rb_cmd_cnt计数到71时,BRAM地址addra 从0加到1开始写入数据,原始数据首先从encin端口进入编码器进行编码,编码字落后1个时钟由dina端口存入BRAM中。

图6(b)显示了故障注入的过程。翻转信号start_flip_bit在时钟上升沿处拉高,表示开始从BRAM 的douta端口读取地址07,对位地址为25~27的3 位数据进行翻转,图中可以看到相应的位25~27由“0”变为“E”,翻转结束后通过dina端口将数据写回BRAM中,flip_start_done拉高表示一轮故障注入结束 。

图6(c)是数据处理单元从BRAM读取数据并实现三位纠错的过程,当ICAP写计数器wf_cmd_cnt计数到21时,BRAM的douta端口开始输出数据,先进入译码器进行译码,当wf_cmd_cnt计数为37时,可以看到,译码器decout端口输出的数据为正常数据,翻转的三位被修复。

图6 实验分析

经过仿真验证以及实物验证,均证明RM(2,5)码可修复BRAM中发生的不少于三位的翻转错误,有效提高FPGA块存储器的可靠性。

5 结束语

辐射诱发的MBU是FPGA的一个严重的可靠性问题,器件晶体管的减少、集成度的提高,使得FPGA的MBU概率变高。BRAM作为FPGA的第二大内存,一旦发生MBU,其设置的SEC-DED防护将会失效,造成所存储的用户数据出现错误,从而引发电路逻辑故障。

本文利用RM(2,5)码对FPGA的BRAM进行了EDAC防护,理论分析了防护系统的可靠性,并且通过仿真和实物测试实验,结果表明该方法可实现对存储器不少于3位翻转故障的修复,验证了RM(2,5)码组成的防护系统的有效性和可靠性。将TMR与EDAC模块相结合,提高了EDAC模块的可靠性,相比较传统的汉明码技术,具有更好的防护效果,该防护系统可灵活应用于寄存器和存储器的防护中。下一步,将继续研究FPGA配置存储器配置帧的MBU修复,将用RM(2,5)防护的BRAM的来存取配置帧的配置数据,保证在整个配置帧的重配置中配置数据的可靠性。