永磁直驱风电机组硬件在环实时仿真方法分析

2021-05-29王立强

牟 迪,曹 斌,王立强

(1.国电和风风电开发有限公司,沈阳 110000;2.内蒙古电力科学研究院,呼和浩特 010020;3.内蒙古自治区电力系统智能化电网仿真企业重点实验室,呼和浩特 010020)

0 引言

随着新能源行业的迅猛发展,新能源装机及发电量占比不断增加,与此同时,新能源并网带来的问题也日益增多,其中,风电机组在并网运行中存在的暂态稳定、次同步振荡[1-3]等问题,给电网的安全带来新的挑战。

目前,对于风电机组的并网性能检测主要通过现场测试的方式进行,这种检测手段周期长、费用高且对环境有一定的要求,同时,对于控制器厂家而言,验证控制策略只能通过离线仿真的方式,仿真时间相对较长,且对于实际控制器的性能检测没有有效途径。RT-LAB硬件在环实时仿真平台的出现为风电机组控制策略的验证和特性分析提供了解决方案,借助RT-LAB将控制器接入数字电网中,形成控制器硬件在环仿真结构,该平台具有强大的计算处理能力,能够实现控制策略的实时仿真与验证。目前RT-LAB平台已广泛用于新能源并网仿真特性研究中。文献[4-7]利用RT-LAB搭建永磁直驱风电机组的硬件在环仿真模型,文献[8]搭建了鼠笼型风电变流器的仿真模型。上述文献均侧重于仿真的实现,未对仿真原理和结果进行深入研究。文献[9-10]应用平台开展了直驱风电机组次同步振荡的仿真分析与研究,但在研究过程中对仿真模型进行了简化,并没有对平台的仿真过程进行研究和讨论。文献[11]应用该平台介绍了风电机组阻抗测量方法,提出仿真步长、接口延时、开关模型参数对风机阻抗的影响,但对于不同仿真器间的建模并未进行对比研究,对接口延时的研究不够深入。

本文以永磁直驱风电机组为研究对象,基于RT-LAB仿真平台建立风电机组硬件在环实时仿真模型,并开展相应的研究工作,为风电机组的实时仿真提供参考和借鉴。

1 RT-LAB硬件在环实时仿真平台

RT-LAB硬件在环实时仿真平台是基于Simu⁃link平台的一套实时仿真系统,能够进行新能源控制器接入的硬件在环仿真。仿真平台由上位机和下位机组成,上位机为普通计算机,用于建立数字模型;下位机为仿真器,用于仿真计算和与控制器的数据交互。仿真过程为:用户在上位机的Simu⁃link软件中按照模型定义规则建立仿真模型,编译生成C代码,通过以太网下载到仿真器中运行,仿真器与控制器通过I/O板卡进行数据的传输和交互,同时仿真器将用户监测信息传输至上位机显示[12]。

2 CPU与FPGA仿真模型

RT-LAB仿真器包含中央处理器(Central Pro⁃cessing Unit,CPU)仿真器和现场可编程门阵列(Field-Programmable Gate Array,FPGA)仿真器,其中,CPU仿真器(OP5600)通过软件形式进行算法执行和模型计算,仿真步长由模型的复杂程度而定,一般为5~100μs。对于新能源控制器,当开关频率较大时,CPU仿真往往无法满足要求。FPGA仿真器(OP5607)采用硬件语言描述及流水线结构[4],仿真器内置eHS解算器,仿真步长可达到ns级;同时,FPGA仿真器能够通过底层文件直接管理I/O接口,无需返回模型经数据传输模块输出,从而降低了接口延时,提升了仿真的准确度。但是OP5607仿真器无法独立进行仿真计算,需借助CPU仿真器进行联合仿真,对于开关频率小的仿真项目,占用了不必要的仿真资源。本文选取开关频率为3 kHz的直驱风机控制器,CPU仿真器的仿真步长能够满足仿真要求,因此,分别进行CPU和CPU+FPGA的仿真建模。

2.1 CPU仿真模型

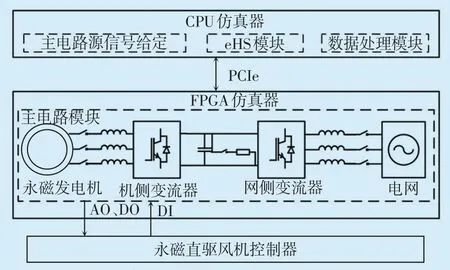

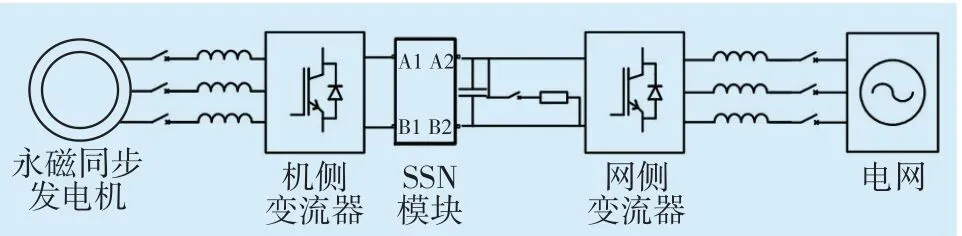

CPU仿真模型是指仅通过CPU仿真器建立的风电机组模型,模型的主电路、信号接口模块、数据处理模块均在CPU仿真器中运行,如图1所示。其中,信号接口模块由数字、模拟板卡模块及信号调理模块等组成,接收从风机控制器传输的数字量输入信号(DI),驱动主电路的开关器件,同时从主电路采集模拟量输出信号(AO)、数字量反馈信号(DO)传输至控制器,信号如表1所示。信号调理模块对输入/输出信号进行增益和限幅。数据处理模块是对采集的电气量进行处理,并传输至显示子系统中,用于监视和查看仿真结果。

2.2 CPU+FPGA仿真模型

CPU+FPGA仿真模型采用CPU仿真器与FPGA仿真器联合仿真的方式,结构如图2所示。其主电路模型在FPGA仿真器中运行,与控制器的接口通过FPGA底层程序直接管理。主电路中源信号的给定模块、eHS模块和数据处理模块在CPU仿真器中运行,源信号的给定模块用于主电路模型中电网和等效风电机组的信号输入,eHS模块为CPU+FPGA仿真的管理模块,包含仿真步长、输入/输出接口对应关系、主电路模型关联等设置。仿真器之间通过PCIe同步线进行数据交互,通常FPGA仿真器的仿真步长为ns级,CPU仿真器的仿真步长为μs级,通过联合仿真的方式实现小步长的精确仿真。

表1 仿真器与控制器间的交互数据

图2 永磁直驱风电机组CPU+FPGA仿真模型

3 仿真模型对比分析

针对两种不同方式建立的直驱风电机组实时仿真模型,从解算算法、仿真步长和产生的接口延时等方面进行多角度对比分析。

3.1 解算算法分析

传统CPU仿真采用节点分析法进行电路求解,当开关动作时,网络的拓扑结构随之变化,从而重新构建节点矩阵和预计算,需占用大量的内存空间和计算量。由于实时仿真的要求,CPU模型对开关数量和仿真规模存在一定限制,如CPU仿真模型超过单一计算核心的计算能力,无法进行实时仿真,可引入状态空间节点算法(State-Space Nodal,SSN)对电路拓扑进行划分处理,以提高仿真计算效率。

SSN算法将电路系统划分为两个或多个子系统,每个子系统为一个独立的状态空间,通过状态空间法进行计算,子系统间使用节点算法求解节点网络方程。通过SSN划分后,降低了子系统的开关数量,加速并完成仿真计算[13-15]。

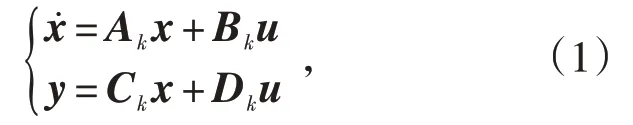

任意给定的子系统可以表示为:

对式(1)进行离散化运算,在t+Δt可得:

式中:yn t+Δt表示t+Δt时刻电压值;ykhis为历史电压值;Wk n为系统阻抗矩阵历史电压值;un t+Δt表示外部注入子系统的电流,形成戴维南等效电路。最后与子系统间列写的节点电压表达式联合求解,完成整个电路系统的计算[16]。对于含有k个开关器件的电路系统而言,仿真器需要对每种开关状态进行预计算并存储得到的系统矩阵,k对应的存储取值为2k个;假设利用SSN算法将系统均分为两部分,其对应取值将缩减为2×2k/2,并分配在两个计算核中并行计算,其计算量和存储量大大降低。

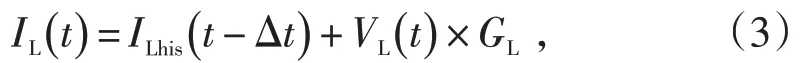

CPU+FPGA仿真采用内置的eHS解算器,采取小步长仿真且应用离散化的普约维奇(Pejovic)等效方法,以避免矩阵因子化计算及大量求逆矩阵带来的存储和计算压力[4]。在仿真过程中,Pejovic算法是将开关的导通状态等效为电感,关断等效为电容,通过离散化进一步等效为电流源与电阻的并联,因此有:

式中:Δt为仿真步长;ΔILhis(t-Δt)为电流源历史值;GL为等效导纳,即开关导通等效为电流源历史值与导纳GL的电阻并联。

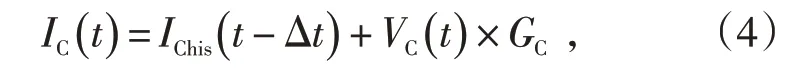

同理,开关关断时有:

即开关关断等效为电流源历史值与导纳GC的电阻并联。

通过上述等效,避免了由于开关器件动作导致矩阵重新构建,相比于CPU仿真,减少了计算时间和存储资源占用,使得仿真步长更小,计算更精细。

3.2 仿真步长对比分析

基于3.1节的分析,对两种仿真模型分别进行20%Un(Un为额定电压)低电压过渡仿真测试,并开展不同仿真步长的对比分析。模型均给定电动机转速为16 r/min,风机有功功率输出为1(p.u.),无功功率输出为0。系统稳定后使得电网电压降低至0.2(p.u.),持续时间0.625 s。

3.2.1 CPU模型

RT-LAB软件中集成了SSN解耦模块,在直流母线处对模型进行分割(见图3),分割后模型能够满足实时仿真计算的要求。设定仿真步长为20μs。图4为CPU模型20μs仿真步长测试曲线,可以看出,风机正常并网持续一段时间后发生电压跌落;风电机组在正常及故障阶段电流输出波形均畸变严重。

图3 含SSN的主电路模型

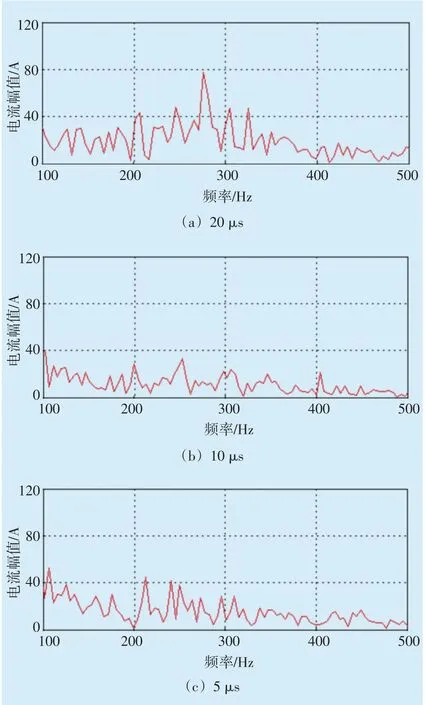

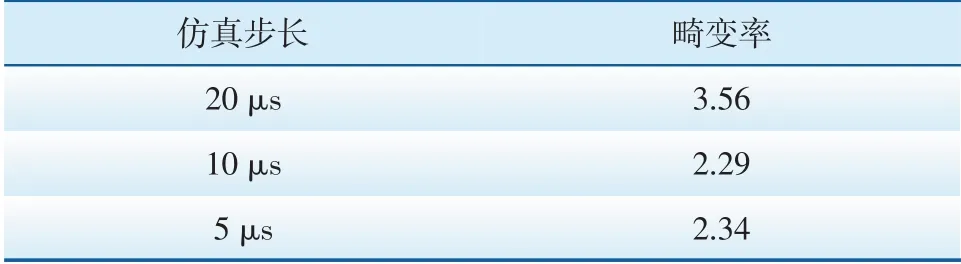

该模型虽然能够完成风机控制器的硬件在环仿真,但仿真波形的畸变严重,为提高仿真计算准确度,将模型的仿真步长进一步降低。RT-LAB平台集成了RT-Events模块库,其中包含带有时间戳信息的换流桥(Time Stamped Bridge,TSB)[17],TSB可通过插值模拟采样点间脉冲的跳变[18]提高仿真精度[19-20];同时,将普通换流桥更换为TSB后,可降低模型的规模,进一步精细仿真步长。引入TSB后,将仿真步长分别设置为10μs和5μs。由于风电机组直接连接理想电压源,电压曲线均为理想波形,因此不再进行对比。电流曲线如图5所示。由图5可见,仿真步长减小后,模型能够进行正常并网和故障暂态响应的仿真。根据3种情形做出对应的电流频谱图和电流谐波总畸变率,如图6和表2所示。相比于20μs步长仿真波形,5μs与10μs的仿真波形差异不大,畸变率相近。

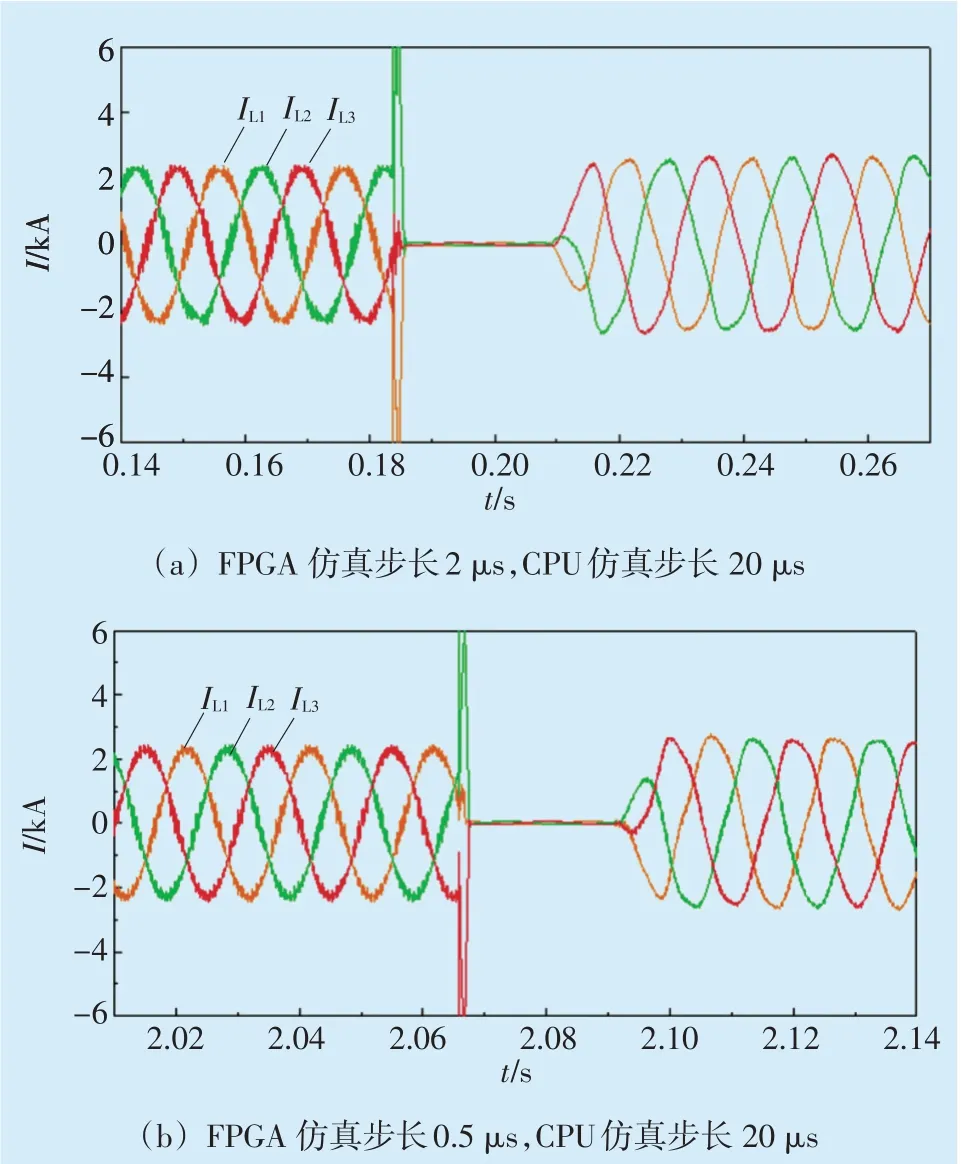

3.2.2 CPU+FPGA模型

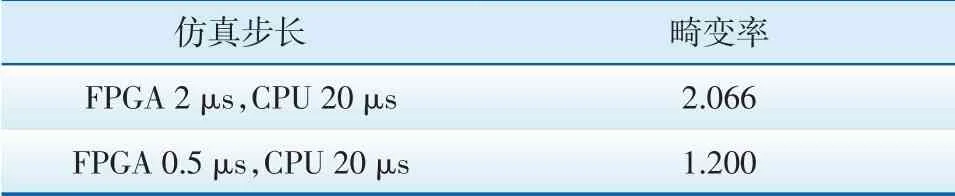

CPU+FPGA仿真器可将主电路模型的仿真步长进一步降低至ns级,开展与CPU仿真的对比研究。在FPGA仿真器中运行主电路模型,仿真步长分别设定为2μs和0.5μs,CPU仿真器进行电源及数据显示等模块的计算,仿真步长为20μs,电流仿真曲线如图7所示。由图5—图7及表2、表3可见,相比于CPU仿真,CPU+FPGA仿真的电流波形及畸变率更小,仿真结果更理想。仿真步长的降低在一定程度上能够获得更理想的仿真效果,但考虑到风电机组控制器的开关频率为3 kHz,仿真形成的差异也受其他因素影响。

3.3 接口延时对比分析

图6 CPU仿真不同步长电流频谱图

表2 CPU仿真电流总谐波畸变率 %

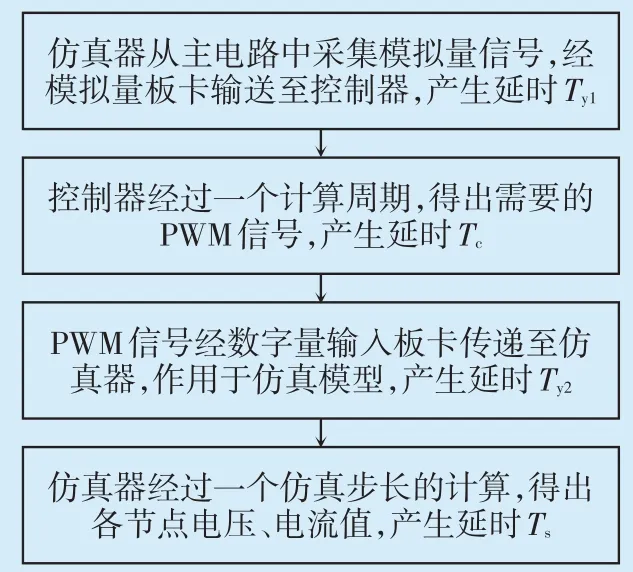

CPU仿真模型与控制器的数据交互需经过数据接口模块的处理,一个控制周期需要经过模拟量输出处理和数字量输入处理两次延时,而FPGA仿真器直接通过底层文件进行数据访问,减少了数据转换的时间。通过自回路的方式进行对应不同仿真方式的接口延时测试,利用信号发生器分别向不同仿真模型输入数字信号,经模型处理后输出模拟量信号,测量输入输出波形的延时,以模拟不同仿真模型之间的接口延时。表4为不同模型在不同仿真步长下的接口延时,CPU模型在不同仿真步长下产生的接口延时是一个波动值,CPU+FPGA模型的延时为固定值,对于风机控制器而言,一个控制指令流程如图8所示。由图8可见,忽略控制器计算的时间Tc,一个控制指令产生的延时:

结合表4可以看出,CPU仿真延时与仿真步长Ts有关,其值在Ts~2Ts波动;CPU+FPGA仿真延时可分为两部分,固有延时Ty1+Ty2和仿真步长Ts,其中固有延时为2μs。对于不同的仿真模型,在信号传输的过程中均会产生延时,且与仿真步长相关。考虑到CPU+FPGA仿真的步长更小和接口的访问方式,其仿真精准度更高。

图7 CPU+FPGA仿真电流曲线

表3 CPU+FPGA仿真电流总谐波畸变率 %

表4 接口延时 μs

图8 控制指令流程

4 结论

本文基于RT-LAB仿真平台,分别搭建了永磁直驱风电机组的CPU仿真模型和CPU+FPGA仿真模型,研究了模型和解算算法的差异,从多角度对比了不同仿真器、仿真步长间的仿真结果差异并测量了产生的接口延时,得出结论如下:

(1)对于CPU模型而言,可通过引入SSN和TSB降低仿真规模和步长以提高仿真精度,但当仿真步长足够精细时,进一步减少步长并不能够改善仿真结果。

(2)定量研究了仿真接口延时与仿真器、仿真步长间关系,其中CPU仿真延时在Ts~2Ts波动,CPU+FPGA仿真延时可分为固有延时2μs和仿真步长Ts,得出CPU+FPGA仿真产生的接口延时更小且恒定的结论。

(3)对于开关频率较低的永磁直驱风电机组,可运用CPU模型进行仿真,但CPU+FPGA模型的仿真结果更理想。